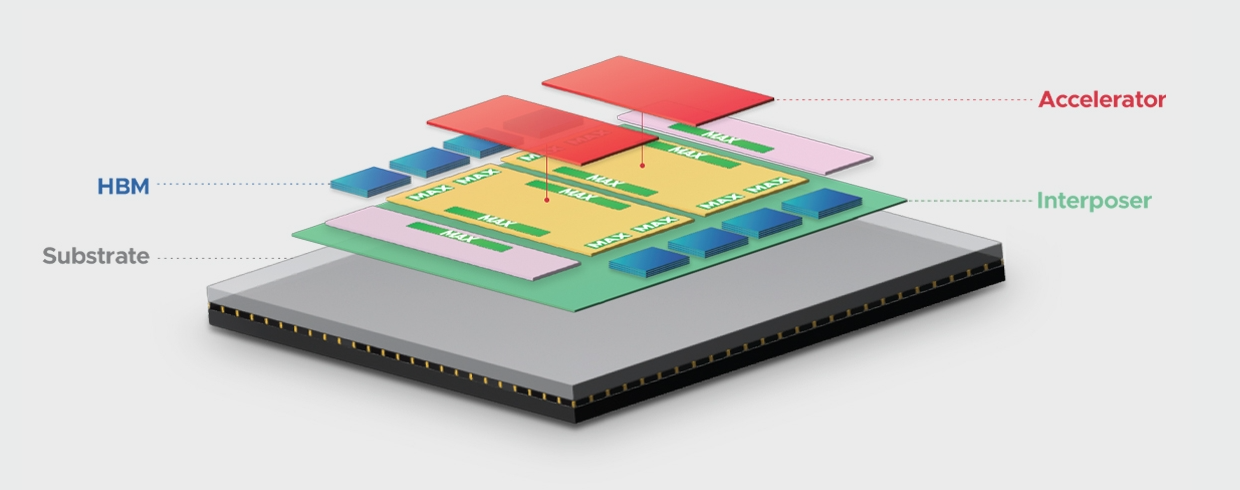

電子發(fā)燒友網(wǎng)報道(文/梁浩斌)博通最近推出了3.5D XDSiP的芯片封裝平臺技術(shù),面向下一代高性能AI、HPC應(yīng)用的定制XPU和ASIC。3.5D XDSiP的最大亮點,在于可以將超過6000平方毫米的3D堆疊硅晶片和12個HBM模塊集成到一個系統(tǒng)級封裝中。這是什么概念?

目前手機移動端的旗艦處理器驍龍8Elite核心面積是124.1平方毫米;英偉達H200核心面積1526平方毫米;今年英偉達推出的首款Blackwell架構(gòu)GPU B200,采用雙die合封,核心面積也達到1600平方毫米左右。也就是說博通的3.5D XDSiP平臺,可以支持近4個B200核心集成在一個封裝中。

那么這么“巨大”的芯片是怎么封裝的,市場上真的需要這么大規(guī)模的芯片嗎?

2.5D封裝、3D堆棧、F2F堆疊結(jié)合,首批產(chǎn)品2026上市

圖源:博通

隨著摩爾定律的進一步減緩,先進封裝在大規(guī)模計算集群中XPU上的應(yīng)用已經(jīng)成為了業(yè)界共識,在AI計算中,XPU需要計算、內(nèi)存、I/O等功能的復(fù)雜集成,以最大限度地降低功耗和成本。

而博通的3.5D XDSiP平臺,作為用于定制計算芯片的平臺,優(yōu)勢主要包括:

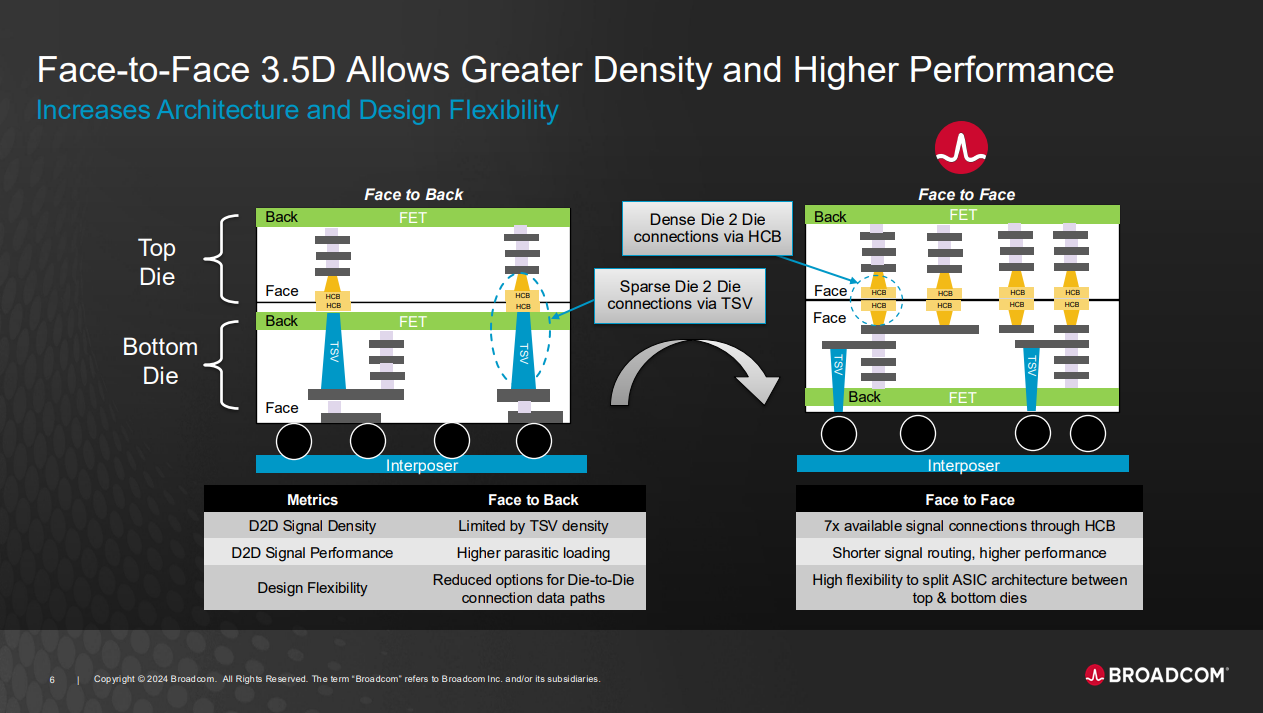

圖源:博通

增強的互連密度:與傳統(tǒng)采用硅通孔TVS的F2B(面到背)的技術(shù)相比,3.5D XDSiP采用HCB(混合銅鍵合)以F2F(面對面)的方式將邏輯芯片堆疊,堆疊芯片之間的信號密度提高了7倍;

高能效:通過利用3D HCB代替平面芯片到芯片物理接口,芯片到芯片接口的功耗降低了90%;

低延遲:最大限度地減少3D堆棧中計算、內(nèi)存和I/O組件之間的延遲;

小尺寸:支持更小的轉(zhuǎn)接板和封裝尺寸,從而節(jié)省成本并改善封裝翹曲。

這項封裝技術(shù)是博通與臺積電多年合作的成果,博通ASIC產(chǎn)品部高級副總裁兼總經(jīng)理Frank Ostojic表示:“隨著我們達到摩爾定律的極限,先進封裝對于下一代XPU集群至關(guān)重要。通過與我們的客戶密切合作,我們在臺積電和EDA合作伙伴的技術(shù)和工具基礎(chǔ)上創(chuàng)建了一個3.5D XDSiP平臺。通過垂直堆疊芯片組件,Broadcom的3.5D平臺使芯片設(shè)計師能夠為每個組件配對正確的制造工藝,同時縮小插入器和封裝尺寸,從而顯著提高性能、效率和成本。”

臺積電業(yè)務(wù)發(fā)展高級副總裁張曉強博士表示,臺積電和博通在過去幾年中密切合作,將臺積電最先進的邏輯處理和3D芯片堆疊技術(shù)與博通的設(shè)計專業(yè)知識結(jié)合在一起。

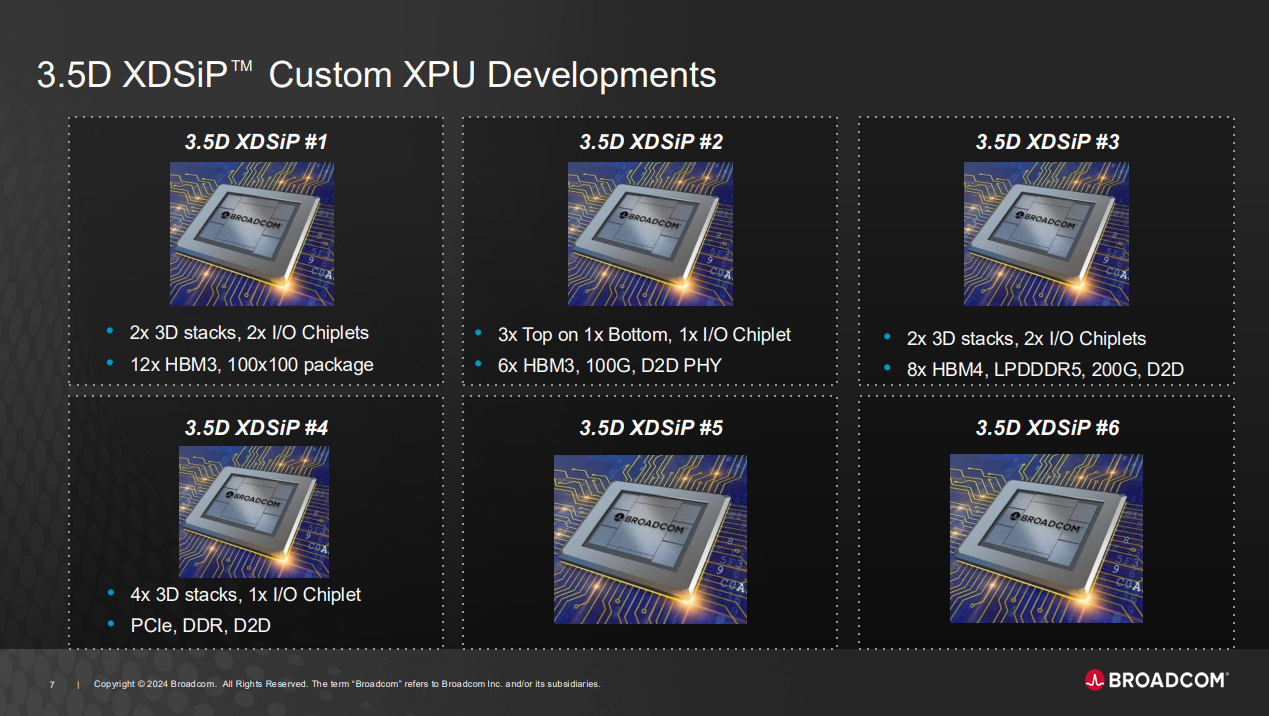

圖源:博通

博通表示,3.5D XDSiP技術(shù)目前已經(jīng)被主要的AI領(lǐng)域客戶使用,已經(jīng)有6款產(chǎn)品正在開發(fā)中。其中富士通下一代2nm制程的Arm處理器FUJITSU-MONAKA已經(jīng)確認使用博通3.5D XDSiP技術(shù),這款處理器面向數(shù)據(jù)中心、邊緣計算等應(yīng)用,據(jù)此前富士通的介紹,MONAKA每顆CPU包含一個中央的I/O die和四個3D垂直堆疊die,并集成SRAM,預(yù)計2027年出貨。

使用3.5D XDSiP技術(shù)的芯片產(chǎn)品,博通預(yù)計最早在2026年2月實現(xiàn)出貨。

小結(jié):

先進封裝作為未來AI計算芯片的重要部分,博通這種大面積的芯片封裝方案,能夠極大程度上提高系統(tǒng)集成度,同時通過創(chuàng)新的互連方案,提高片內(nèi)互連的帶寬和提高能效,有望成為未來高性能處理器的一個重要方向。

-

博通

+關(guān)注

關(guān)注

35文章

4336瀏覽量

107681

發(fā)布評論請先 登錄

如何用一顆SOP8芯片實現(xiàn)色溫+亮度精準控制?

先進封裝技術(shù):3.5D封裝、AMD、AI訓練降本

用一顆TXB0104可以進行串口電壓轉(zhuǎn)換嗎?

3.5D封裝來了(下)

用一顆5G的204B接口DA芯片,DA芯片的輸入時鐘大小和輸入數(shù)據(jù)的速率是怎么樣的關(guān)系?

博通股價躍升 或因蘋果與博通合作開發(fā)人工智能芯片的利好刺激

一顆射頻開關(guān)的獨白

一文理解2.5D和3D封裝技術(shù)

什么是3.5D封裝?它有哪些優(yōu)勢?

一顆芯片面積頂4顆H200,博通推出3.5D XDSiP封裝平臺

一顆芯片面積頂4顆H200,博通推出3.5D XDSiP封裝平臺

評論