來源:悅智網 ,作者羅拯東、韓根全等

功率半導體器件作為高效電能控制和轉換裝置的核心器件,從其誕生之初,便作為電力電子技術的“幕后英雄”持續推動人類社會蓬勃發展。從個人電腦到數據中心,從電動汽車到鐵路運輸,再到日益成長的風電、光伏等新興能源產業,功率半導體在電力生產、傳輸、儲能和日常應用全鏈條發揮著重要作用。

近年來,隨著全球氣候變化和能源價格增長,能源利用效率正成為電子設備更新迭代的關鍵指標,主導電子設備電能轉換的高性能功率器件也因此愈發受到社會關注。據預測,未來全球80%的電能都將經由以功率半導體為基礎的電力電子設備進行處理,先進功率半導體技術因此成為各國競相發展的關鍵戰略方向之一。

隨著中國在雙碳戰略、能源電子等相關領域的持續投入,功率半導體產業在國內已進入實質性快速發展階段。在推動現有硅基、碳化硅基功率器件技術國產替代之外,布局先進技術自主創新已成為我國功率半導體進一步發展的重要方向和搶占未來國際市場的重要策略。功率半導體發展主要圍繞器件工藝、集成和材料迭代升級這一主線,其中半導體材料的革新對于行業具有顛覆性影響。以碳化硅、氮化鎵、氧化鎵為代表的(超)寬禁帶半導體相比于傳統硅材料在開關效率、尺寸、頻率等功率器件關鍵性能指標上優勢明顯;其中,氧化鎵具有能帶更寬、耐壓更強、功耗更低等優勢,有望推動功率器件變革和升級換代。基于技術成熟度和潛在成本優勢,業界普遍認為氧化鎵是最有希望快速實現產業化的超寬禁帶半導體材料,全球主要研究機構以及龍頭半導體企業已開始提前布局氧化鎵功率半導體技術。特別地,美國等國家近年來相繼對氧化鎵相關技術進行出口管制;我國也在政策上高度重視氧化鎵技術,將其列入“十四五”國家重點研發計劃、中國工程院戰略性新材料以及多省市重點產業規劃。發展氧化鎵相關技術,對于我國在功率半導體技術上取得國際領先具有重要意義,也是我國通過自主創新引領未來功率半導體產業的重要戰略機遇。

氧化鎵功率半導體的優勢與局限

相較于傳統硅材料以及碳化硅、氮化鎵等寬禁帶半導體,基于氧化鎵的功率半導體器件在高壓、體積、功耗等關鍵器件指標方面優勢突出。在電學特性方面,憑借其超寬帶隙特性(4.8 ~5.1 eV),氧化鎵的擊穿場強理論上可以達到8 MV/cm,是硅的20倍以上,氮化鎵的2.5倍、碳化硅的3倍多;同時,氧化鎵功率器件品質因子(如直流低損耗Baliga品質因子等)明顯優于碳化硅、氮化鎵等。因此,在功率器件上使用氧化鎵可顯著提升器件輸出電流密度和功率密度,有望推動下一代高壓大功率電子設備的快速發展。在材料制備方面,氧化鎵單晶可基于相對簡單的技術合成,其缺陷密度相較碳化硅晶圓低至少3個數量級,可有效提升后續產品良率。同時,大尺寸氧化鎵晶圓制備技術正在快速發展,目前國際上已突破6英寸晶圓尺寸,低成本、大尺寸晶圓技術有望成為氧化鎵行業爆發拐點。

盡管氧化鎵半導體優勢突出,但其應用于功率器件仍面臨材料熱導率偏低的難題,嚴重制約了氧化鎵功率器件工作性能。具體而言,相比于常見于功率器件中的硅和碳化硅半導體,氧化鎵的熱導率僅為硅的20%、碳化硅的10%。低熱導率使得氧化鎵器件工作時產生的熱量無法從襯底得到有效耗散,從而導致器件結溫急劇上升、性能嚴重退化。因此,低熱導率已成為制約氧化鎵在功率器件應用方面的最大瓶頸之一,也是國內外氧化鎵技術研究攻關的核心方向。

探索更具發展前景的氧化鎵襯底散熱技術

氧化鎵材料自身存在劇烈的聲子-聲子散射,導致其熱導率較低。在不改變其物理性質的前提下,將氧化鎵薄膜與其他高導熱襯底集成是提升器件散熱性能的有效方法。在這方面,過往研究主要基于兩條技術路線:一是在高導熱襯底上進行氧化鎵薄膜異質外延生長,然而異質外延受限于襯底晶格適配度,通常難以實現高質量薄膜,進而影響器件性能;二是將氧化鎵襯底進行減薄后與其他襯底集成,但機械減薄過程難以精確控制、容易造成襯底損壞,且其界面質量較差,使得氧化鎵界面熱阻過高,無法有效提高器件散熱。

在多項國家科研計劃的支持下,西安電子科技大學郝躍、韓根全研究團隊(以下簡稱“團隊”)與合作者們深入探索氧化鎵半導體器件散熱的關鍵科學問題,基于離子注入-鍵合剝離技術提出氧化鎵異質集成襯底新工藝,并在氧化鎵晶圓制備和高性能功率器件全流程工藝上取得重要進展。

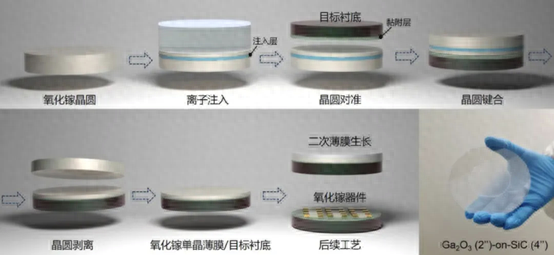

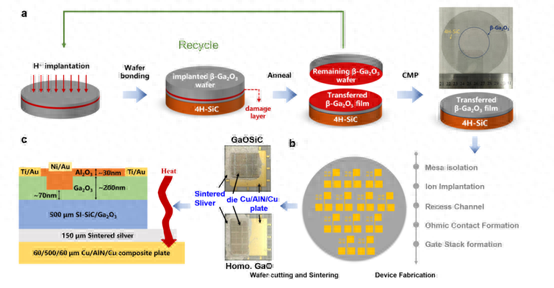

以“氧化鎵薄膜-高導熱襯底”異質集成為出發點,團隊結合氧化鎵單晶材料特性,大幅改進傳統離子注入-鍵合剝離技術,在離子注入劑量、鍵合方法以及剝離溫度等關鍵參數方面進行協同優化,成功開發出一套專用于氧化鎵單晶晶圓的互補金屬氧化物半導體(CMOS)工藝兼容的智能剝離技術。該技術方案工藝流程大致包括:首先對原始氧化鎵單晶晶圓進行H+離子注入,通過調節工藝參數在氧化鎵內部產生深度可控、易于剝離的離子注入層,之后進行目標襯底(如碳化硅、硅等)與氧化鎵晶圓對準和直接鍵合,使得氧化鎵表面薄膜與目標襯底牢固結合;經上述工序得到穩固鍵合后的“氧化鎵-目標襯底”晶圓對,隨后再進行特殊工藝處理,使得氧化鎵薄膜沿著H+離子注入層解離,即可將所需氧化鎵單晶薄膜從氧化鎵晶圓上剝離,實現“氧化鎵-目標襯底”晶圓級異質集成。除了可實現氧化鎵薄膜與高導熱襯底集成這一重要目標以外,該技術在襯底材料不受晶格匹配限制、被剝離氧化鎵晶圓可循環使用方面具有獨特優勢,可進一步發展更為復雜的高質量氧化鎵薄膜結構和降低氧化鎵使用成本。

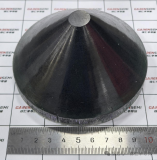

基于該技術,團隊首次在國際上基于碳化硅和硅襯底創新制備了大尺寸、高導熱氧化鎵異質集成晶圓(見圖1),目前已成功實現2寸和4寸氧化鎵異質集成晶圓。經系統表征,異質集成氧化鎵薄膜晶體質量、電導率與氧化鎵單晶襯底相當,薄膜轉移率高于95%、厚度不均勻性小于2%、表面粗糙度低于0.2納米,材料整體散熱性能遠優于同期報道的同質外延氧化鎵薄膜,且接近于襯底材料(如碳化硅)的散熱水平。通過選取合適的氧化鎵單晶薄膜厚度,可在異質集成晶圓上基于氧化鎵薄膜直接進行晶體管器件制備,無需再一次進行功能層薄膜外延。另一方面,基于異質集成襯底的單晶氧化鎵模板層,也可以進行晶格相似材料的高質量薄膜二次外延,從而制備更為復雜的器件結構。

圖1:氧化鎵異質集成晶圓制備流程圖與氧化鎵(2英寸)/碳化硅(4英寸)異質集成晶圓照片

基于異質集成晶圓實現高性能功率器件

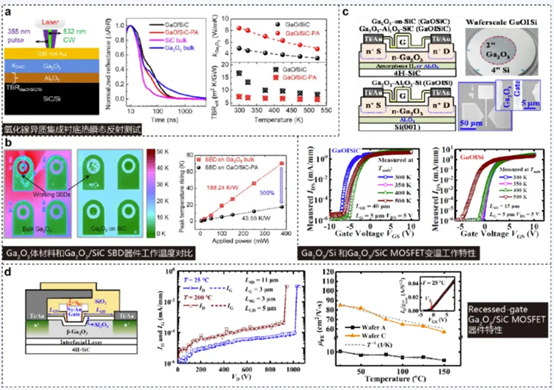

團隊針對氧化鎵異質集成晶圓進行了詳細的散熱性能測試與評估。通過瞬態熱反射測試并結合有限元模型擬合測試曲線,可提取氧化鎵異質集成晶圓熱導率和界面熱阻等關鍵信息,如圖2a所示。通過對比氧化鎵/碳化硅異質集成晶圓和氧化鎵晶圓的導熱參數,可以得出結論:氧化鎵/碳化硅異質集成晶圓的熱擴散速率幾乎與碳化硅襯底相當,遠高于氧化鎵體材料。同時,通過理論分析,團隊發現經過特殊工藝界面處理的氧化鎵異質集成薄膜導熱機制由常規的聲子-缺陷散射轉變為本征聲子-聲子散射,大幅提高了異質集成結構的散熱性能。為了驗證異質集成晶圓的散熱效果,團隊對氧化鎵肖特基二極管(SBD)進行了表面工作溫度紅外測試。從圖2b可以看出,基于氧化鎵/碳化硅異質集成結構的器件工作時表面溫度變化很小,且呈現均勻的溫度分布。相比之下,在相同偏置功率的情況下,氧化鎵體材料SBD器件表面最高工作溫度是異質集成器件的400%,證明氧化鎵異質集成結構對于器件散熱性能具有顯著提升效果。

功率晶體管是氧化鎵未來應用的主要器件形式,團隊基于異質集成結構開發了高導熱氧化鎵異質集成晶體管制備工藝,實現了增強型與耗盡型器件。經測試,器件展現出優異的溫度穩定性,高溫可靠性遠高于傳統氧化鎵體材料同質外延晶體管。如圖2c所示,在測試溫度由室溫升高到500 K的情況下,實驗結果表明基于硅和碳化硅襯底的高導熱氧化鎵異質集成晶體管在開態、關態電流以及電流開關比上幾乎沒有變化;相比之下,同期報道顯示基于氧化鎵單晶襯底的同質外延氧化鎵晶體管通常在測試溫度升高到400 K左右時即出現明顯的性能退化,其電流開關比對比室溫結果甚至降低近5個數量級,使得器件在高溫下工作失效。進一步地,團隊基于Ga?O?/SiC異質集成晶圓開發Recessed-gate晶體管器件,成功實現上千伏擊穿電壓與高遷移率。受益于異質集成晶圓的獨特特性,以上高性能器件在200℃高溫環境下僅顯示出微弱的性能退化,見圖2d。團隊的這項工作有力證明了基于高導熱異質集成襯底的氧化鎵晶體管可有效克服因強烈自熱效應導致的晶體管器件性能退化問題,為高性能氧化鎵晶體管提供了一種可行的解決方案,對推動氧化鎵功率半導體技術的應用有積極作用。

圖2:氧化鎵異質集成結構助推器件散熱:(a)針對氧化鎵異質集成晶圓的熱瞬態反射測試;(b)氧化鎵/碳化硅與氧化鎵體材料SBD器件表面溫度對比;(c)基于氧化鎵異質集成結構的晶體管器件變溫電學特性;(d)Recessed-gate晶體管的電學特性。(圖片來源:Ga203/SiCACS Appl. Electron Mater.,2022,4:494-502;Fundamental Res.,2021,1:691-696;IEEEInternational Electron Devices Meeting (lEDM),2019.12.5.1-12.5.4:lEEE Trans. ElectronDevices,2022,69,1945;lEEE Trans. ElectronDevices,2021.68:1188)

未來,功率半導體將繼續深刻影響世界電力電子系統,相關變革性技術的出現將快速推動能源電子新一輪創新發展。團隊將繼續瞄準國家重大需求以及國際功率半導體技術前沿方向,基于異質集成晶圓技術,力爭推動我國氧化鎵半導體材料、器件、下游應用相關技術的自主可控發展,為能源電子、雙碳戰略等重點領域提供更多助力。

【近期會議】

10月30-31日,由寬禁帶半導體國家工程研究中心主辦的“化合物半導體先進技術及應用大會”將首次與大家在江蘇·常州相見,邀您齊聚常州新城希爾頓酒店,解耦產業鏈市場布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二屆半導體先進封測產業技術創新大會”將再次與各位相見于廈門,秉承“延續去年,創新今年”的思想,仍將由云天半導體與廈門大學聯合主辦,雅時國際商訊承辦,邀您齊聚廈門·海滄融信華邑酒店共探行業發展!誠邀您報名參會:https://w.lwc.cn/s/n6FFne

聲明:本網站部分文章轉載自網絡,轉發僅為更大范圍傳播。 轉載文章版權歸原作者所有,如有異議,請聯系我們修改或刪除。聯系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

氧化鎵

+關注

關注

5文章

82瀏覽量

10556 -

功率半導體器件

+關注

關注

3文章

52瀏覽量

6263 -

異質集成

+關注

關注

1文章

6瀏覽量

783

發布評論請先 登錄

從清華大學到鎵未來科技,張大江先生在半導體功率器件十八年的堅守!

氧化鎵器件的研究現狀和應用前景

第四代半導體新進展:4英寸氧化鎵單晶導電型摻雜

ACS AMI:通過襯底集成和器件封裝協同設計實現具有極低器件熱阻的氧化鎵MOSFETs

意法半導體下一代汽車微控制器的戰略部署

集成之巔,易用至極!納微發布全新GaNSlim?氮化鎵功率芯片

異質集成氧化鎵:下一代高性能功率半導體器件的新基石

異質集成氧化鎵:下一代高性能功率半導體器件的新基石

評論