CadenceLIVE China 2024 中國用戶大會(huì),作為目前中國 EDA 行業(yè)覆蓋技術(shù)領(lǐng)域全面、規(guī)模巨大的先進(jìn)技術(shù)交流平臺(tái),迎來其輝煌的第二十屆盛會(huì)。此次大會(huì)定于8 月 27 日在上海浦東嘉里大酒店盛大啟幕,本次是在中國舉辦的第二十屆大會(huì),眾多亮點(diǎn)值得關(guān)注,現(xiàn)場參會(huì)注冊(cè)現(xiàn)已開放,誠邀您前來參會(huì)。

大會(huì)專題和亮點(diǎn)將陸續(xù)揭曉,并在文末特別奉上“拼手速贏好禮 CadenceLIVE 2024 主題大揭秘游戲”,拼手速、拿獎(jiǎng)品,驚喜多多,快向下翻閱查看吧!

▼▼▼

今日專題揭曉:

PCB、封裝設(shè)計(jì)及系統(tǒng)級(jí)仿真專場

無論你是公司硬件設(shè)計(jì)平臺(tái)的高級(jí)架構(gòu)師還是硬件開發(fā)人員,或者是負(fù)責(zé)高速電路設(shè)計(jì)與仿真專家,亦或是負(fù)責(zé)芯片設(shè)計(jì)和熱管理、熱分析的專職工程師,您都將在本專題瀏覽到 Cadence 最新的系統(tǒng)設(shè)計(jì)與仿真技術(shù)方案。

在本專題論壇上,來自 Cadence 總部的研發(fā)專家將介紹 Allegro 硬件設(shè)計(jì)平臺(tái)最新的開發(fā)進(jìn)展、遠(yuǎn)景路標(biāo),尤其是集成了人工智能技術(shù)的下一代 Allegro XAI 平臺(tái),作為一款顛覆性的生產(chǎn)力工具,該平臺(tái)將改變傳統(tǒng)的、低效的基于人工的硬件布局布線流程,通過借助 AI 技術(shù),極大地提高硬件開發(fā)的效率。

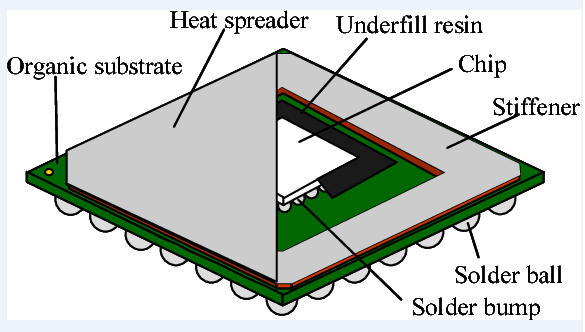

在 AI 時(shí)代,大算力、低延時(shí)成為硬件設(shè)計(jì)的主題詞。仿真技術(shù),尤其是高速信號(hào)完整性、電-熱完整性、應(yīng)力完整性,越來越成為一款大算力、高帶寬、高功耗芯片產(chǎn)品成功與否的關(guān)鍵。同樣來自 Cadence 總部的多物理場仿真產(chǎn)品線的研發(fā)專家,將為您帶來最新的Sigrity、Clarity、Celsius 等產(chǎn)品開發(fā)進(jìn)展,尤其是在3DIC、射頻(RF)電路設(shè)計(jì)、熱和應(yīng)力、人工智能技術(shù)應(yīng)用等領(lǐng)域的持續(xù)投入及相關(guān)產(chǎn)品,從中您將了解 Cadence 在多物理場仿真領(lǐng)域的戰(zhàn)略布局和遠(yuǎn)景規(guī)劃。

同時(shí),本專題論壇同樣邀請(qǐng)了來自業(yè)內(nèi)的頂級(jí)專家分享他們基于 Cadence 方案的成功經(jīng)驗(yàn),包括來自Schneider的數(shù)字孿生架構(gòu)實(shí)施方案;來自 ZTE、NIO 和 Inventec 的仿真專家分享了在服務(wù)器和智能自動(dòng)駕駛產(chǎn)品上應(yīng)用電-熱多物理仿真分析解決高功耗產(chǎn)品電源完整性、信號(hào)完整性簽核的問題;來自中興微電子和一博科技的仿真專家分享了他們利用 Optimality 技術(shù),自動(dòng)地優(yōu)化主流高速接口比如 112G,SerDes,DDR5 等的信號(hào)完整性指標(biāo),大大加快了設(shè)計(jì)效率。歡迎對(duì)相關(guān)技術(shù)感興趣的業(yè)內(nèi)技術(shù)人員和專家報(bào)名參加 CadenceLIVE China 2024 年度用戶分享大會(huì),并利用互動(dòng)環(huán)節(jié)與現(xiàn)場研發(fā)和同行進(jìn)行充分互動(dòng)交流。

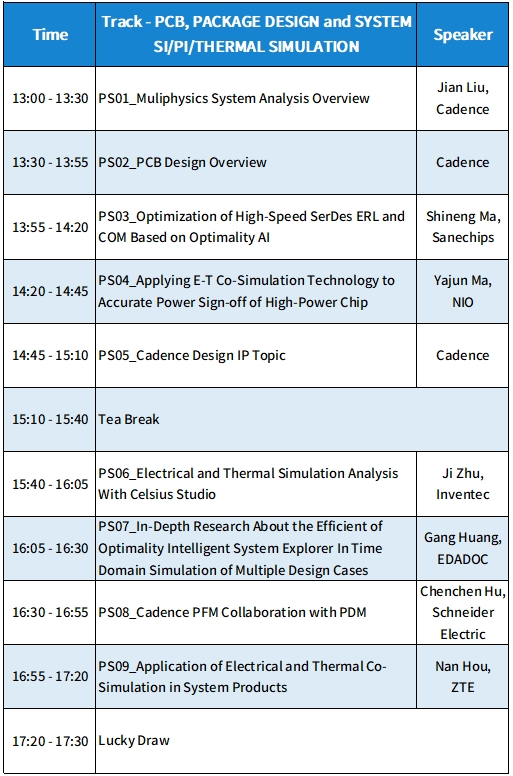

專題議程

*日程以最終現(xiàn)場公布為準(zhǔn)

-

pcb

+關(guān)注

關(guān)注

4367文章

23485瀏覽量

409519 -

Cadence

+關(guān)注

關(guān)注

67文章

973瀏覽量

144360 -

封裝設(shè)計(jì)

+關(guān)注

關(guān)注

2文章

47瀏覽量

12066 -

系統(tǒng)仿真

+關(guān)注

關(guān)注

0文章

20瀏覽量

4730

發(fā)布評(píng)論請(qǐng)先 登錄

MUN12AD03-SEC的封裝設(shè)計(jì)對(duì)散熱有何影響?

封裝設(shè)計(jì)圖紙的基本概念和類型

如何通俗理解芯片封裝設(shè)計(jì)

集成電路封裝設(shè)計(jì)為什么需要Design Rule

芯片封裝需要進(jìn)行哪些仿真?

封裝工藝簡介及元器件級(jí)封裝設(shè)備有哪些

NVIDIA即將亮相ROSCon China 2024

行芯精彩亮相IC CHINA 2024

楷領(lǐng)科技邀您相約IC CHINA 2024

開始報(bào)名!PCB/封裝設(shè)計(jì)及系統(tǒng) SI/PI/Thermal 仿真專場研討會(huì)——2024 Cadence 中國技術(shù)巡回研討會(huì)

2024 KiCon Asia KiCad 用戶大會(huì)

新技術(shù)丨廣電計(jì)量成功開發(fā)系統(tǒng)級(jí)電磁脈沖防護(hù)仿真技術(shù)

CadenceLIVE China 2024丨PCB、封裝設(shè)計(jì)及系統(tǒng)級(jí)仿真專題揭曉

CadenceLIVE China 2024丨PCB、封裝設(shè)計(jì)及系統(tǒng)級(jí)仿真專題揭曉

評(píng)論