電子發燒友網報道(文/李寧遠)提及芯片制造,首先想到的自然是光刻機和光刻技術。而眾所周知,EUV光刻機產能有限而且成本高昂,業界一直都在探索不完全依賴于EUV光刻機來生產高端芯片的技術和工藝。納米壓印光刻技術NIL在這條賽道上備受關注,是最有機會率先應用落地的技術路線。

今年早些時候,根據英國金融時報的報道,負責監督新型光刻機開發的佳能高管武石洋明在接受采訪時稱,采用納米壓印技術的佳能光刻設備FPA-1200NZ2C目標最快在今年開始交付,這一設備的交付將為小型半導體制造商生產先進芯片開辟了一條新的途徑。

與此同時,3月5日美光科技公司在一場舉辦的演講中表示,將率先支持佳能的納米壓印技術,從而進一步降低生產DRAM存儲芯片的單層成本。

從存儲芯片開始,納米壓印攪動芯片制造格局

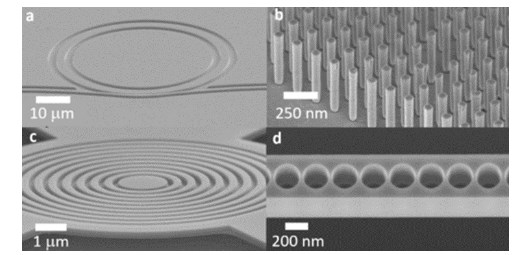

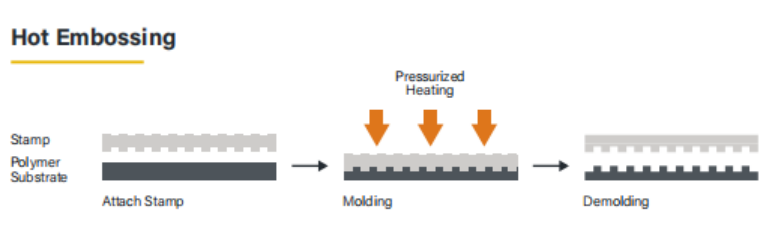

納米壓印,一種新型的微納加工技術。納米壓印技術通過光刻膠輔助,將模板上的微納結構轉移到待加工材料上的技術,其最早在20世紀90年代中期由華裔科學家周郁發明。單從EUV光刻技術原理來看,想要實現更高的分辨率,無外乎從三個層面著手。一是選用更小波長的光源,二是通過界面材料提高數值孔徑NA值,三是獲取更低的工藝因子,其中主要的實現手段是縮短光源波長。

但是光學光刻是存在分辨率極限的,縮小波長的每一次實現都伴隨技術難度和成本倍增,所以EUV光刻機不僅產能有限而且成本極其高昂。而納米壓印的加工過程不使用可見光或紫外光加工圖案,而是使用機械手段進行圖案轉移,所以能實現的分辨率完全不會受到光學光刻最短曝光波長的物理限制,也不會像EUV需要如此高昂的成本。

在美光科技公司近期的演講中,也提到了DRAM節點和沉浸式光刻分辨率的問題,“Chop層數量不斷增加,這就意味著添加更多的曝光步驟,來取出密集存儲器陣列外圍的dummy structures。”在光學系統下,受限于技術本身的限制,DRAM層圖案已經很難用光刻技術來進行印刷。

“納米打印方式可以用更精細的方式打印出來,且鑒于納米壓印技術應用成本是沉浸式光刻技術的五分之一,因此是非常不錯的解決方案”,美光科技公司坦言。納米壓印分辨率只與模板圖案的尺寸相關,已經能做到高于傳統光刻的分辨率。

雖然生產速度上會慢上一些,但是用于壓印的模板可以反復使用,大大降低了加工成本也方便進行量產。因此美光計劃率先支持佳能的納米壓印技術,從而進一步降低生產DRAM存儲芯片的單層成本。

存儲芯片,的確是目前最契合納米壓印技術的。存儲廠商在芯片制造上會更偏重對成本的把控,會放寬對缺陷的要求給予一定的設計余量,可以承受一定的缺陷只要不影響成品率就行。佳能規劃的納米壓印設備路線圖也是從3D NAND存儲芯片開始,逐漸過渡到DRAM,最終實現CPU等邏輯芯片的制造。

凱俠與佳能在納米壓印上的合作也已有多年,SK海力士也從Canon引進納米壓印設備計劃在2025年左右使用該設備開始量產3D NAND閃存。三星同樣開發了包括納米壓印技術在內多種方案以解決多圖案工藝導致的成本上升問題。

佳能社長御手洗富士夫也曾在去年表示,納米壓印光刻技術面世為半導體制造商生產先進芯片開辟了一條新的途徑。

隨著佳能光刻設備最快今年開始交付,存儲芯片與納米壓印技術相結合,該技術能否降低存儲廠商對芯片代工廠的依賴,能否在存儲芯片的批量生產上大幅提高效率并降低成本,這一問題的答案最早在今年就能看到。

降低芯片制造成本,納米壓印給國產先進芯片發展帶來新思路

此前佳能公布FPA-1200NZ2C納米壓印光刻半導體設備社長御手洗富士夫表示,納米壓印光刻半導體設備比ASML的EUV少1位數,而且這種機器所需功率只有EUV同類產品的十分之一。

從目前公布的進展看,FPA-1200NZ2C已經能夠勝任5nm節點芯片的制造。此前還有佳能高管表示只需要不斷改進掩模,FPA-1200NZ2C甚至能生產2nm芯片。

除了制程節點上的適配,據日經中文網報道,納米壓印能與極紫外光刻相比能將該工序的制造成本降低四成,耗電量降低九成。佳能此前公布的研究結果中,納米壓印光刻在吞吐量為80片時相對ArF光刻工藝可降低28%的成本,隨著吞吐量增加成本降低幅度可達到50%以上。

雖然納米壓印技術不會也不可能完全取代EUV,但是它如果能成功應用,將打開芯片先進制程制造的新思路。

眾所周知,目前我國半導體產業正受到多方圍堵,國內半導體制造商獲取先進半導體制造設備受到了不小的限制,尤其是在先進制程上。不例外的是佳能的納米壓印設備同樣是限制出口的,日本的出口管制清單中就有“可實現45nm以下線寬的壓印光刻裝置”。

當前,納米壓印市場正在逐漸壯大,TechNavio數據顯示,2026年納米壓印市場有望達到33億美元,年復合增長率可達17.74%。已有不少國內廠商和科研機構在納米壓印賽道上布局,如青島天仁微納、蘇州蘇大維格、美迪凱、水晶光電、炬光科技、蘇州光舵微納、昇印光電、新維度微納、歌爾股份等,助力國內半導體制造進一步突破。

在納米壓印市場打磨多年的天仁微納已經在微納光學市場占據了技術和市場領先地位,現在除了繼續迭代納米壓印光刻在晶圓級光學加工領域的拓展,還在持續加碼拓展納米壓印在半導體集成電路、平板顯示、生物芯片等其他領域的應用,助力國產納米壓印設備打破進口壟斷。

不久前炬光科技成功并購瑞士SMO,SMO擁有納米壓印精密微納光學設計與加工制造技術,即結合微納光學設計目標進行母版的設計與制造,在8英寸晶圓基板上進行精密壓印,8英寸晶圓處于成熟量產階段。

光舵微納經過多年的研發及市場應用推廣,已制造出多款研發型納米壓印設備及全自動量產型納米壓印設備,在LED圖形化襯底產業實現了對尼康光刻機的產業化替代。目前也在積極拓展納米壓印技術在高端半導體領域的產業化應用。

如果納米壓印設備在實際量產中真的取得了如預期中的效果,這對國內納米壓印行業無疑將是一針強心劑,也將為國內先進芯片制造發展帶來新的思路。

小結

隨著半導體行業的快速發展,芯片越來越緊湊集成度越來越高,對芯片制造技術提出了越來越高的要求,行業渴求更低成本的制造技術。納米壓印能否如預期中掀起先進制程芯片制造的革命,不久之后就能在存儲領域見分曉。

-

光刻技術

+關注

關注

1文章

150瀏覽量

16110

發布評論請先 登錄

納米壓印光刻技術應用在即,能否掀起芯片制造革命?

納米壓印光刻技術應用在即,能否掀起芯片制造革命?

評論