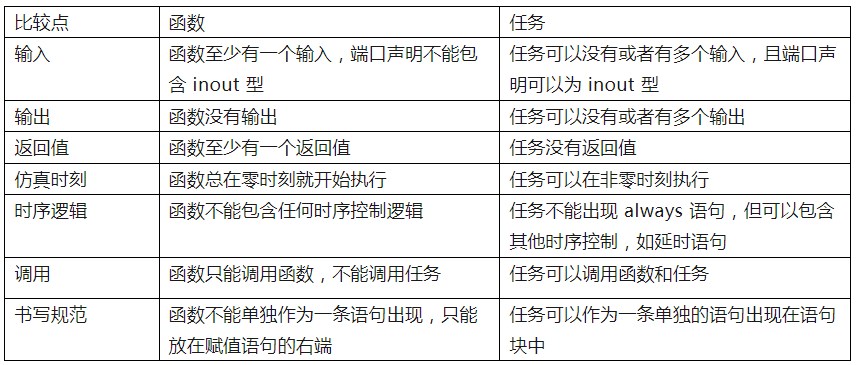

在verilog中,函數(shù)和任務(wù)均用來描述共同的代碼段,并且在模式內(nèi)任意位置被調(diào)用,提高代碼效率,讓代碼更加的直觀,提高代碼可讀性。但是在實(shí)際使用的過程中,函數(shù)和任務(wù)也存在諸多的不同,下面將對而這進(jìn)行對比,方便學(xué)習(xí)理解。

| 比較 | 函數(shù) | 任務(wù) |

|---|---|---|

| 輸入 | 函數(shù)至少需要包含一個輸入,端口類型不能包含inout類型 | 任務(wù)可以沒有或者有多個輸入,且端口聲明可以為inout類型 |

| 輸出 | 函數(shù)無輸出 | 任務(wù)可以沒有或者有多個輸出 |

| 返回值 | 函數(shù)有至少一個返回值 | 任務(wù)無返回值 |

| 仿真時間 | 函數(shù)從零時刻開始執(zhí)行 | 任務(wù)可以在非零時刻執(zhí)行 |

| 時序邏輯 | 函數(shù)不包含時序邏輯 | 任務(wù)不能出現(xiàn)always語句,但是可以使用延時之類的語句 |

| 調(diào)用 | 函數(shù)可以調(diào)用函數(shù)但是不能調(diào)用任務(wù) | 任務(wù)可以調(diào)用任務(wù)和函數(shù) |

| 語法規(guī)范 | 函數(shù)只能出現(xiàn)在賦值語句的右端 | 任務(wù)可以作為單獨(dú)的語句出現(xiàn) |

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111868 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4371瀏覽量

64228 -

任務(wù)

+關(guān)注

關(guān)注

1文章

20瀏覽量

8629

發(fā)布評論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

verilog模塊的調(diào)用、任務(wù)和函數(shù)

在做模塊劃分時,通常會出現(xiàn)這種情形,某個大的模塊中包含了一個或多個功能子模塊,verilog是通過模塊調(diào)用或稱為模塊實(shí)例化的方式來實(shí)現(xiàn)這些子模塊與高層模塊的連接的.

Verilog系統(tǒng)任務(wù)的相關(guān)資料推薦

Verilog數(shù)字系統(tǒng)設(shè)計十任務(wù)和函數(shù)實(shí)驗(yàn)2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計十前言一、Verilog系統(tǒng)

發(fā)表于 02-09 06:05

任務(wù)和函數(shù)的區(qū)別?

Verilog數(shù)字系統(tǒng)設(shè)計九任務(wù)和函數(shù)實(shí)驗(yàn)1文章目錄Verilog數(shù)字系統(tǒng)設(shè)計九前言一、任務(wù)和函數(shù)

發(fā)表于 02-09 07:47

FreeRTOS任務(wù)應(yīng)用函數(shù)介紹

* constpulTotalRunTime ); 該函數(shù)向TaskStatus_t結(jié)構(gòu)體填充相關(guān)信息,系統(tǒng)中每一個任務(wù)的信息都可以填充到TaskStatus_t結(jié)構(gòu)體數(shù)組中,數(shù)組大

Verilog HDL語言中任務(wù)與函數(shù)的比較

其中,返回值的類型和位寬是可選項(xiàng),如果缺省會返回一位寄存器類型數(shù)據(jù)。Verilog HDL認(rèn)為函數(shù)的定義隱式地聲明了與函數(shù)同名的寄存器。函數(shù)的定義把

Verilog數(shù)字系統(tǒng)設(shè)計——任務(wù)和函數(shù)二(系統(tǒng)任務(wù)readmemb或readmemh)

Verilog數(shù)字系統(tǒng)設(shè)計十任務(wù)和函數(shù)實(shí)驗(yàn)2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計十前言一、Verilog系統(tǒng)

發(fā)表于 12-05 19:06

?7次下載

Verilog數(shù)字系統(tǒng)設(shè)計——任務(wù)和函數(shù)一(斐波那契數(shù)列)

Verilog數(shù)字系統(tǒng)設(shè)計九任務(wù)和函數(shù)實(shí)驗(yàn)1文章目錄Verilog數(shù)字系統(tǒng)設(shè)計九前言一、任務(wù)和函數(shù)

發(fā)表于 12-05 19:06

?9次下載

Verilog設(shè)計中函數(shù)和任務(wù)的作用分析

任務(wù)和函數(shù)在Verilog中用于描述常用的功能行為。與其在不同的地方復(fù)制相同的代碼,不如根據(jù)需求使用函數(shù)或任務(wù),這是一種良好且常見的做法。為

Verilog系統(tǒng)函數(shù)和邊沿檢測

“ 本文主要分享了在Verilog設(shè)計過程中一些經(jīng)驗(yàn)與知識點(diǎn),主要包括Verilog仿真時常用的系統(tǒng)任務(wù)、雙向端口的使用(inout)、邊沿檢測”

RTL建模中的函數(shù)和任務(wù)討論

函數(shù)和任務(wù)可以在使用它們的模塊或接口中定義。定義可以出現(xiàn)在調(diào)用函數(shù)或任務(wù)的語句之前或之后完成,函數(shù)和任務(wù)

Verilog中關(guān)于文件操作的系統(tǒng)任務(wù)

Verilog提供了很多對文件操作的系統(tǒng)任務(wù)和函數(shù),例如打開關(guān)閉文件、向文件寫入值、從文件讀出值等等。

Verilog任務(wù)與函數(shù)的區(qū)別

和函數(shù)一樣,任務(wù)(task)可以用來描述共同的代碼段,并在模塊內(nèi)任意位置被調(diào)用,讓代碼更加的直觀易讀。

FreeRTOS中其他任務(wù)API函數(shù)

1、函數(shù) uxTaskPriorityGet() 此函數(shù)用來獲取指定任務(wù)的優(yōu)先級,要使用此函數(shù)的話宏 INCLUDE_uxTaskPriorityGet 應(yīng) 該定義為 1。 2、

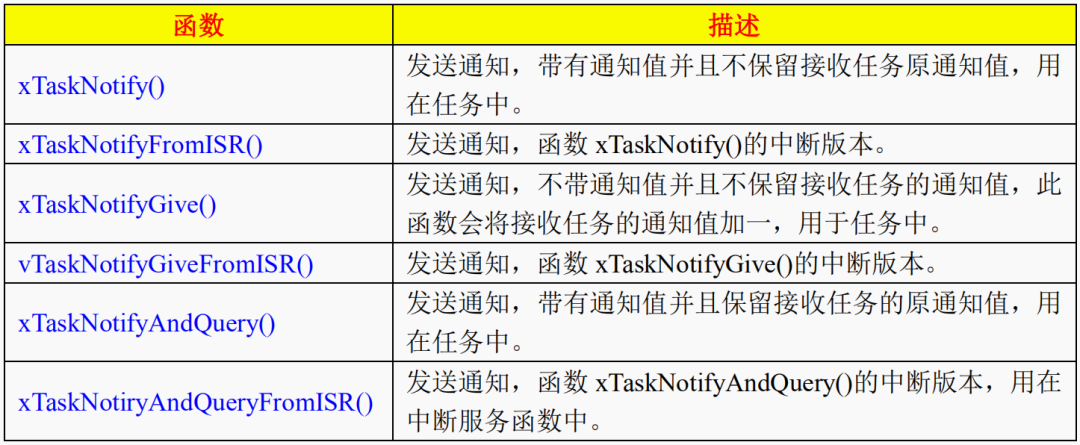

FreeRTOS任務(wù)通知通用發(fā)送函數(shù)

發(fā)送任務(wù)通知 任務(wù)通知通用發(fā)送函數(shù) 任務(wù)級任務(wù)通知發(fā)送函數(shù):xTaskNotify()、xTas

verilog function函數(shù)的用法

Verilog 是一種硬件描述語言 (HDL),主要用于描述數(shù)字電子電路的行為和結(jié)構(gòu)。在 Verilog 中,函數(shù) (Function) 是一種用于執(zhí)行特定

verilog中函數(shù)和任務(wù)對比

verilog中函數(shù)和任務(wù)對比

評論