Verilog 是一種硬件描述語言 (HDL),主要用于描述數字電子電路的行為和結構。在 Verilog 中,函數 (Function) 是一種用于執行特定任務并返回一個值的可重用代碼塊。函數在 Verilog 中被廣泛用于對電路進行模塊化設計,以簡化和組織代碼。

本文將詳細介紹 Verilog 函數的用法,并探討函數在硬件設計中的重要性和實際應用場景。

一. Verilog 函數概述

Verilog 函數通過提供一種結構化的方式來組織代碼,并可以根據需要重復使用。它們可以在模塊內部或外部定義,可以在模塊中的任何位置調用,并可以接受輸入參數并返回一個值。

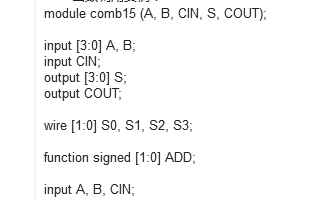

函數定義的一般語法如下所示:

function [返回值類型] [函數名稱] ([參數1], [參數2], ...);

// 函數體

return [返回值];

endfunction

endfunction

endfunction其中:

- [返回值類型]:指定函數返回值的數據類型。可以是任何 Verilog 數據類型,如整數 (integer)、位向量 (bit vector)、布爾值 (boolean) 等。

- [函數名稱]:函數的唯一標識符,用于在其他地方調用該函數。

- [參數1], [參數2], ...:函數的輸入參數。每個參數都有一個數據類型和一個名稱。

- [返回值]:函數執行完成后返回的值,必須與 [返回值類型] 的數據類型匹配。

函數體可以包含任意數量的語句,可以使用變量、操作符、控制結構等來進行邏輯運算、數學運算等操作。函數可以調用其他函數,還可以使用模塊中定義的信號和變量。

二. Verilog 函數的優勢

使用函數主要有以下幾個優勢:

- 代碼重用:函數提供了一種封裝代碼的方法,可以在需要的地方多次調用,避免了代碼的重復編寫,提高了代碼的可讀性和可維護性。

- 模塊化設計:函數可以將電路的不同功能模塊化,使整個設計更加清晰和易于理解。這種模塊化的設計方法促進了團隊合作和并行開發,提高了開發效率。

- 簡化復雜邏輯:函數可以將復雜的邏輯分解為更小的、易于理解的部分。這使得電路的設計和調試更加簡單直觀,并且減少了出錯的可能性。

- 參數化設計:函數可以接受輸入參數,根據參數的不同值執行不同的操作。這種參數化的設計方法可以根據不同的需求生成多個實例,從而節省了設計時間和資源。

- 更好的性能:使用函數可以將一些常用的邏輯實現為高度優化的代碼,并通過調用函數來提供功能。這種方法可以提高電路的性能和效率。

三. Verilog 函數的實例

下面是一個簡單的 Verilog 函數的示例,該函數用于計算兩個輸入參數的乘積:

function integer multiply(int a, int b);

integer result;

result = a * b;

return result;

endfunction

// 在其他地方調用該函數

integer m;

m = multiply(2, 3);

m = multiply(2, 3);

m = multiply(2, 3);在上述示例中,函數 multiply 接受兩個整數參數 a 和 b,并返回它們的乘積。函數體中的變量 result 用于保存乘積的結果,并通過 return 語句將其返回給調用者。在其他地方,我們將函數 multiply(2, 3) 的返回值賦給變量 m。

四. Verilog 函數的使用注意事項

在使用 Verilog 函數時,需要注意以下事項:

- 函數只能在模塊中定義,不支持在過程塊 (Procedural Blocks) 中定義。

- 函數只能在聲明之后調用。因此,如果函數在調用之前定義,則需要在模塊開頭聲明該函數。

- 函數不能對模塊的輸入、輸出端口進行賦值操作。函數只能使用輸入參數進行計算,并通過返回值傳遞結果。

- 函數內部不允許定義信號或變量的方向。在函數內訪問的信號或變量默認為局部變量,其范圍僅限于該函數內部。

- 函數不能使用非阻塞賦值語句 (<=)。只能使用阻塞賦值語句 (=) 進行賦值操作。

- 函數可以調用其他函數,但要確保函數調用不會形成循環依賴。

五. Verilog 函數的實際應用場景

Verilog 函數在硬件設計中有許多實際應用場景。以下是幾個常見的應用場景:

- 邏輯單元:函數可用于實現邏輯單元,如與門、或門等。函數可以接受多個輸入信號,并根據這些信號的值返回一個輸出信號。

- 狀態機:函數可以用于實現狀態機的不同狀態和狀態轉換邏輯。每個狀態可以被定義為一個函數,并根據輸入信號和當前狀態值來執行特定的操作。

- 復雜計算:函數可用于實現復雜的計算邏輯,如乘法運算、除法運算、開方等。通過將這些復雜的計算邏輯封裝為函數,可以提高代碼的可讀性和可維護性。

- 緩存控制:函數可用于實現硬件緩存的控制邏輯,如寫控制、讀控制、替換策略等。通過將這些復雜的控制邏輯封裝為函數,可以簡化整個緩存控制器的設計。

- 錯誤檢測與糾正:函數可用于實現錯誤檢測與糾正的邏輯,如校驗和計算、奇偶校驗等。這些函數可以用于在數字通信和存儲系統中保護數據的完整性。

六. 總結

本文詳細介紹了 Verilog 函數的用法,并探討了函數在硬件設計中的重要性和實際應用場景。Verilog 函數提供了一種封裝代碼的方法,使硬件設計變得更加模塊化、簡單和可擴展。通過合理使用函數,我們可以提高代碼的可讀性和可維護性,提高設計效率,實現復雜的邏輯運算和控制。

-

Verilog

+關注

關注

29文章

1366瀏覽量

111865 -

Function

+關注

關注

0文章

14瀏覽量

10068 -

函數

+關注

關注

3文章

4371瀏覽量

64225 -

代碼

+關注

關注

30文章

4887瀏覽量

70270

發布評論請先 登錄

Verilog函數中function里的過程語句該怎么寫

簡談FPGA verilog中的function用法與例子

講解function任務的用法

verilog function函數的用法

verilog function函數的用法

評論