歡迎了解

楊彥章 鐘上彪 陳志華

(光華科學(xué)技術(shù)研究院(廣東)有限公司)

摘要

先進(jìn)封裝是半導(dǎo)體行業(yè)未來(lái)發(fā)展的重要一環(huán),是超越摩爾定律的關(guān)鍵技術(shù)。本文通過(guò)對(duì)不同封裝材料進(jìn)行表面金屬化處理,發(fā)現(xiàn)粗糙度和鍍層應(yīng)力對(duì)鍍層結(jié)合力均有顯著影響。選擇合適的粗化方法及低應(yīng)力電鍍銅鍍液可以在不顯著增加封裝材料表面粗糙度的情況下提高鍍層結(jié)合力(剝離強(qiáng)度>0.53 N/mm),從而有利于制作精細(xì)線路(線寬/線距=15 μm/15 μm)。

0 引言

先進(jìn)封裝包括PLP、SOC、SIP等封裝,是順應(yīng)半導(dǎo)體行業(yè)向更小尺寸、更高性能發(fā)展趨勢(shì)的新的高技術(shù)含量的封裝技術(shù) [1]-[4] 。先進(jìn)封裝表面金屬化可以實(shí)現(xiàn)封裝體電磁屏蔽、散熱、導(dǎo)電等功能,進(jìn)一步減小封裝器件的尺寸,并且提高封裝器件的性能 [5]-[7] 。目前先進(jìn)封裝表面金屬化存在粗糙度高、結(jié)合力低等問(wèn)題,面臨難以制作精細(xì)線路的挑戰(zhàn) [8]-[10] 。針對(duì)這一問(wèn)題,本文通過(guò)優(yōu)化封裝材料表面粗化技術(shù)和使用低應(yīng)力電鍍銅鍍液,成功實(shí)現(xiàn)低粗糙度高結(jié)合力的鍍層,并完成精細(xì)線路的制作。

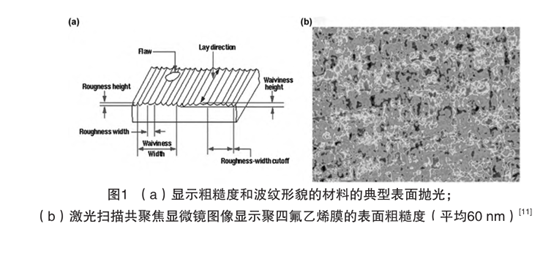

1 粗糙度

粗糙度是表征材料表面形貌的參數(shù)(如圖1所示),其數(shù)值大小對(duì)鍍層結(jié)合力有顯著影響 [11] 。一般來(lái)講,粗糙度越大越有利于鍍層結(jié)合力的增加,因此提高鍍層結(jié)合力的重要手段在于增加接觸面的粗糙度。然而粗糙度過(guò)大不利于制作精細(xì)線路 [12] 。

2 鍍層應(yīng)力

應(yīng)力廣泛存在于各種材料中,對(duì)材料的機(jī)械、化學(xué)等性能有重要影響 [13] 。電鍍層的鍍層應(yīng)力會(huì)影響鍍層硬度和開(kāi)裂,例如應(yīng)力越大的鍍層其鍍層機(jī)械性能越差。影響鍍層應(yīng)力的因素有很多,如鍍液配方、電鍍參數(shù)等 [14] 。

3 實(shí)驗(yàn)方案

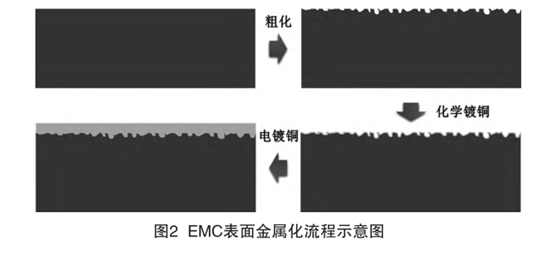

3.1 原理

如圖2所示,首先對(duì)封裝材料表面進(jìn)行粗化,然后使用化學(xué)鍍?cè)诒砻驽兩戏N子層金屬銅(<1 μm),最后使用電鍍銅增加鍍層厚度(>10 μm)。

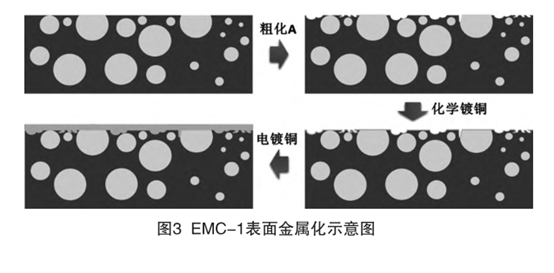

如圖3所示,使用粗化方法A對(duì)封裝材料EMC-1表面的樹(shù)脂區(qū)域進(jìn)行咬蝕,增大表面的粗糙度,然后使用化學(xué)鍍?cè)诒砻驽兩戏N子層金屬銅,最后使用電鍍銅增加鍍層厚度。

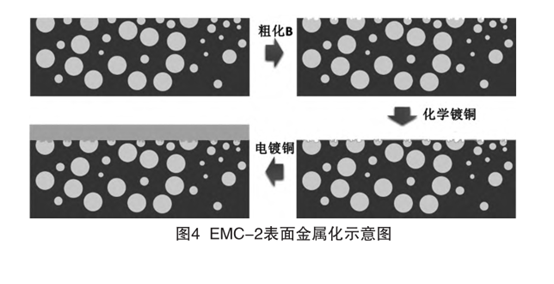

如圖4所示,使用粗化方法B對(duì)封裝材料EMC-2表面的填料區(qū)域進(jìn)行咬蝕,增大表面的粗糙度,然后使用化學(xué)鍍?cè)诒砻驽兩戏N子層金屬銅,最后使用電鍍銅增加鍍層厚度。

3.2 試驗(yàn)材料及測(cè)試設(shè)備

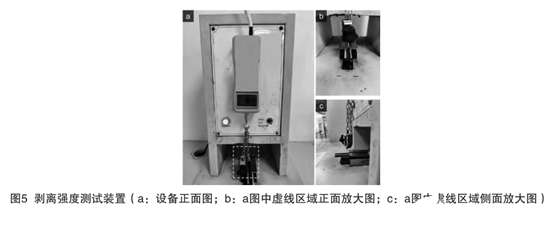

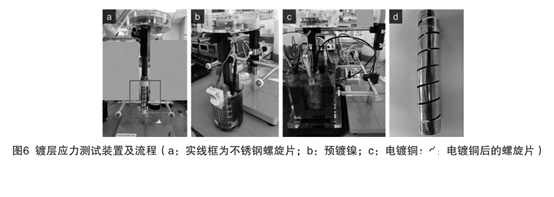

本文所使用的封裝材料均為環(huán)氧樹(shù)脂塑封料(EMC),這種類(lèi)型的封裝材料占整個(gè)電子封裝材料的90%以上。EMC材料共有兩種,差異主要體現(xiàn)在填料的篩分粒徑不同——EMC-1和EMC-2的篩分粒徑分別為50 μm和20 μm。測(cè)試設(shè)備包括激光共聚焦顯微鏡、電子掃描顯微鏡、剝離強(qiáng)度測(cè)試儀(如圖5所示)、應(yīng)力測(cè)試儀(如圖6所示)。

4 實(shí)驗(yàn)結(jié)果及分析

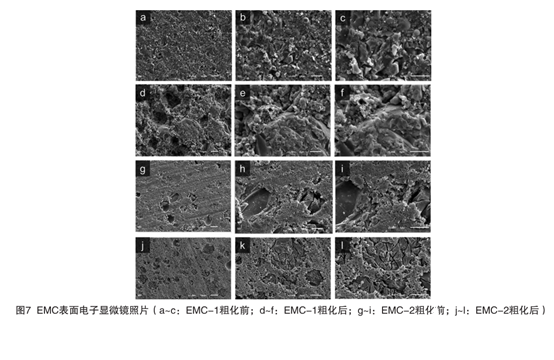

EMC-1和EMC-2粗化前后表面的SEM照片如圖7所示。從圖中結(jié)果可以看出,粗化后的EMC材料表面形貌較粗化前變得更加粗糙:(1)粗化后的EMC-1表面樹(shù)脂區(qū)域被咬蝕的微坑尺寸明顯增大;(2)粗化后的EMC-2表面填料區(qū)域出現(xiàn)了清晰的咬蝕裂紋。

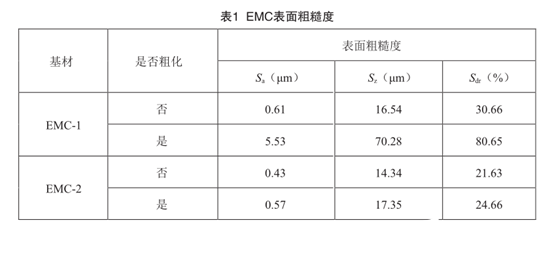

為進(jìn)一步分析粗化前后的EMC表面粗糙度,我們使用激光共聚焦顯微鏡對(duì)EMC表面粗糙度進(jìn)行表征,結(jié)果列于表1。從表1可以看出,EMC-1粗化后的表面粗糙度相較于粗化前顯著增大,而EMC-2粗化后的表面粗糙度相較于粗化前增加不明顯。這與圖7的表征結(jié)果是一致的。

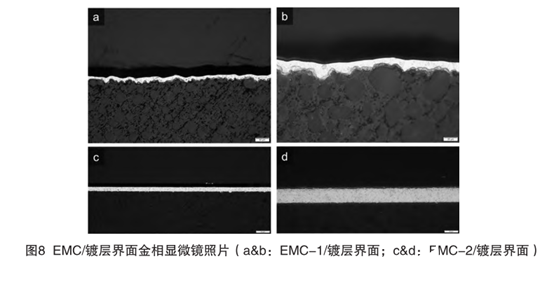

EMC表面電鍍銅后的界面結(jié)構(gòu)如圖8所示。從圖中可以看出,EMC-1/鍍層界面起伏較大,這是由于EMC-1粗化后的表面粗糙度大(與圖7d-f和表1一致)。EMC-2/鍍層界面相較于EMC-1/鍍層界面更加平坦,無(wú)顯著起伏波動(dòng)(與圖7j-l和表1一致),這樣的界面更易制作精細(xì)線路。

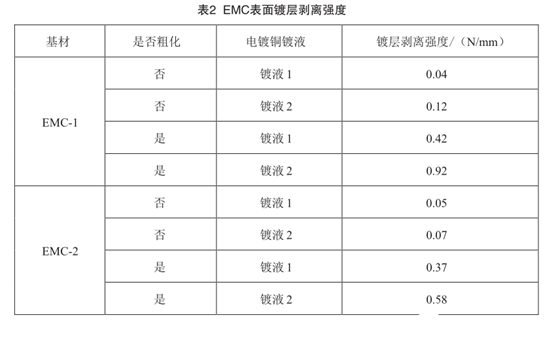

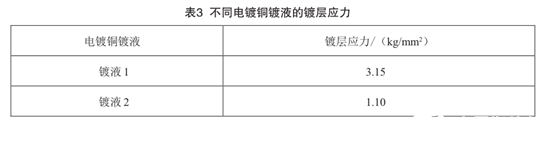

我們使用剝離強(qiáng)度來(lái)表征鍍層與EMC之間的結(jié)合力。從表2可以看出,相較于未經(jīng)過(guò)表面粗化處理的EMC材料,經(jīng)過(guò)表面粗化處理后的EMC材料表面鍍層的剝離強(qiáng)度顯著增加,這表明EMC表面粗糙度對(duì)鍍層結(jié)合力起重要作用。此外,不同的電鍍銅鍍液獲得的鍍層剝離強(qiáng)度不同:在相同前處理?xiàng)l件下,鍍液2獲得的鍍層結(jié)合力要優(yōu)于鍍液1。這是由于鍍液2的鍍層應(yīng)力更低(如表3所示),所以獲得的鍍層與基材之間的結(jié)合力更高。

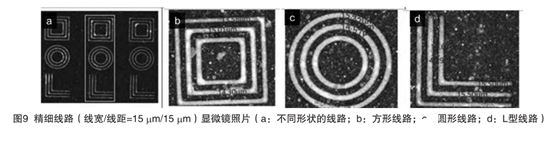

在前面實(shí)驗(yàn)結(jié)果的基礎(chǔ)上,我們使用SAP工藝在EMC-2表面制作精細(xì)線路。如圖9所示,使用SAP工藝成功在EMC-2表面制作出線寬/線距=15 μm/15 μm的精細(xì)線路,且未出現(xiàn)線路脫落的現(xiàn)象,這表明該金屬化工藝可以滿(mǎn)足精細(xì)線路的制作要求。

5 結(jié)論

環(huán)氧塑封料是先進(jìn)封裝常用的封裝材料。本文研究了濕化學(xué)工藝中前處理和電鍍對(duì)兩種填料粒徑不同的EMC封裝材料表面鍍層結(jié)合力的影響,發(fā)現(xiàn)增加表面粗糙度和降低電鍍銅層鍍層應(yīng)力可以有效提高鍍層結(jié)合力:最大剝離強(qiáng)度可達(dá)0.92 N/mm。選擇填料尺寸較小的EMC材料,可以在低的表面粗糙度下(Sz<18 μm)實(shí)現(xiàn)0.58 N/mm的鍍層結(jié)合力,并且使用SAP工藝制作出線寬/線距=15 μm/15 μm的精細(xì)線路。這些實(shí)驗(yàn)結(jié)果為適應(yīng)未來(lái)先進(jìn)封裝金屬化更高的要求提供了解決思路,也為電介質(zhì)-金屬互聯(lián)工藝提供了技術(shù)參考。

審核編輯 黃宇

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28585瀏覽量

232451 -

封裝

+關(guān)注

關(guān)注

128文章

8479瀏覽量

144775 -

SAP

+關(guān)注

關(guān)注

1文章

428瀏覽量

21938

發(fā)布評(píng)論請(qǐng)先 登錄

電子封裝中的高導(dǎo)熱平面陶瓷基板及金屬化技術(shù)研究

IC封裝產(chǎn)線分類(lèi)詳解:金屬封裝、陶瓷封裝與先進(jìn)封裝

效率突破24.32%!江蘇大學(xué)J Mater Sci發(fā)文:雙面鍍銅金屬化n-TOPCon太陽(yáng)能電池的穩(wěn)定性研究

超聲波焊接有利于解決固態(tài)電池的枝晶問(wèn)題

碳化硅晶片表面金屬殘留的清洗方法

美能網(wǎng)版智能影像測(cè)試儀亮相N型高效電池大會(huì),彰顯電池金屬化技術(shù)應(yīng)用優(yōu)勢(shì)

先進(jìn)封裝中RDL工藝介紹

什么是先進(jìn)封裝中的Bumping

玻璃基板之通孔金屬化電鍍技術(shù)

改進(jìn)絲網(wǎng)印刷工藝,晶硅太陽(yáng)能電池正面銀電極金屬化效率高達(dá)22.1%

如何測(cè)量晶圓表面金屬離子的濃度

金屬化膜電容器的方阻選擇標(biāo)準(zhǔn)

無(wú)鉛共晶焊料在厚Cu凸點(diǎn)下金屬化層上的潤(rùn)濕反應(yīng)

金屬化薄膜電容氧化時(shí)方阻會(huì)變大嗎

先進(jìn)封裝技術(shù)綜述

先進(jìn)封裝表面金屬化研究

先進(jìn)封裝表面金屬化研究

評(píng)論