年復(fù)一年,越來越多的用戶通過無線方式傳輸越來越多的數(shù)據(jù)。為了跟上這一趨勢并使數(shù)據(jù)傳輸更快、更高效,第五代移動通信 (5G) 正在推出,業(yè)界已經(jīng)在關(guān)注未來的發(fā)展。5G 可實現(xiàn) 10Gbit/s 的峰值數(shù)據(jù)速率,而 6G 預(yù)計從 2030 年起將以 100Gbit/s 的速度運行。除了應(yīng)對更多數(shù)據(jù)和連接之外,研究人員還研究下一代無線通信如何支持自動駕駛和全息存在等新用例。

為了實現(xiàn)極高的數(shù)據(jù)速率,電信行業(yè)一直在提高無線信號的頻率。雖然 5G 最初使用 6GHz 以下頻段,但針對 28/39GHz 的產(chǎn)品已經(jīng)展示。此外,由于 FR3 (6-20GHz) 頻段能夠平衡覆蓋范圍和容量,因此人們對 5G 網(wǎng)絡(luò)使用 FR3 (6-20GHz) 頻段越來越感興趣。對于 6G,100GHz 以上的頻率正在討論中。

轉(zhuǎn)向更高的頻率有幾個優(yōu)點:可以使用新的頻段,解決現(xiàn)有頻段內(nèi)的頻譜稀缺問題。而且,工作頻率越高,就越容易獲得更寬的帶寬。原則上,高于 100GHz 的頻率和高達 30GHz 的帶寬允許電信運營商在無線數(shù)據(jù)鏈路中使用低階調(diào)制方案,從而降低功耗。較高的頻率還與較小的波長 (λ) 相關(guān)。隨著天線陣列尺寸隨λ 2縮放,天線陣列可以排列得更密集。這有助于更好的波束成形,這種技術(shù)可確保大部分傳輸能量到達目標接收器。

但更高頻率的出現(xiàn)是有代價的。如今,CMOS是構(gòu)建發(fā)射器和接收器關(guān)鍵組件的首選技術(shù)。其中包括前端模塊內(nèi)的功率放大器,用于向天線發(fā)送射頻信號或從天線發(fā)送射頻信號。工作頻率越高,基于 CMOS 的功率放大器就越難以以足夠高的效率提供所需的輸出功率。

這就是GaN 和 InP等技術(shù)發(fā)揮作用的地方。由于出色的材料特性,這些 III/V 族半導(dǎo)體更有可能在高工作頻率下提供所需的輸出功率和效率。例如,GaN具有高電流密度、高電子遷移率和大擊穿電壓。高功率密度還可以實現(xiàn)較小的外形尺寸,從而在相同性能的情況下減小總體系統(tǒng)尺寸。

01GaN 和 InP 在更高的工作頻率下優(yōu)于 CMOS

在建模實驗中,imec 的研究人員比較了140GHz工作頻率下三種不同功率放大器實現(xiàn)的性能:全 CMOS 實現(xiàn)、帶有 SiGe 異質(zhì)結(jié)雙極晶體管 (HBT) 的 CMOS 波束形成器(beamformer)和InP HBT。InP 在輸出功率(超過 20dBm)和能源效率(20% 至 30%)方面明顯獲勝。建模結(jié)果還表明,對于 InP,能量效率的最佳點是通過相對較少的天線數(shù)量獲得的。這對于用戶設(shè)備(例如移動設(shè)備)等占地面積受限的用例尤其有趣。

圖 1 – 比較發(fā)射器架構(gòu)中 CMOS、SiGe 和 InP 器件的功耗與天線數(shù)量的關(guān)系(如 IEDM 2022 上所述)。

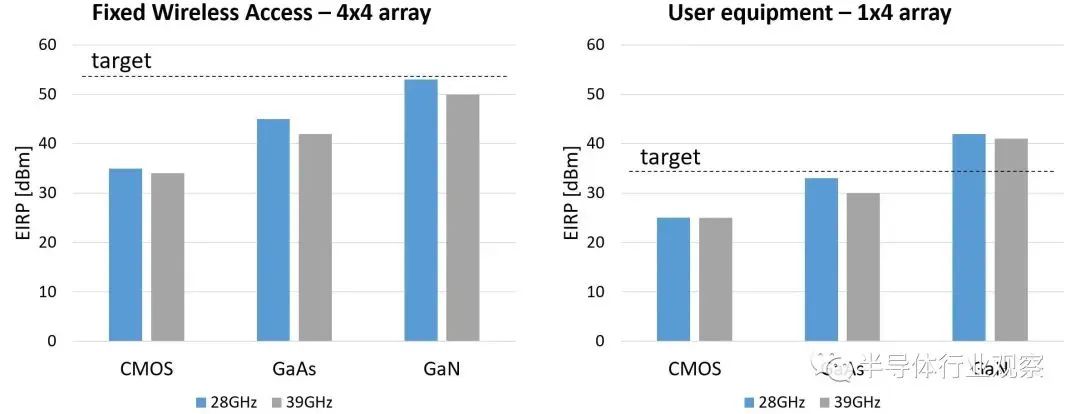

然而,在較低的毫米波頻率下,GaN表現(xiàn)出優(yōu)異的性能。對于28GHz 和 39GHz,由碳化硅上氮化鎵 (GaN-on-SiC) 制成的高電子遷移率晶體管 (HEMT) 在輸出功率和能效方面均優(yōu)于基于 CMOS 的器件和 GaAs HEMT。考慮了兩種不同的用例,即固定無線接入(FWA,具有 16 個天線)和用戶設(shè)備(具有 4 個天線)。

圖 2 –(左)FWA 和(右)用戶設(shè)備中 28GHz 和 39GHz 工作頻率的輸出功率:三種不同技術(shù)的比較(如 IEDM 2022 上所示)。

02升級的機遇與挑戰(zhàn)

但如果我們考慮成本和集成的簡易性,GaN 和 InP 器件技術(shù)還無法與基于 CMOS 的技術(shù)完全競爭。III/V 器件通常在小型且昂貴的非硅襯底上制造,依賴于不太適合大批量制造的工藝。將這些器件集成在 200 或 300mm 硅晶圓上是一種有趣的方法,可以在保持卓越射頻性能的同時實現(xiàn)整體優(yōu)化。硅基板不僅更便宜,而且兼容 CMOS 的工藝還可以實現(xiàn)大規(guī)模制造。

在 Si 平臺上集成 GaN 和 InP需要結(jié)合新的晶體管和電路設(shè)計方法、材料和制造技術(shù)。主要挑戰(zhàn)之一與大晶格失配有關(guān):InP 為 8%,GaN 為 17%。眾所周知,這會在層中產(chǎn)生許多缺陷,最終降低器件性能。

此外,我們還必須將基于 GaN-on-Si 和 InP-on-Si 的組件與基于 CMOS 的組件共同集成到一個完整的系統(tǒng)中。GaN 和 InP 技術(shù)最初將用于實現(xiàn)前端模塊內(nèi)的功率放大器。此外,低噪聲放大器和開關(guān)可能受益于這些化合物半導(dǎo)體的獨特性能。但最終,校準、控制和波束形成仍然需要 CMOS。

在其高級射頻計劃中,imec 與其行業(yè)合作伙伴一起探索在大尺寸硅晶圓上集成 GaN 和 InP 器件的各種方法,以及如何實現(xiàn)它們與 CMOS 組件的異構(gòu)集成。正在評估不同用例(基礎(chǔ)設(shè)施(例如 FWA)以及用戶設(shè)備)的優(yōu)缺點。

03改進 GaN-on-Si 技術(shù)的射頻性能

根據(jù)起始襯底的不同,GaN 技術(shù)有多種類型:GaN bulk substrates, GaN-on-SiC和GaN-on-Si。如今,GaN-on-SiC得到了廣泛探索,并已用于基礎(chǔ)設(shè)施應(yīng)用,包括 5G 基站。GaN-on-SiC比GaN bulk substrates技術(shù)更具成本效益,而且碳化硅是一種出色的熱導(dǎo)體,有助于散發(fā)高功率基礎(chǔ)設(shè)施應(yīng)用中產(chǎn)生的熱量。然而,成本和基板尺寸有限使其不太適合大規(guī)模生產(chǎn)。

相反,GaN-on-Si具有擴大到 200mm 甚至 300mm 晶圓的潛力。得益于多年來電力電子應(yīng)用的創(chuàng)新,GaN在大尺寸Si襯底上的集成取得了巨大進展。但硅基氮化鎵技術(shù)還需要進一步改進,以實現(xiàn)最佳射頻性能。主要挑戰(zhàn)在于實現(xiàn)與 GaN-on-SiC 相當?shù)拇笮盘柡涂煽啃孕阅芤约疤岣吖ぷ黝l率。這需要在材料堆疊設(shè)計和材料選擇方面不斷創(chuàng)新,縮短 HEMT 的柵極長度,抑制寄生效應(yīng),并保持盡可能低的射頻色散。

Imec 的射頻 GaN-on-Si 工藝流程從在 200mm Si 晶圓上生長(通過金屬有機化學(xué)氣相沉積 (MOCVD))外延結(jié)構(gòu)開始。該結(jié)構(gòu)由專有的 GaN/AlGaN 緩沖結(jié)構(gòu)、GaN 溝道、AlN 間隔物和 AlGaN 勢壘組成。具有 TiN 肖特基金屬柵極的 GaN HEMT 器件隨后與(低溫)3 級 Cu 后道工藝集成。

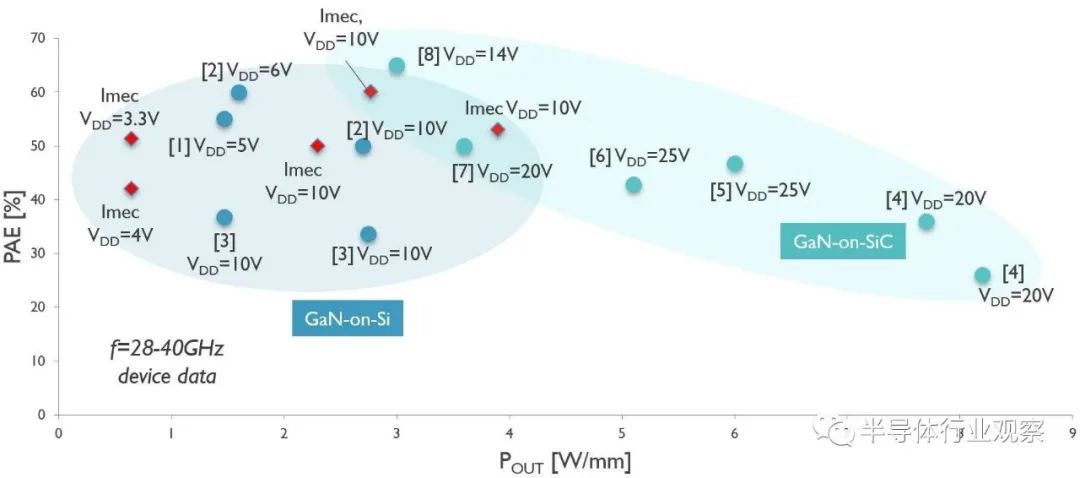

近期,imec的GaN-on-Si平臺取得了具有競爭力的成果,輸出功率和功率附加效率(PAE)首次接近GaN -on-SiC技術(shù)。PAE 是評估功率放大器效率的常用指標,它考慮了放大器增益對其整體效率的影響。

圖 3 - 硅基氮化鎵基準測試數(shù)據(jù)。紅色的 IMEC 數(shù)據(jù)是 GaN-on-Si 器件的最佳報告之一,可與 GaN-on-SiC 襯底相媲美(如 IEDM 2022 上介紹的)。

通過建模活動補充技術(shù)開發(fā)將最終有助于實現(xiàn)更好的性能和可靠性。例如,在 IEDM 2022 上,imec 推出了一個仿真框架,可以更好地預(yù)測射頻設(shè)備中的熱傳輸。在硅基氮化鎵 HEMT 的案例研究中,模擬顯示峰值溫升比之前預(yù)測的高出三倍。諸如此類的建模工作為在開發(fā)階段早期優(yōu)化射頻器件及其布局提供了進一步的指導(dǎo)。

04用于 6G 亞太赫茲頻率的 InP-on-Si:三種制造方法

如前所述,InP HBT在所有技術(shù)實現(xiàn)的140GHz工作頻率下提供最佳輸出功率/效率權(quán)衡。研究人員還知道如何設(shè)計 InP HBT 以獲得最佳射頻性能。但制造通常從小型 (InP) 襯底晶圓 (< 150mm) 開始,使用與CMOS 不兼容的類似實驗室的工藝。

但是當我們在 Si 上集成 InP 時,性能會發(fā)生什么變化呢?眾所周知,在 Si 上沉積 InP 會引入許多缺陷,主要是螺紋位錯( threading dislocations)和平面缺陷(planar defects)。這些缺陷會引起漏電流,從而極大地降低器件性能或?qū)е驴煽啃詥栴}。

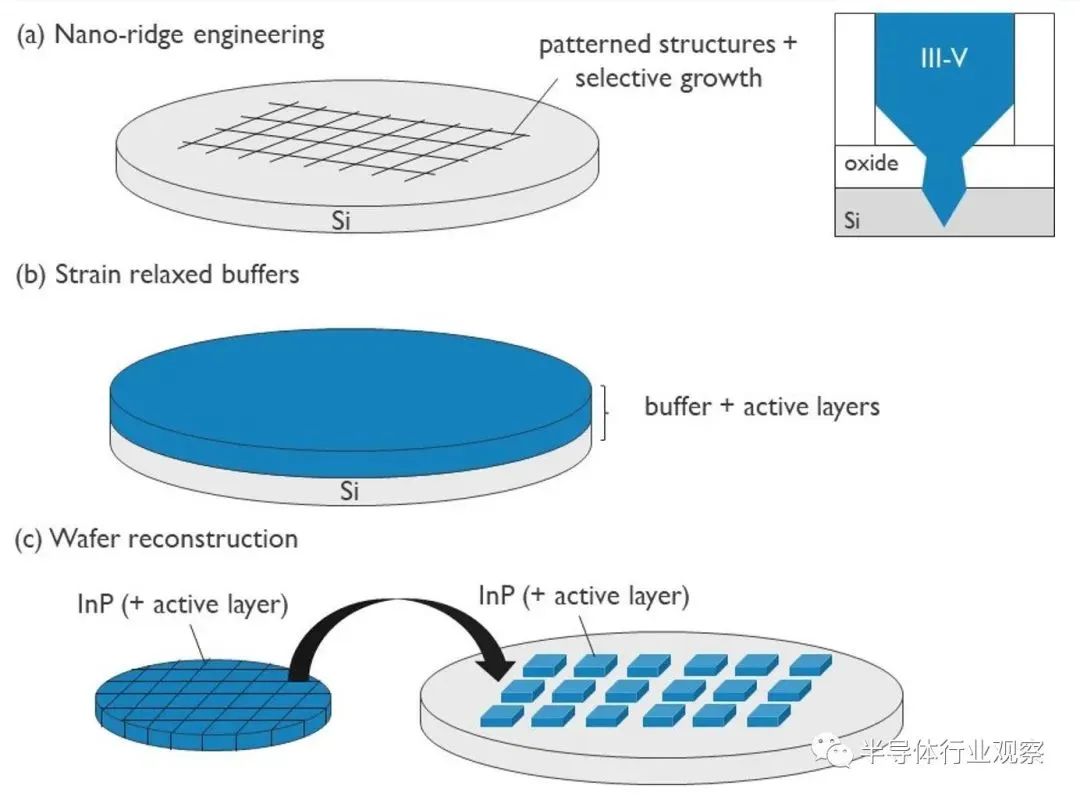

正在考慮三種升級方法。其中兩個依賴于 Si 上 InP 的直接生長,另一個依賴于晶圓重構(gòu)。預(yù)計所有三種方法都將提供比使用小型 InP 襯底的現(xiàn)有技術(shù)更具成本效益的解決方案。但它們在性能、成本和異構(gòu)集成潛力方面都各有利弊。Imec 承擔了評估各種用例(基礎(chǔ)設(shè)施以及移動設(shè)備)的優(yōu)勢和挑戰(zhàn)的角色。

圖 4 – 不同 InP-on-Si 生長方法的示意圖:(a) nano-ridge engineering; (b) blanket growth with strain relaxed buffers, and (c) wafer reconstruction.

制造 InP-on-Si HBT 的第一種方法(圖 4b)使用直接沉積在 Si 頂部的應(yīng)變松弛緩沖層,以補償 Si 和 InP 之間 8% 的晶格失配。接下來,InP直接生長在該緩沖層的頂部。使用更大晶圓尺寸的能力,特別是在部分硅可以重復(fù)使用的情況下,提供了顯著的成本優(yōu)勢。然而,需要優(yōu)化以進一步減少缺陷數(shù)量。

與這種“blanket”生長方法不同,imec 提出nano-ridge engineering(NRE) 作為更有效地應(yīng)對缺陷的替代技術(shù)(圖 4a)。NRE 依賴于在 Si 中預(yù)先圖案化的溝槽中選擇性生長 III/V 族材料。這些高深寬比溝槽對于捕獲狹窄底部中的缺陷非常有效,并允許在溝槽外生長高質(zhì)量、低缺陷率的材料。過度生長的nano-ridge使其向頂部變寬,為設(shè)備堆棧形成堅實的基礎(chǔ)。從 GaAs/InGaP 案例研究中獲得的初步見解將指導(dǎo)目標 InGaAs/InP NRE HBT 器件的優(yōu)化。

除了直接生長之外,InP 還可以使用晶圓重建技術(shù)放置在 Si 上(圖 4c)。在這種情況下,高質(zhì)量 InP 襯底(無論是否有有源層)在晶圓構(gòu)造過程中被切成片。隨后使用芯片到晶圓鍵合技術(shù)將這些瓦片附著到硅晶圓上。主要挑戰(zhàn)在于材料的有效轉(zhuǎn)移和 InP 襯底的去除,為此正在考慮多種技術(shù)。

05走向異構(gòu)集成

最終,III/V-on-Si 功率放大器必須與負責校準和控制等功能的基于 CMOS 的組件相結(jié)合。Imec 正在研究各種異構(gòu)集成選項,權(quán)衡它們在各種用例中的優(yōu)缺點。

先進的層壓基板技術(shù)是將不同射頻元件集成到系統(tǒng)級封裝中的最常見方法,并且正在進行優(yōu)化以使其能夠適應(yīng)更高的頻率。

此外,imec還探索更先進的異構(gòu)集成選項,包括2.5D中介層和3D集成技術(shù)。

特別是對于 100GHz 以上的頻率,需要注意的是天線模塊開始定義收發(fā)器可用的區(qū)域。事實上,當頻率較高時,波長會減小,天線陣列的面積也會相應(yīng)縮小。在 100GHz 以上,天線尺寸變得小于前端模塊尺寸,而前端模塊尺寸幾乎不會隨著頻率的增加而縮小。對于大型天線陣列配置,一個有趣的選擇是將射頻前端模塊移至天線陣列下方。這就是3D 集成技術(shù)的用武之地(die-to-wafer or 和wafer-to-wafer)發(fā)揮作用,實現(xiàn)前端模塊和天線模塊之間的短且明確的連接。然而,熱管理仍然是 3D 集成的一個重要問題,并且能夠提供有效的散熱器至關(guān)重要。在imec,我們正在進行全面的系統(tǒng)技術(shù)協(xié)同優(yōu)化 (STCO) 分析,以評估用于 3D 集成的不同技術(shù),并從系統(tǒng)級角度指導(dǎo)技術(shù)選擇。

對于手持設(shè)備,減少天線數(shù)量可以放松限制,2.5D interposer技術(shù)被認為是一種有趣的方法。這種異構(gòu)集成選項使用具有光刻定義連接的層堆棧,甚至是硅通孔,以在基于 III/V 和 CMOS 的組件之間進行通信。在這種情況下,III/V 器件位于 CMOS 芯片旁邊,可以實現(xiàn)更好的熱管理,因為兩個芯片都可以與散熱器直接接觸。然而,這種架構(gòu)僅允許一維波束控制。我們目前正在評估 2.5D 中介層技術(shù)的硬件實現(xiàn),研究基板、電介質(zhì)和再分布層的最佳組合,以最大限度地減少損耗。例如,我們展示了射頻定制硅中介層技術(shù)的第一個版本,該技術(shù)使用標準硅基板、銅半加成互連。

總之,最近的升級和集成工作表明,硅基氮化鎵和硅基磷化銦可以成為下一代高容量無線通信應(yīng)用的可行技術(shù)。

來源:半導(dǎo)體行業(yè)觀察編譯自imec

審核編輯:湯梓紅

-

CMOS

+關(guān)注

關(guān)注

58文章

5991瀏覽量

238074 -

功率放大器

+關(guān)注

關(guān)注

102文章

3928瀏覽量

133871 -

發(fā)射器

+關(guān)注

關(guān)注

6文章

875瀏覽量

54256 -

GaN

+關(guān)注

關(guān)注

19文章

2177瀏覽量

76158 -

射頻芯片

+關(guān)注

關(guān)注

984文章

434瀏覽量

80711

發(fā)布評論請先 登錄

為什么說射頻前端的一體化設(shè)計決定下一代移動設(shè)備?

如何建設(shè)下一代蜂窩網(wǎng)絡(luò)?

請問Ultrascale FPGA中單片和下一代堆疊硅互連技術(shù)是什么意思?

【MPS電源評估板試用申請】下一代接入網(wǎng)的芯片研究

下一代網(wǎng)絡(luò)概述

下一代無線設(shè)備的射頻芯片設(shè)計挑戰(zhàn)

華為芯片斷代 臺積電將投產(chǎn)下一代芯片制程工藝

早報:下一代iPhone芯片或?qū)⑹褂门_積電的5nm+工藝

超越摩爾定律,下一代芯片如何創(chuàng)新?

下一代射頻芯片工藝路在何方?

下一代射頻芯片工藝路在何方?

評論