從3G升級到LTE-Advance,對下一代移動通信基礎設施的設備和器件供應商提出了諸多挑戰(zhàn)。下一代無線設備要求支持更寬的信號帶寬、更復雜的調(diào)制方式,以便在全球范圍內(nèi)部署的各種運行頻段上都能獲得更高的數(shù)據(jù)速率。因此,噪聲、信號線性度、功耗和外形尺寸等性能都非常關鍵,對這些性能的要求也更苛刻。此外,元器件供應商同樣被要求降低元器件的成本和尺寸以支持更高密度的應用。

射頻芯片(RF IC)設計師面臨的挑戰(zhàn)也將日益艱巨,因為集成方案必須具有或超過分立元器件實現(xiàn)的性能。在采用分立元器件實現(xiàn)方案時,系統(tǒng)設計師可以分別采取不同技術(如GaAs、Si Bipolar或CMOS)進行最優(yōu)化的設計。但對那些想通過單一工藝技術提供更高集成度的RF IC設計師來說,選擇最佳工藝技術所面臨的最大挑戰(zhàn)是靈活性。

在基站的發(fā)送器內(nèi),模擬I/Q調(diào)制器是決定發(fā)送信號路徑的本底噪聲和線性度的關鍵RF IC器件,不允許為降低尺寸、功耗或成本而犧牲性能。

幸運的是,SiGe BiCMOS工藝技術可實現(xiàn)更高集成度而又不犧牲性能。這些工藝通常能提供多種速度類別的SiGe NPN晶體管,在某些情況下還能提供一倍(更多時候是兩倍)于CMOS晶體管特征尺寸的互補高性能PNP晶體管。在此基礎上,還能增加MIM電容、薄膜電阻以及更重要的多層厚銅和鋁金屬膜。這些特性能夠幫助設計師在單芯片上實現(xiàn)多個高性能的功能模塊,從而大大降低功耗、縮小體積,并保持很高的性能。

發(fā)射機板級設計的一個重要方面是用于各個上變頻和下變頻轉(zhuǎn)換電路的本振時鐘的合成和分配。基站本振時鐘的分配必須保持到PCB所有遠距離位置的相位一致性,而且必須具有低的帶內(nèi)噪聲、寬帶噪聲以及總雜散噪聲。混頻器性能與驅(qū)動它的本振性能一樣,因此高質(zhì)量的本振是提高發(fā)射機總體性能的關鍵。此外,本振信號上很小的相位噪聲或雜散分量都有可能在模擬信號路徑中引入足夠大的能量,導致發(fā)射機不能滿足一些主要的蜂窩通信標準(MC-GSM、WCDMA、LTE、WiMAX)規(guī)定的雜散干擾指標。這些標準要求的本振頻率范圍為約500MHz至接近4GHz,這意味著用于本振時鐘分配的版圖設計必須十分小心。從本振產(chǎn)生到最后終結的走線長度應盡可能短,但如果本振合成器必須饋送到多個不同器件時,這個要求就很難滿足。一種解決方案是將公共的低頻參考時鐘饋送到每個本振附近的獨立PLL合成器,但這會占用很大的PCB面積。

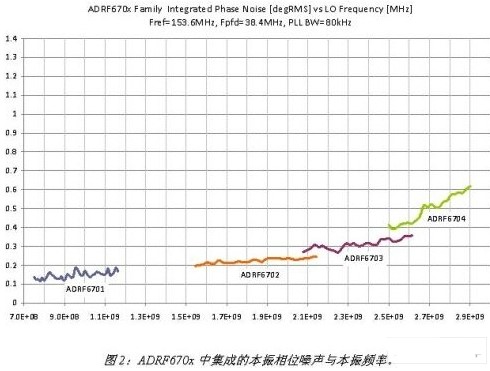

通過集成先進的小數(shù)N分頻PLL和VCO,ADRF670x系列集成式調(diào)制器解決了上述許多問題。使用硅鍺技術能讓內(nèi)置VCO的正交調(diào)制器和混頻器的動態(tài)范圍達到業(yè)界領先水平,并且具有競爭優(yōu)勢的性能,而體積顯著小于外接VCO/PLL解決方案。VCO在上層厚金屬層中實現(xiàn),可將高Q值的片上電感用作LC電路的一部分。VCO電容是用MOS開關型MIM電容組成的,因此允許VCO在寬頻范圍內(nèi)切換頻率,并具有較低的相位噪聲。每次編程PLL頻率時都會自動調(diào)整頻帶,因而能提供獨立和可靠的解決方案。在初始化完成后,頻帶大小的選擇要確保器件能在整個溫度范圍內(nèi)正常工作。厚金屬層還用來集成具有出色反射損耗的輸出平衡不平衡轉(zhuǎn)換器(Balun)。ADRF670x系列由4個頻率參數(shù)互相重疊的成員組成,覆蓋從400MHz至3GHz的頻率范圍和頻帶,每個成員都是根據(jù)1dB和3dB通帶上的輸出Balun帶寬定義的。

ADRF670x和ADRF660x系列小數(shù)N分頻PLL設計是低相位噪聲的3G和4G應用的理想之選。這些新的蜂窩標準具有密集的信號星座,要求越來越低的本振相位噪聲以獲得足夠的性能。傳統(tǒng)的PLL合成器設計使用“整數(shù)N”架構,其輸出頻率是鑒相器頻率的整數(shù)倍。為提供較小的頻率步進,整數(shù)倍增因子必須非常大。大量本振相位噪聲源于參考路徑,并被PLL頻率倍增因子所放大,這將導致PLL輸出端產(chǎn)生很高的帶內(nèi)噪聲。小數(shù)N分頻PLL允許輸出頻率有較小的步進,同時保持低的總倍頻值,因而與整數(shù)N分頻PLL相比,可以降低相位噪聲放大值。

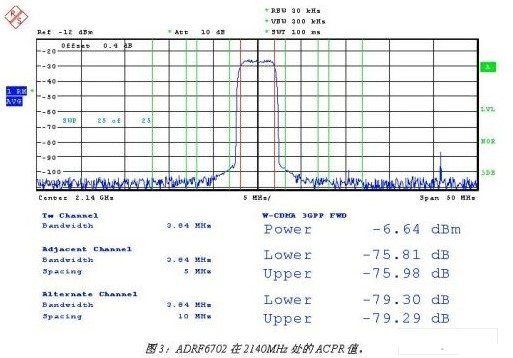

鄰信道功率比(ACPR)是判斷發(fā)射信號有多少泄漏進相鄰頻帶的一個指標。像WCDMA等3G標準對帶外發(fā)送功率有嚴格限制。ADRF6702的ACPR指標見圖3。調(diào)制器提供高度線性的輸出功率和低噪聲,因此在-6dBm輸出點有優(yōu)于-76dB的ACPR值,這有助于減少調(diào)制器后面的增益級數(shù),并使末端功放級電路前面的動態(tài)范圍達到最大。

ADRF670x系列器件集成了3個LDO電路,可在單5V電源下工作,從而進一步簡化了用戶應用、減小了成本和電路板面積。LDO用于向VCO、電荷泵以及PLL增量累加調(diào)制器提供穩(wěn)定電源,+5V電源可直接用于I-Q調(diào)制器,以使輸出功率最大。

在高密度應用中,ADL670x可以利用PLL完成本振的內(nèi)部合成,而其它器件可以禁用它們的PLL,并使用來自某個主器件的公共本振。

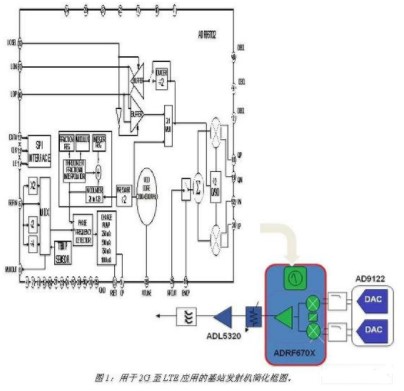

ADRF670x系列產(chǎn)品設計用于簡化用戶接口,方便與ADI最新的發(fā)送數(shù)模轉(zhuǎn)換器AD9122和GaAs放大器(如ADL5320)的連接。(ADL5320是一個0.25瓦高線性度放大器,能夠?qū)?dBm以上功率驅(qū)動進最末級功放電路。)這三個尺寸緊湊的IC構成了一個完整的有源IC器件組合,是所有下一代多載頻蜂窩無線平臺的理想之選。

-

芯片

+關注

關注

459文章

52169瀏覽量

436100 -

射頻

+關注

關注

106文章

5727瀏覽量

169729 -

晶體管

+關注

關注

77文章

9979瀏覽量

140649

發(fā)布評論請先 登錄

傳蘋果正開發(fā)下一代無線充電技術

如何利用新型Linux開發(fā)工具應對下一代嵌入式系統(tǒng)設計挑戰(zhàn)?

為什么說射頻前端的一體化設計決定下一代移動設備?

如何建設下一代蜂窩網(wǎng)絡?

下一代超快I-V測試系統(tǒng)關鍵的技術挑戰(zhàn)有哪些?

針對下一代LTE基站發(fā)射機的RF IC集成設計策略

射頻前端的一體化設計決定下一代移動設備發(fā)展

下一代無線技術是VR下一代發(fā)展的缺失環(huán)節(jié)

下一代無線產(chǎn)品設計的挑戰(zhàn)

下一代移動設備會不會實現(xiàn)射頻前端的一體化

下一代無線設備的射頻芯片設計挑戰(zhàn)

下一代無線設備的射頻芯片設計挑戰(zhàn)

評論