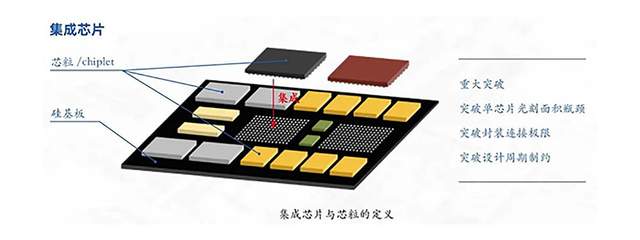

Chiplet與異構集成即將改變電子系統的設計、測試和制造方式。芯片行業的“先知”們相信這個未來是不可避免的。他們認為,相比于最新的設計節點,異構、多chiplet的架構可以降低成本和功耗。盡管這一預測得到了廣泛的接受,但問題是,大家都準備好了嗎?

前不久在舊金山的Semicon West上,Applied Materials舉行了異構集成討論會,由他們的半導體產品組的副總裁Vincent DiCaprio主持,討論了fabless芯片設計師、代工廠和生產設備公司開發的特定異構集成策略。這場對話揭示出,在市場看到更廣泛的chiplet實現之前,還存在一些重大挑戰。

Chiplet的前景吸引了許多fabless公司,尤其是那些為高性能計算解決方案開發CPU和GPU的公司。然而,高昂的成本讓Qualcomm這樣重要的玩家望而怯步。異構集成的一個大問題是先進的封裝技術,wafer-to-wafer鍵合或die-to-wafer鍵合。

代工廠或是OSAT(outsourced semiconductor assembly and test),誰來負責高級封裝技術是個大問題。這兩方將何時開始合作,如何合作?最重要的是,由于缺乏計量工具,討論組的成員們紛紛表示,推動chiplet的快速采用變得難以負擔。 小組討論包括AMD、Intel、Qualcomm、Besi和EV Group的代表。Besi是一家設計和制造半導體設備的荷蘭公司。總部位于奧地利的EV Group是晶圓鍵合和光刻設備供應商。

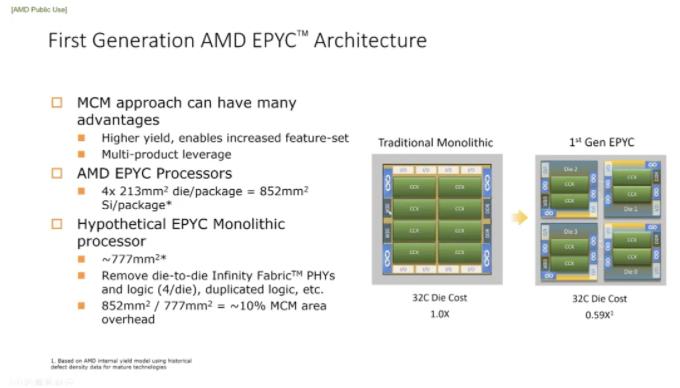

AMD:異構集成的早期采用者

AMD是異構集成的早期采用者。AMD的技術和產品工程高級副總裁Mark Fuselier將其描述為“跨越過去十年的旅程”。通過“將SoC解構成多個片段,然后在封裝中重新組合起來”,AMD首先在數據中心設計了基于Zen的CPU。

但是,“當我們開始熟悉chiplet時,我們發現其中有更多的機會。”AMD的異構集成第二代是“將內存更靠近邏輯部分”。首先是在圖形空間中使用了HBM(high bandwidth memory)。Fuselier稱之為AMD的“一個轉折點”,他解釋說最近正在讓SRAM更靠近CPU。

他指出,第三代更加令人興奮。AMD看到其未來在于“實現真正的異構集成,優化chiplet以適應CPU或GPU計算。”它已經成為了“一個架構師的夢想,能夠優化每一個計算空間中的工作負載。”

Qualcomm:移動領域中的chiplet?

當AMD利用異構集成服務于客戶端和數據中心時,Qualcomm在移動領域的定位又在哪里呢?

Qualcomm的副總裁兼研究員Chidambaram指出,“Qualcomm要想在智能手機市場上繼續生產更具競爭力的超大批量產品,我們需要超越摩爾定律的創新。”

他說:“五年前,我知道GAA將是2022年的技術。但是從現在起五年后,我不確定我們會做什么。”他強調,Qualcomm看到自己“走在橫軸和縱軸之間的二維空間里”,其中“吞吐量成為一個關鍵向量,而不是規模”。

盡管Qualcomm對chiplet思考很多,但Chidambaram表示,由于chiplet無法滿足Qualcomm的成本要求,所以還沒有相關產品。

盡管如此,隨著市場從5G轉向6G,Qualcomm看到了chiplet的潛力。他解釋說,從整體上看,一個系統有大量的射頻、電源管理和內存。Chidambaram說:“插入損耗很大,功率放大器的性能必須非常接近系統芯片的其他部分。異構集成成為將所有這些整合在一起的關鍵。”

智能手機并不是6G轉型唯一重要的領域。Chidambaram舉了十字路口的例子。“一旦你完全實施了6G,借助異構集成將延遲從現有的7-8ms降低到1-2ms,你就可以讓路邊單元完全管理十字路口,人們甚至不需要停車。”

當然。他承認,啟用這樣的功能需要“大量的基礎設施建設,才能履行所有的延遲要求和承諾,以及在路邊單元上的連接數量。”

Intel:chiplet制造所需的關鍵技術

談到異構集成,Intel擁有得天獨厚的優勢。Intel的業務涵蓋了芯片設計、內部制造和外部代工服務。

Intel的高級副總裁兼裝配/測試開發總經理Babak Sabi說:“未來,Intel看到了需要將大量的內核與內存結合……以絕對最低的延遲和最高的帶寬”,這一切都會歸結為“互連和封裝問題”。

Sabi指出,可以通過混合鍵合來堆疊芯片,這有助于減少每比特的皮焦。除了這種物理連接,“橫向集成”也是必要的,Sabi強調,以盡可能密集的方式連接芯片。他說,這一步需要創新,“超越我們在晶圓級裝配中已經擁有的技術”。

這就是玻璃基板變得極其重要的地方。Sabi說:“它讓我們能夠將這些巨大的復合體組合在一起,你可以完全消除interposer。我知道大家都喜歡銅,但銅最終會耗盡高速通信的能量。”未來在于Sabi所說的“光學領域”。

混合鍵合的現狀

無論是wafer-to-wafer還是die-to-wafer,混合鍵合都是實現chiplet高級封裝的關鍵。

BE Semiconductor Industries N.V.(Besi)的CEO Richard Blickman表示,混合鍵合中最關鍵的元素是“裝配、互連和前端之間的握手”。這個過程仍然“處于非常早期的階段”。

盡管不愿預測混合鍵合何時會在更大規模上被采用,但Blickman強調,在過去的兩年里,已經有了大批量chiplet設計的PoC。不過,他回顧說,flip chips在23年前就已推出,但多年后才成為主流,因此他建議大家耐心等待。他指出,混合鍵合需要更精確的粒子,這是設備供應商面臨的“最大的敵人之一”。設備本身必須更小。

EV Group的技術執行總監Paul Lindner指出,“我們將晶圓鍵合視為規模提升的推動器……它提供了將有源層從一個晶圓轉移到另一個晶圓的可能性,從而進入晶圓背面。”

Lindner指出,晶圓鍵合已經得到了不同的實現,包括SOI晶圓(鍵合晶圓)。另一個大量應用的例子是BSI傳感器(backside illuminatedsensor),這種傳感器可以接觸到光電二極管的背面,而不會受到布線的阻礙。他解釋說,這提高了傳感器的靈敏度。Lindner還看到3D NAND閃存正在采用混合鍵合。

混合鍵合的挑戰????????

那么,怎樣才能加快混合鍵合的應用并實現大批量生產呢?

AMD的Fuselier說,“混合鍵合的神奇之處真的在于它所能帶來的密度”,這為芯片設計者提供了更多選擇。

“作為一個架構師,我們需要弄清楚如何最好地利用這種密度來應對我們面臨的一些挑戰,無論是logic to logic,還是interconnect logic to memory。”Fuselier解釋說,還需要出現更多的創新。為此,“我們需要開發工具集來推動這種互連。”

他說,雖然晶圓廠有很多工具,但封裝方面的工具集不足以讓芯片設計者決定是否使用混合鍵合。

Intel的Sabi從制造角度闡述了混合鍵合的問題。

他指出,晶圓廠和封裝供應商之間的更緊密合作至關重要。像混合鍵合這樣的技術“真的打破了兩者之間的界限”。在眾多挑戰中,他指出,互連的密度是巨大的。“我們需要極端的粒子控制能力,才能使CMP工藝保持原狀”,這是在整個晶圓上實現這種機制所必需的。

根據Intel的說法,圍繞混合鍵合的許多挑戰可歸結為計量工具。Sabi說,“我們強調計量工具。因為我們必須要找到問題,這樣才能解決它們。”

考慮到混合鍵合模糊了傳統的前端處理和后端裝配測試之間的界限,像Qualcomm這樣的fabless巨頭需要什么呢?

Chidambaram指出,這一切都與系統級集成有關。在討論公司內部的系統集成時,他說,“負責CPU的人和其他開發射頻的人對彼此的領域了解不深。”為了實現不同領域的“協同優化”,“我們需要工具,以及人們可以在這些不同領域之間使用的語言。”

Chidambaram從三維層面詳細介紹了混合集成,他說,“你說的是創造一種后端類型的集成。要做到這一點,你需要所有的物理學來解決問題,同時還需要解決多個芯片的電氣行為。你把一個模塊從頂部移動到底部,它會改變你的熱行為、改變你的機械行為,你需要同時優化所有這些東西。”

阻礙chiplet發展的最大問題是工具集。現有的各種工具,可以分別解決一些特定的問題。但這個行業需要投資并開發能夠從三維角度解決異構集成問題的工具。

審核編輯:劉清

-

傳感器

+關注

關注

2562文章

52559瀏覽量

763670 -

電源管理

+關注

關注

117文章

6400瀏覽量

145787 -

SoC芯片

+關注

關注

1文章

636瀏覽量

35654 -

CMP

+關注

關注

6文章

152瀏覽量

26497 -

chiplet

+關注

關注

6文章

453瀏覽量

12864

原文標題:AMD、Intel與Qualcomm如何思考chiplet?

文章出處:【微信號:Astroys,微信公眾號:Astroys】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet:芯片良率與可靠性的新保障!

2.5D集成電路的Chiplet布局設計

解鎖Chiplet潛力:封裝技術是關鍵

Chiplet或改變半導體設計和制造

AMD即將推出的 Hawk Point Refresh“Ryzen 200”APU 將應對 Intel 的 Raptor Lake Refresh “Core 200”CPU

Chiplet技術有哪些優勢

AMD數據中心業務逆襲,營收首超Intel

AMD數據中心業務收入超越Intel

2035年Chiplet市場規模將超4110億美元

IMEC組建汽車Chiplet聯盟

Primemas選擇Achronix eFPGA技術用于Chiplet平臺

突破與解耦:Chiplet技術讓AMD實現高性能計算與服務器領域復興

AMD、Intel與Qualcomm如何思考chiplet?

AMD、Intel與Qualcomm如何思考chiplet?

評論