今天我們要介紹的時序分析概念是 min pulse width ,全稱為最小脈沖寬度檢查。這也是一種非常重要的timing arc check,經常用在時序器件或者memory上面。

一般情況下,由于cell本身有變異,rise和fall delay不相同,這樣可能會造成時鐘信號脈沖寬度減小。

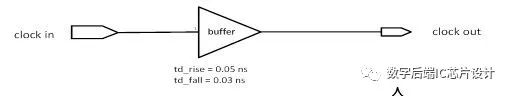

如下圖一個周期為1ns,duty cycle 為50%的clock信號

在經過一個buffer(rise delay: 0.05, fall delay:0.03)

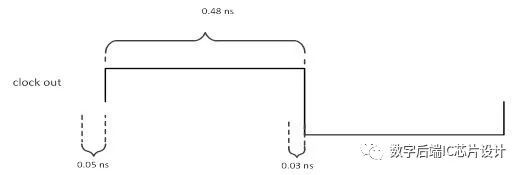

clock信號波形變成如下圖所示:

因此,可以知道,如果某個cell的rise delay大于fall delay,那么輸出時鐘的脈沖寬度要比輸入時鐘小。如果時鐘信號經過一系列相同類型的單元,則時鐘信號的脈沖寬度將會持續減小。如果小于某個最小寬度,可能會導致器件不能正常的捕獲數據。

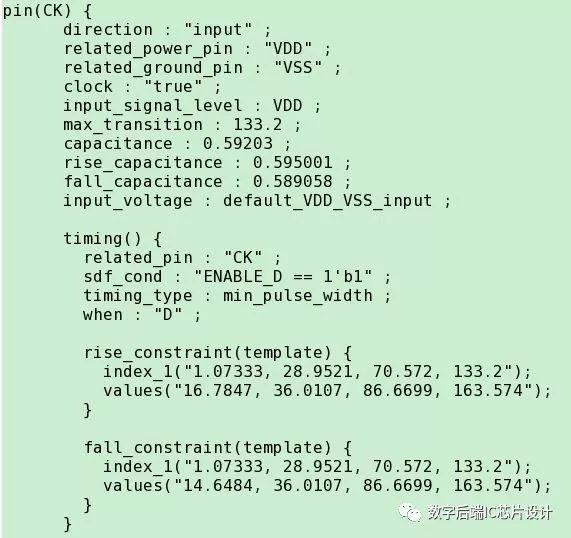

因此,在做timing分析時,我們是必須對cell的pin做min pulse width檢查。通常有兩類方法:

1) sdc里面定義

set_min_pulse_width 2.0 [get_clocks CK1]

2)library里面定義

-

時鐘信號

+關注

關注

4文章

465瀏覽量

29083 -

時序分析器

+關注

關注

0文章

24瀏覽量

5341

發布評論請先 登錄

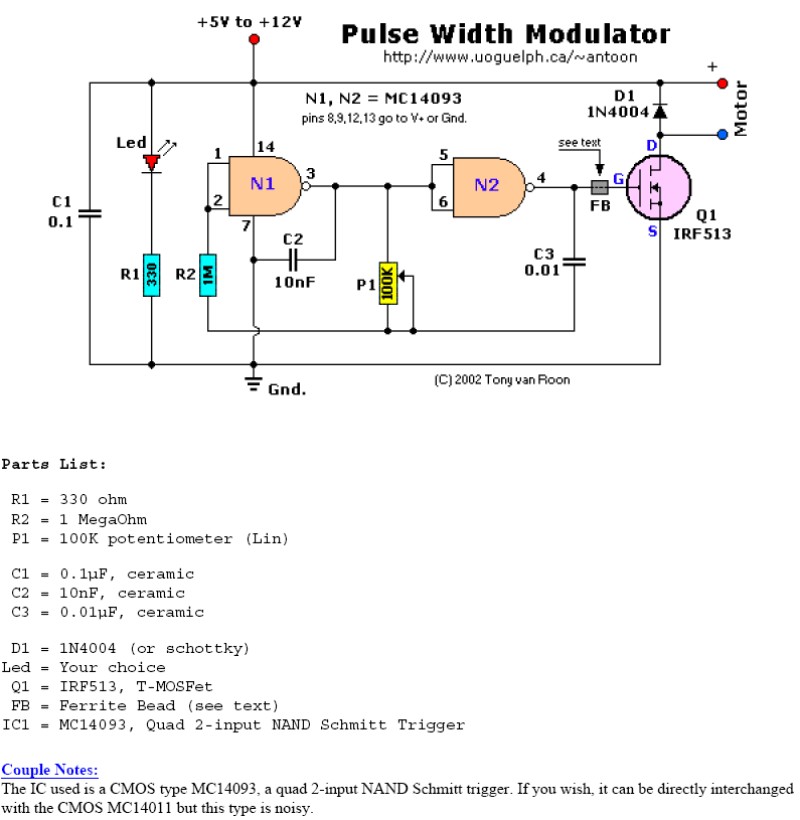

Pulse Width Modulator circuits

脈寬調制器工作在不同層次的頻率和功耗-Pulse-Width

Pulse Width Modulation

時序分析基本概念介紹

什么是Min Period檢查?

clock gate時序分析概念介紹

時序分析概念min pulse width介紹

時序分析概念min pulse width介紹

評論