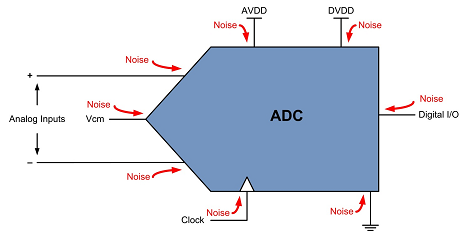

到目前為止,這是一個有趣的旅程,研究了ADC中潛在噪聲源。我們研究了模擬和數字電源輸入以及接地連接。沿著這些思路,我們還研究了PSRR和PSMR。之后,我討論了涉及ADC模擬輸入的噪聲。現在,讓我們來看看ADC上需要注意噪聲的最關鍵的地方之一——ADC時鐘輸入。

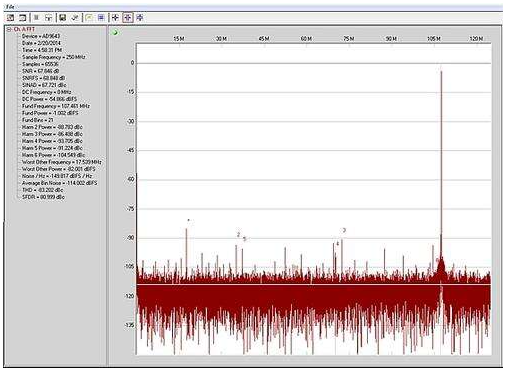

通過時鐘電路進入ADC的任何噪聲都可能直接進入輸出。ADC中涉及該電路的噪聲機制可以被認為是混頻器。在查看噪聲時以這種方式考慮此輸入確實可以正確看待事物。通過時鐘輸入進入ADC的噪聲頻率將被混入模擬輸入信號,并顯示在轉換器輸出端的FFT中。

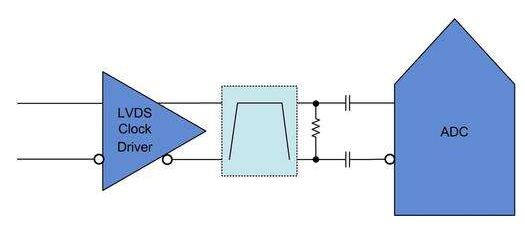

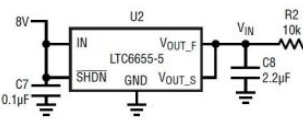

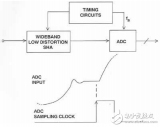

與時鐘電路和相關物理布局相關的幾點需要注意。首先,最好將時鐘驅動器放置在ADC附近,以保持布線盡可能短。時鐘信號傳播的距離越短,拾取系統中可能存在的任何錯誤噪聲的可能性就越小。盡管大多數ADC時鐘都是差分的,并且提供抗共模噪聲的能力,但并沒有完全的抗擾度。一種選擇是在ADC的時鐘頻率處添加一個中心頻率的帶通濾波器,如下圖所示。

圖1.典型ADC LVDS時鐘電路(濾波器可選)。

該濾波器應放置在靠近ADC的位置,以消除可能耦合到系統中時鐘信號的任何噪聲。最好將濾波器放置在靠近ADC的位置,因為將濾波器放置在靠近時鐘驅動器的位置,會使噪聲在濾波器之后耦合到時鐘信號上,并進入ADC。

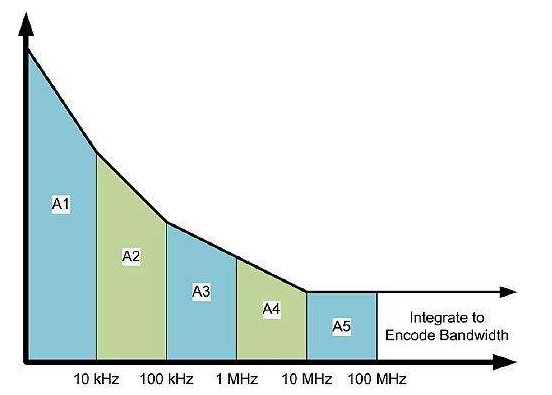

不僅要注意時鐘驅動器和ADC的放置和布線,而且考慮時鐘驅動器本身也很重要。利用良好的布局和路由技術,并選擇性地濾波時鐘信號有助于減少外部噪聲源,但不要忘記考慮時鐘源本身。選擇具有低相位噪聲的時鐘驅動器非常重要。但是,您也可以根據自己的喜好關注抖動。

審核編輯:郭婷

-

驅動器

+關注

關注

54文章

8619瀏覽量

149049 -

adc

+關注

關注

99文章

6635瀏覽量

548233 -

混頻器

+關注

關注

10文章

844瀏覽量

46644

發布評論請先 登錄

ADC輸入噪聲利弊分析

ADC時鐘輸入考慮的因素詳講

如何通過從串行接口讀取數據來向ADC14DS105提供輸入信號和時鐘

ADC噪聲:時鐘輸入和相位噪聲–測試設置

ADC噪聲:時鐘輸入和相位噪聲,第 1 部分

ADC噪聲:時鐘輸入和相位噪聲,第 2 部分

ADC噪聲:時鐘輸入如何提供幫助

ADC噪聲:時鐘輸入如何提供幫助

評論