所有模數(shù)轉(zhuǎn)換器(ADC)都有一定量的輸入?yún)⒖荚肼暎榕c無(wú)噪聲ADC輸入串聯(lián)的噪聲源。不要將折合到輸入端的噪聲與量化噪聲混淆,量化噪聲僅在ADC處理時(shí)變信號(hào)時(shí)才有意義。在大多數(shù)情況下,輸入噪聲越少越好;然而,在某些情況下,輸入噪聲實(shí)際上有助于實(shí)現(xiàn)更高的分辨率。

折合到輸入端的噪聲(代碼轉(zhuǎn)換噪聲)

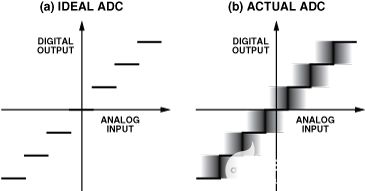

實(shí)用型ADC在許多方面都與理想ADC不同。折合到輸入端的噪聲肯定與理想值有所不同,其對(duì)整個(gè)ADC傳遞函數(shù)的影響如圖1所示。隨著模擬輸入電壓的增加,“理想”ADC(如圖1a所示)保持恒定的輸出代碼,直到到達(dá)轉(zhuǎn)換區(qū)域,此時(shí)它會(huì)立即跳轉(zhuǎn)到下一個(gè)值,一直保持在那里,直到到達(dá)下一個(gè)轉(zhuǎn)換區(qū)域。理論上完美的ADC具有零代碼轉(zhuǎn)換噪聲,轉(zhuǎn)換區(qū)域?qū)挾鹊扔诹恪?shí)際ADC具有一定數(shù)量的代碼轉(zhuǎn)換噪聲,因此具有有限的轉(zhuǎn)換區(qū)域?qū)挾取D1b顯示了代碼轉(zhuǎn)換噪聲的寬度約為<>個(gè)最低有效位(LSB)峰峰值的情況。

圖1.代碼轉(zhuǎn)換噪聲(折合到輸入端的噪聲)及其對(duì)ADC傳遞函數(shù)的影響。

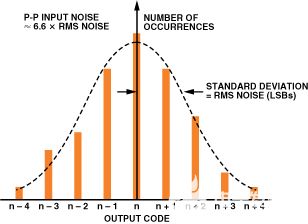

在內(nèi)部,所有ADC電路都會(huì)因電阻噪聲和“kT/C”噪聲而產(chǎn)生一定量的均方根噪聲。這種噪聲甚至對(duì)于直流輸入信號(hào)也存在,它解釋了代碼轉(zhuǎn)換噪聲,現(xiàn)在通常稱為折合到輸入端的噪聲。折合到輸入端的噪聲通常通過(guò)檢查多個(gè)輸出樣本的直方圖來(lái)表征,而ADC的輸入則保持在直流值不變。大多數(shù)高速或高分辨率ADC的輸出是代碼分布,通常以直流輸入的標(biāo)稱值為中心(見(jiàn)圖2)。

為了測(cè)量折合到輸入端的噪聲量,ADC的輸入要么接地,要么連接到高度去耦的電壓源,并收集大量輸出樣本并繪制為直方圖(如果輸入標(biāo)稱值為零伏,則稱為接地輸入直方圖)。由于噪聲近似于高斯,因此可以計(jì)算的直方圖σ的標(biāo)準(zhǔn)偏差對(duì)應(yīng)于有效輸入均方根噪聲。有關(guān)如何根據(jù)直方圖數(shù)據(jù)計(jì)算σ值的詳細(xì)說(shuō)明,請(qǐng)參閱進(jìn)一步閱讀 6。通常的做法是用LSBs均方根來(lái)表示這種均方根噪聲,對(duì)應(yīng)于以ADC滿量程輸入范圍為基準(zhǔn)的均方根電壓。如果模擬輸入范圍表示為數(shù)字或計(jì)數(shù),則輸入值(如σ)可以表示為L(zhǎng)SB數(shù)量的計(jì)數(shù)。

圖2.折合到輸入端的噪聲對(duì)具有少量DNL的ADC的ADC接地輸入直方圖的影響。

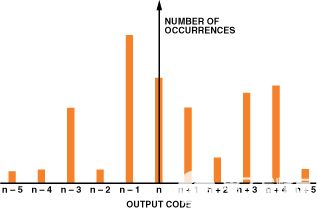

雖然ADC固有的微分非線性(DNL)會(huì)導(dǎo)致與理想高斯分布的偏差(例如,圖2中可以看到一些DNL),但它至少應(yīng)該近似于高斯分布。如果存在顯著的DNL,則應(yīng)計(jì)算幾種不同直流輸入電壓的σ值,并將結(jié)果取平均值。如果代碼分布明顯非高斯分布,例如大而明顯的峰值和谷值,這可能表明ADC設(shè)計(jì)不佳,或者更有可能表明PCB布局不佳、接地技術(shù)不良或電源去耦不當(dāng)(見(jiàn)圖3)。另一個(gè)問(wèn)題跡象是,當(dāng)直流輸入掃過(guò)ADC輸入電壓范圍時(shí),分布寬度發(fā)生劇烈變化。

圖3.接地輸入直方圖,用于設(shè)計(jì)不良的ADC和/或布局、接地或去耦不良的情況。

無(wú)噪聲(無(wú)閃爍)代碼分辨率

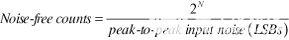

ADC的無(wú)噪聲碼分辨率是分辨率位數(shù),超過(guò)該位數(shù)就不可能明確分辨單個(gè)代碼。這種限制是由于與上述所有ADC相關(guān)的有效輸入噪聲(或折合到輸入端的噪聲)造成的,通常表示為L(zhǎng)SBs均方根單位的均方根量。乘以系數(shù)6.6可將均方根噪聲轉(zhuǎn)換為峰峰值噪聲的有用度量,即可以識(shí)別代碼的實(shí)際不確定性,以LSB的峰峰值表示。由于N位ADC的總范圍(或跨度)為2N因此,LSB,無(wú)噪聲計(jì)數(shù)的總數(shù)等于:

?

|

??? | (1) |

?

通過(guò)計(jì)算以 2 為底的對(duì)數(shù),可以將無(wú)噪聲計(jì)數(shù)的數(shù)量轉(zhuǎn)換為無(wú)噪聲(二進(jìn)制)代碼分辨率,如下所示:

?

|

??? | (2) |

?

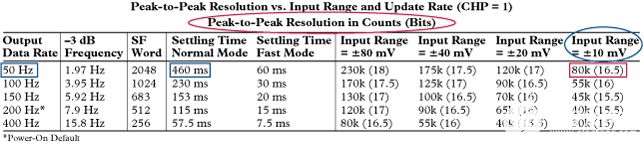

無(wú)噪聲碼分辨率規(guī)范通常與高分辨率Σ-Δ測(cè)量ADC相關(guān)。它通常是采樣速率、數(shù)字濾波器帶寬和可編程增益放大器(PGA)增益(因此輸入范圍)的函數(shù)。圖4所示為典型表格,取自AD7730 Σ-Δ型ADC的數(shù)據(jù)手冊(cè)。

圖4.AD7730 Σ-Δ型ADC的無(wú)噪聲代碼分辨率。

請(qǐng)注意,對(duì)于50 Hz的輸出數(shù)據(jù)速率和±10 mV的輸入范圍,無(wú)噪聲碼分辨率為16.5位(80,000個(gè)無(wú)噪聲計(jì)數(shù))。這些條件下的建立時(shí)間為460 ms,使該ADC成為精密電子秤應(yīng)用的理想選擇。適用于精密測(cè)量應(yīng)用的高分辨率Σ-Δ型ADC的大多數(shù)數(shù)據(jù)手冊(cè)中都提供了此類數(shù)據(jù)。

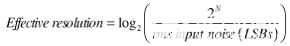

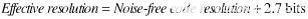

滿量程范圍與均方根輸入噪聲(而不是峰峰值噪聲)之比有時(shí)用于計(jì)算分辨率。在這種情況下,使用術(shù)語(yǔ)有效分辨率。請(qǐng)注意,在相同條件下,有效分辨率大于通過(guò)日志進(jìn)行無(wú)噪聲代碼解析2(6.6),或大約 2.7 位。

?

|

??? | (3) |

|

??? | (4) |

?

一些制造商更喜歡指定有效分辨率而不是無(wú)噪聲代碼分辨率,因?yàn)檫@會(huì)產(chǎn)生更多的位數(shù)——用戶應(yīng)仔細(xì)檢查數(shù)據(jù)手冊(cè),以確保實(shí)際指定了哪個(gè)。

數(shù)字平均可提高分辨率并降低噪聲

折合到輸入端的噪聲的影響可以通過(guò)數(shù)字平均來(lái)降低。考慮一個(gè)16位ADC,它具有15個(gè)無(wú)噪聲位,采樣速率為100 kSPS。對(duì)每個(gè)輸出樣本的不變信號(hào)進(jìn)行兩次測(cè)量平均,可將有效采樣速率降低到50 kSPS,并將SNR提高3 dB,無(wú)噪聲位數(shù)提高到15.5。對(duì)每個(gè)輸出樣本進(jìn)行四次測(cè)量的平均值可將采樣速率降低至25 kSPS,并將SNR提高6 dB,無(wú)噪聲位數(shù)提高至16 dB。

我們可以更進(jìn)一步,平均每個(gè)輸出 16 次測(cè)量;輸出采樣速率降低到6.25 kSPS,SNR又增加了6 dB,無(wú)噪聲位數(shù)增加到17 dB。平均中的算術(shù)精度必須對(duì)更多的有效位進(jìn)行,以獲得額外的“分辨率”。

平均過(guò)程還有助于消除ADC傳遞函數(shù)中的DNL誤差。對(duì)于ADC在量化級(jí)別k缺少代碼的簡(jiǎn)單情況,可以說(shuō)明這一點(diǎn)。即使由于 DNL 誤差較大而缺少代碼 k,兩個(gè)相鄰代碼 k – 1 和 k + 1 的 平均值等于 k。

因此,該技術(shù)可以有效地用于增加ADC的動(dòng)態(tài)范圍,但代價(jià)是總輸出采樣速率和額外的數(shù)字硬件。還應(yīng)注意的是,平均不會(huì)校正ADC固有的積分非線性。

現(xiàn)在,考慮一個(gè)ADC的情況,它具有極低的輸入?yún)⒖荚肼暎瑹o(wú)論采集多少樣本,直方圖都會(huì)顯示單個(gè)代碼。數(shù)字平均對(duì)這款A(yù)DC有什么作用?這個(gè)答案很簡(jiǎn)單——它什么也做不了!無(wú)論平均多少樣本,答案都是一樣的。但是,一旦向輸入信號(hào)添加了足夠的噪聲,使直方圖中有多個(gè)代碼,平均方法就會(huì)再次開(kāi)始工作。因此,有趣的是,一些少量的噪聲是好的(至少就平均方法而言);但是,輸入端的噪聲越多,實(shí)現(xiàn)相同分辨率所需的平均就越多。

不要將有效位數(shù) (ENOB) 與有效分辨率或無(wú)噪聲代碼分辨率混淆

由于術(shù)語(yǔ)的相似性,有效位數(shù)和有效分辨率通常被假定為相等。事實(shí)并非如此。

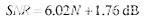

有效位數(shù)(ENOB)來(lái)自ADC被滿量程正弦波輸入信號(hào)激勵(lì)時(shí)對(duì)ADC輸出的FFT分析。計(jì)算所有噪聲和失真項(xiàng)的平方根和(RSS)值,并將信號(hào)與噪聲和失真的比定義為SINAD或S/(N+D)。完美N位ADC的理論信噪比由下式給出:

?

|

??? | (5) |

?

ENOB的計(jì)算方法是將ADC計(jì)算的SINAD代入式中的SNR,并求解方程N(yùn)。

?

|

??? | (6) |

?

用于計(jì)算SINAD和ENOB的噪聲和失真不僅包括折合到輸入端的噪聲,還包括量化噪聲和失真項(xiàng)。SINAD和ENOB用于測(cè)量ADC的動(dòng)態(tài)性能,而有效分辨率和無(wú)噪聲代碼分辨率用于測(cè)量ADC在基本直流輸入條件下的噪聲,其中量化噪聲不是問(wèn)題。

使用噪聲抖動(dòng)來(lái)增加ADC的無(wú)雜散動(dòng)態(tài)范圍

無(wú)雜散動(dòng)態(tài)范圍(SFDR)是均方根信號(hào)幅度與峰值雜散頻譜分量的均方根值之比。在高速ADC中最大化SFDR的兩個(gè)基本限制是前端放大器和采樣保持電路產(chǎn)生的失真;以及由ADC編碼器部分傳遞函數(shù)中的非線性產(chǎn)生的。實(shí)現(xiàn)高SFDR的關(guān)鍵是最小化兩個(gè)非線性源。

ADC外部無(wú)需采取任何措施,以顯著降低其前端引起的固有失真。但是,ADC編碼器傳遞函數(shù)中的差分非線性可以通過(guò)正確使用抖動(dòng)(有意與模擬輸入信號(hào)相加的外部噪聲)來(lái)降低。

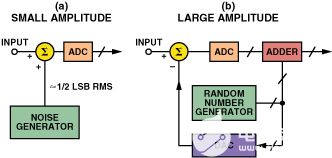

抖動(dòng)可用于在某些條件下改善ADC的SFDR(參見(jiàn)延伸閱讀2-5)。例如,即使在完美的ADC中,量化噪聲和輸入信號(hào)之間也存在一定的相關(guān)性。這種相關(guān)性會(huì)降低ADC的SFDR,特別是當(dāng)輸入信號(hào)是采樣頻率的精確子倍數(shù)時(shí)。將大約1/2 LSB rms的寬帶噪聲與輸入信號(hào)相加,往往會(huì)使量化噪聲隨機(jī)化,并將這種影響降至最低(見(jiàn)圖5a)。然而,在大多數(shù)系統(tǒng)中,已經(jīng)位于信號(hào)頂部的噪聲(包括ADC的輸入?yún)⒖荚肼暎┫藢?duì)額外抖動(dòng)噪聲的需求。將寬帶均方根噪聲水平提高到大約<>LSB以上將按比例降低SNR,并且不會(huì)帶來(lái)額外的改善。

已經(jīng)開(kāi)發(fā)了其他方案,使用大量抖動(dòng)噪聲來(lái)隨機(jī)化ADC的傳遞函數(shù)。圖5b示出了包含驅(qū)動(dòng)DAC的偽隨機(jī)數(shù)發(fā)生器的抖動(dòng)噪聲源。該信號(hào)從ADC輸入信號(hào)中減去,然后以數(shù)字方式添加到ADC輸出中,因此不會(huì)顯著降低SNR。然而,這種技術(shù)的固有缺點(diǎn)是,必須減小輸入信號(hào)擺幅,以防止隨著抖動(dòng)信號(hào)幅度的增加而過(guò)驅(qū)ADC。請(qǐng)注意,雖然該方案改善了ADC編碼器非線性產(chǎn)生的失真,但并未顯著改善其前端產(chǎn)生的失真。

圖5.使用抖動(dòng)隨機(jī)化ADC傳遞函數(shù)。

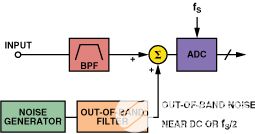

另一種更容易實(shí)現(xiàn)的方法(特別是在寬帶接收器中)是在目標(biāo)信號(hào)頻帶之外注入窄帶抖動(dòng)信號(hào),如圖6所示。通常,在直流附近的頻率范圍內(nèi)沒(méi)有信號(hào)分量,因此該低頻區(qū)域通常用于這種抖動(dòng)信號(hào)。抖動(dòng)信號(hào)的另一個(gè)可能位置略低于fS/2.抖動(dòng)信號(hào)相對(duì)于信號(hào)帶寬僅占用很小的帶寬(通常幾百kHz的帶寬就足夠了),因此SNR不會(huì)發(fā)生明顯的下降,就像抖動(dòng)是寬帶時(shí)一樣。

圖6.注入帶外抖動(dòng)以改善ADC SFDR。

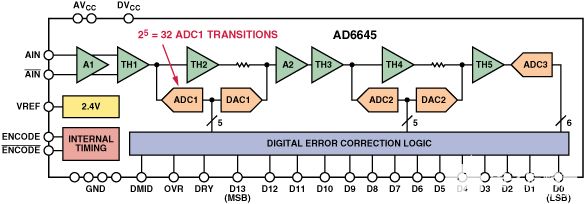

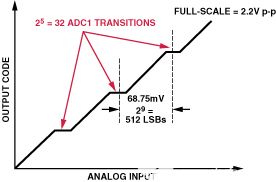

量程流水線ADC,例如6645位、14 MSPS ADC(見(jiàn)圖105)AD7,在ADC范圍內(nèi)的特定代碼轉(zhuǎn)換點(diǎn)處發(fā)生非常小的差分非線性誤差。AD6645內(nèi)置一個(gè)5位ADC (ADC1),后接一個(gè)5位ADC2和一個(gè)6位ADC3。唯一顯著的DNL誤差發(fā)生在ADC1轉(zhuǎn)換點(diǎn),第二級(jí)和第三級(jí)DNL誤差最小。有 2 個(gè)5= 32個(gè)與ADC1相關(guān)的決策點(diǎn),每68.75 mV發(fā)生一次(29= 512 LSB),適用于 2.2V 滿量程輸入范圍。圖8顯示了這些非線性的夸張表示。

圖7.AD6645 14位、105 MSPS ADC簡(jiǎn)化框圖

圖8.AD6645子量程點(diǎn)DNL誤差(夸大)。

當(dāng)模擬輸入高達(dá)約200 MHz時(shí),與編碼器產(chǎn)生的失真分量相比,AD6645前端產(chǎn)生的失真元件可以忽略不計(jì)。也就是說(shuō),AD6645傳遞函數(shù)的靜態(tài)非線性是SFDR的主要限制。

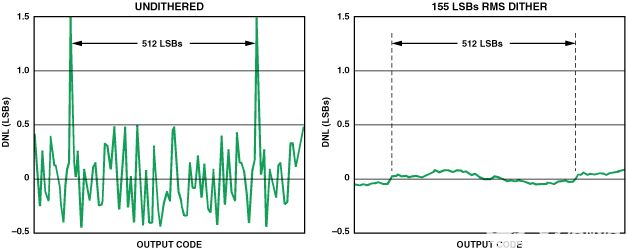

目標(biāo)是選擇適當(dāng)數(shù)量的帶外抖動(dòng),以便這些小DNL誤差的影響在整個(gè)ADC輸入范圍內(nèi)隨機(jī)化,從而降低平均DNL誤差。實(shí)驗(yàn)確定,使峰峰值抖動(dòng)噪聲覆蓋大約兩個(gè)ADC1轉(zhuǎn)換可以最好地改善DNL。隨著噪聲水平的提高,DNL沒(méi)有顯著改善。兩個(gè)ADC1轉(zhuǎn)換覆蓋1024 LSB的峰峰值,或大約155 (= 1024/6.6) LSB rms。

圖9所示的第一個(gè)圖顯示了輸入信號(hào)范圍一小部分的無(wú)抖動(dòng)DNL,包括兩個(gè)間隔為68.75 mV (512 LSB)的子量程點(diǎn)。第二張圖顯示了添加(后來(lái)濾除)155 LSB的均方根抖動(dòng)后的DNL。此抖動(dòng)量對(duì)應(yīng)于大約 –20.6 dBm。請(qǐng)注意 DNL 的顯著改進(jìn)。

圖9.AD6645 DNL圖,無(wú)抖動(dòng)和帶抖動(dòng)。

抖動(dòng)噪聲可以通過(guò)多種方式產(chǎn)生。例如,可以使用噪聲二極管,但簡(jiǎn)單地放大寬帶雙極性運(yùn)算放大器的輸入電壓噪聲可提供更經(jīng)濟(jì)的解決方案。這種方法將在別處(延伸閱讀3、4和5)中詳細(xì)描述,本文將不討論。

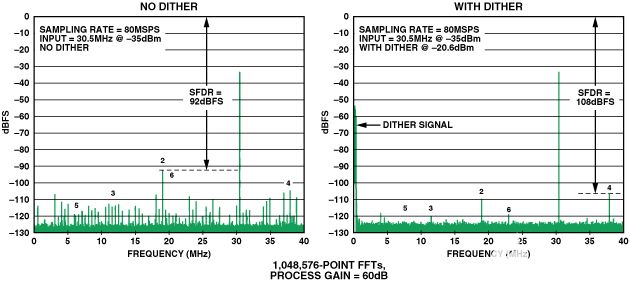

使用深(10,1,048點(diǎn))FFT時(shí),使用帶外抖動(dòng)可獲得的SFDR顯著改善,其中AD576以6645 MSPS采樣–35 dBm、30.5 MHz信號(hào)。請(qǐng)注意,沒(méi)有抖動(dòng)的SFDR約為80 dBFS,而有抖動(dòng)的SFDR約為92 dBFS,這是108 dB的實(shí)質(zhì)性改進(jìn)!

圖 10.FFT圖顯示AD6645 SFDR,沒(méi)有抖動(dòng),也沒(méi)有使用抖動(dòng)。

ADI公司于6645年推出的AD2000 ADC直到最近才代表了SFDR性能的極致。自推出以來(lái)的幾年中,工藝技術(shù)和電路設(shè)計(jì)的改進(jìn)使ADC的性能更加提高,例如AD9444(14位,80 MSPS)、AD9445(14位、105 MSPS和125 MSPS速度等級(jí))和AD9446(16位、80 MSPS和100 MSPS速度等級(jí))。 這些ADC具有非常高的SFDR(對(duì)于90 MHz滿量程輸入信號(hào),通常大于70 dBc)和低DNL。盡管如此,添加適當(dāng)?shù)膸舛秳?dòng)信號(hào)可以改善某些輸入信號(hào)條件下的SFDR。

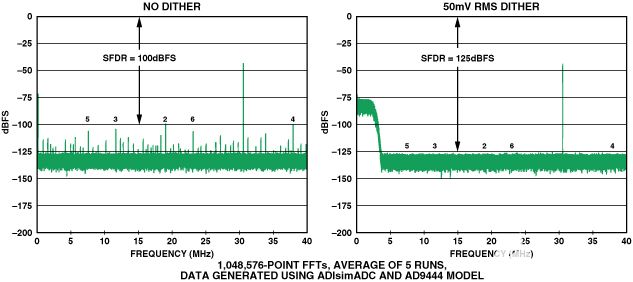

圖11對(duì)AD9444的FFT圖進(jìn)行了建模,有抖動(dòng)和不帶抖動(dòng)。可以看出,在給定的輸入條件下,增加抖動(dòng)可使SFDR提高25 dB。數(shù)據(jù)是使用ADIsimADC獲取的?程序和AD9444模型。

圖 11.AD9444 14位、80MSPS ADC;fS= 80 兆字節(jié), f在= 30.5 MHz,信號(hào)幅度 = –40 dBFS。

盡管圖10和圖11所示的結(jié)果相當(dāng)引人注目,但不應(yīng)假設(shè)增加帶外噪聲抖動(dòng)總能改善ADC在所有條件下的SFDR。我們重申,抖動(dòng)不會(huì)改善ADC前端電路的線性度。即使使用近乎理想的前端,抖動(dòng)的影響也將高度依賴于輸入信號(hào)的幅度和抖動(dòng)信號(hào)本身的幅度。例如,當(dāng)信號(hào)接近ADC的滿量程輸入范圍時(shí),傳遞函數(shù)的積分非線性可能成為決定SFDR的限制因素,抖動(dòng)將無(wú)濟(jì)于事。無(wú)論如何,都應(yīng)仔細(xì)研究數(shù)據(jù)手冊(cè)——在某些情況下,可能會(huì)顯示抖動(dòng)和未抖動(dòng)數(shù)據(jù),以及幅度和帶寬建議。抖動(dòng)可能是較新的中頻采樣ADC的內(nèi)置功能。

總結(jié)

在本討論中,我們考慮了所有ADC通用的折合到輸入端的噪聲。在精密、低頻測(cè)量應(yīng)用中,通過(guò)使用較低的采樣速率和額外的硬件對(duì)ADC輸出數(shù)據(jù)進(jìn)行數(shù)字平均,可以降低這種噪聲的影響。雖然這種平均過(guò)程實(shí)際上可以提高ADC的分辨率,但積分非線性誤差并沒(méi)有降低。只需少量的輸入?yún)⒖荚肼暭纯赏ㄟ^(guò)平均技術(shù)提高分辨率;然而,使用增加的噪聲需要在平均值中有更多的樣本,因此達(dá)到了收益遞減點(diǎn)。

在某些高速ADC應(yīng)用中,增加適量的帶外噪聲抖動(dòng)可以改善ADC的DNL并提高其SFDR。然而,抖動(dòng)在改善SFDR方面的有效性在很大程度上取決于所考慮的ADC的特性。

審核編輯:郭婷

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論