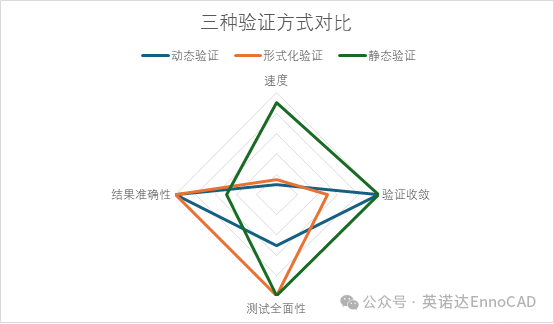

作為數字芯片設計流程中的“責任擔當”,EDA仿真驗證貫穿了芯片立項、架構定義、芯片設計到流片等環節,且在整個研發過程中占了7成左右的時間。面對日益增長的成本及市場壓力,尋找靈活的仿真驗證技術就顯得十分迫切。軟件仿真、硬件仿真及原型驗證是設計和驗證團隊在前端的常規選項,三者的搭配往往基于性能、編譯時間、設計能力和調試等的需求而定。

軟件仿真是最直接的仿真方式,設計工程師會應用硬件描述語言(HDL)來設計數字電路,也就是用軟件和編程的方式將硬件特征虛擬出來,通過計算機驗證芯片的功能正確性。因此軟件仿真可以查看電路中任何地方的信號,但一旦碰到大規模設計數字電路,結構越是復雜,仿真所需要的時間就越長。

所以通過專門的設備在硬件上調試芯片設計, 如硬件仿真和原型驗證,是其重要的解決方案之一。硬件仿真和原型驗證的效率和速度比軟件仿真可要高很多,尤其是硬件仿真,它可以對完整的芯片設計進行自動化的加速仿真并調試,多應用于芯片設計前期的RTL功能驗證。另外信號全可視是硬件仿真器的關鍵特性,因為硬件仿真中含有數量較多的探測儀器、信號記錄器等,以記錄系統電路運行的每一個時鐘周期的數據,以便查找設計錯誤。

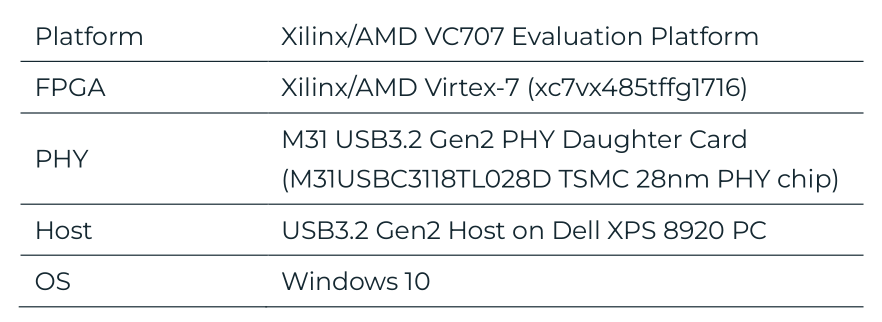

在芯片設計后期的系統級功能和性能驗證,就需要用到原型驗證。它可以為整個系統、固件以及軟件提供一個早期而真實的硬件環境,在流片之前對整個系統進行整體的性能評估和瓶頸分析。工程師將RTL代碼轉換為可編程邏輯,并部署到FPGA芯片上,即可實現原型與真實世界的數據交互,從而輕松檢測出設計中的問題。此外,原型驗證可以提供更高的性能,這意味著可以更快地執行驗證任務。而更好的軟件調試環境使得工程師可以在硬件和軟件之間進行快速切換,并通過與真實數據的交互來捕獲和解決問題。

在先進工藝下,異構計算架構正逐漸成為設計芯片的主流,不同的運算單元有不同的架構設計,對信息流也有不同的處理方式,這些都需要針對其特性使用不同驗證的方法學。為了縮短芯片的上市周期,在不同設計階段選擇不同的仿真驗證工具,提高驗證效率,如今已成了各大芯片設計公司的共識,并運用在各大芯片領域。利用異構驗證方法,多種不同形式的設計在系統建模(芯神匠),軟件仿真(芯神馳),硬件仿真(芯神鼎),原型驗證(芯神瞳)得以協同仿真和交叉驗證,以確保設計出正確的芯片。

-

芯片

+關注

關注

460文章

52515瀏覽量

440875 -

eda

+關注

關注

71文章

2929瀏覽量

177969

發布評論請先 登錄

華大九天物理驗證EDA工具Empyrean Argus助力芯片設計

芯華章攜手EDA國創中心推出數字芯片驗證大模型ChatDV

芯片的驗證為何越來越難?

芯華章以AI+EDA重塑芯片驗證效率

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】芯片如何設計

英諾達發布全新靜態驗證產品,提升芯片設計效率

芯華章推出新一代高性能FPGA原型驗證系統

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統

英諾達推出兩款全新靜態驗證EDA工具

數字芯片設計驗證經驗分享文章 實際案例說明用基于FPGA的原型來測試、驗證和確認IP——如何做到魚與熊掌兼

EDA硬核科普|異構驗證:整合三大數字芯片驗證工具,顯著縮短芯片開發周期

EDA硬核科普|異構驗證:整合三大數字芯片驗證工具,顯著縮短芯片開發周期

評論