引言

隨著AI、HPC及超大規(guī)模芯片設計需求呈指數(shù)級增長原型驗證平臺已成為芯片設計流程中驗證復雜架構、縮短迭代周期的核心工具。然而,傳統(tǒng)原型驗證系統(tǒng)受限于單芯片容量(通常<5000萬門)、多芯片分割效率及系統(tǒng)級聯(lián)能力,難以支撐上億門級以上設計的全場景驗證需求。

為應對這一挑戰(zhàn),行業(yè)亟需兼具超大規(guī)模容量、高效分割算法與跨芯片級聯(lián)能力的下一代原型驗證。AMD Versal Premium VP1902自適應SoC憑借單核等效1億門容量,成為構建高性能仿真與原型驗證系統(tǒng)的理想硬件底座。思爾芯芯神瞳邏輯系統(tǒng)S8-100通過搭載AMD VP1902,并配套自主研發(fā)的智能分割工具鏈,顯著提升超大規(guī)模設計的原型驗證效率。本文以芯神瞳邏輯系統(tǒng)S8-100與芯神瞳邏輯矩陣 LX2(采用VU19P)在多芯片級聯(lián)場景下的性能數(shù)據(jù)對比,揭示S8-100在容量、速度的顯著優(yōu)勢。

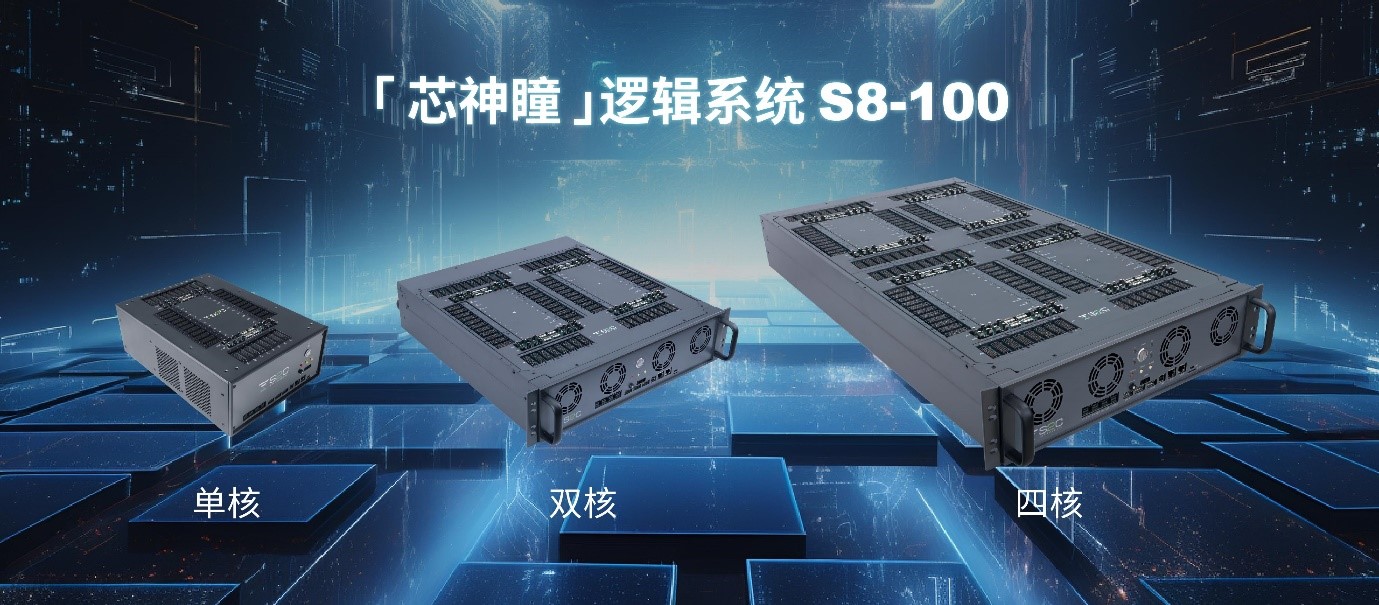

芯神瞳邏輯系統(tǒng)S8-100自去年上市以來,憑借其卓越的性能表現(xiàn)獲得了國內外頭部芯片設計廠商的廣泛采用。作為新一代原型驗證解決方案,S8-100系列提供靈活的單核、雙核及四核配置,可全面滿足從邊緣計算到數(shù)據(jù)中心等不同規(guī)模的AI和HPC芯片設計驗證需求。通過搭載AMD Versal Premium VP1902,S8-100單核即可提供約1億等效邏輯門的容量,較思爾芯上一代產(chǎn)品實現(xiàn)兩倍的容量提升。同時,其創(chuàng)新的多系統(tǒng)級聯(lián)架構能夠輕松應對超大規(guī)模芯片設計的驗證挑戰(zhàn)。

在當今超大規(guī)模芯片驗證領域,單純比較單顆FPGA的性能指標已無法反映實際工程需求。隨著AI和HPC芯片設計規(guī)模普遍突破上億門級,多FPGA分割驗證已成為行業(yè)標配。為此,我們針對思爾芯S8-100與傳統(tǒng)VU19P方案進行了系統(tǒng)級對比測試。

a)為驗證不同架構對超大規(guī)模設計驗證效率的影響,我們基于以下硬件平臺進行對比:

- S8-100Q:搭載 4顆AMD Versal VP1902 FPGA,單顆VP1902等效容量約1億門,通過FPGA級聯(lián),總容量高達4億門。

- LX2:采用 8顆AMD VU19P FPGA 級聯(lián),單顆VU19P等效容量約5000萬門,總容量與S8-100Q相當。

b)同時測試環(huán)境嚴格保持一致:

- 使用思爾芯配套軟件PlayerPro-CT(2024.2)進行設計組網(wǎng)與自動分割,先組網(wǎng)后分割

- 使用Vivado2024.2完成物理實現(xiàn)

- 完全使用軟件自動分割,啟用統(tǒng)一優(yōu)化策略:TDM感知、自動全局優(yōu)化等

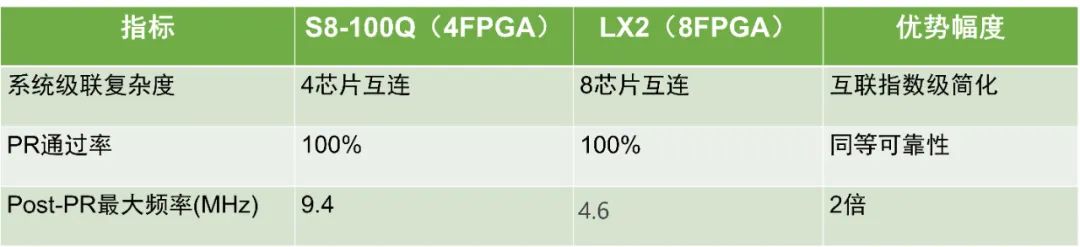

c)關鍵性能指標對比如下圖所示:

時序性能方面,S8-100和LX2在Pre-PR和Post-PR階段均保持穩(wěn)定性能,其中,S8平臺的最高頻率達到S7平臺的2倍左右。在工程效率方面,S8-100系統(tǒng)優(yōu)勢顯著:互聯(lián)結構更簡單,拓撲需求更少,接口和線纜配置更簡潔,大大提升了調試效率和工程實施便捷性。

S8-100的卓越性能源于三大關鍵優(yōu)化:

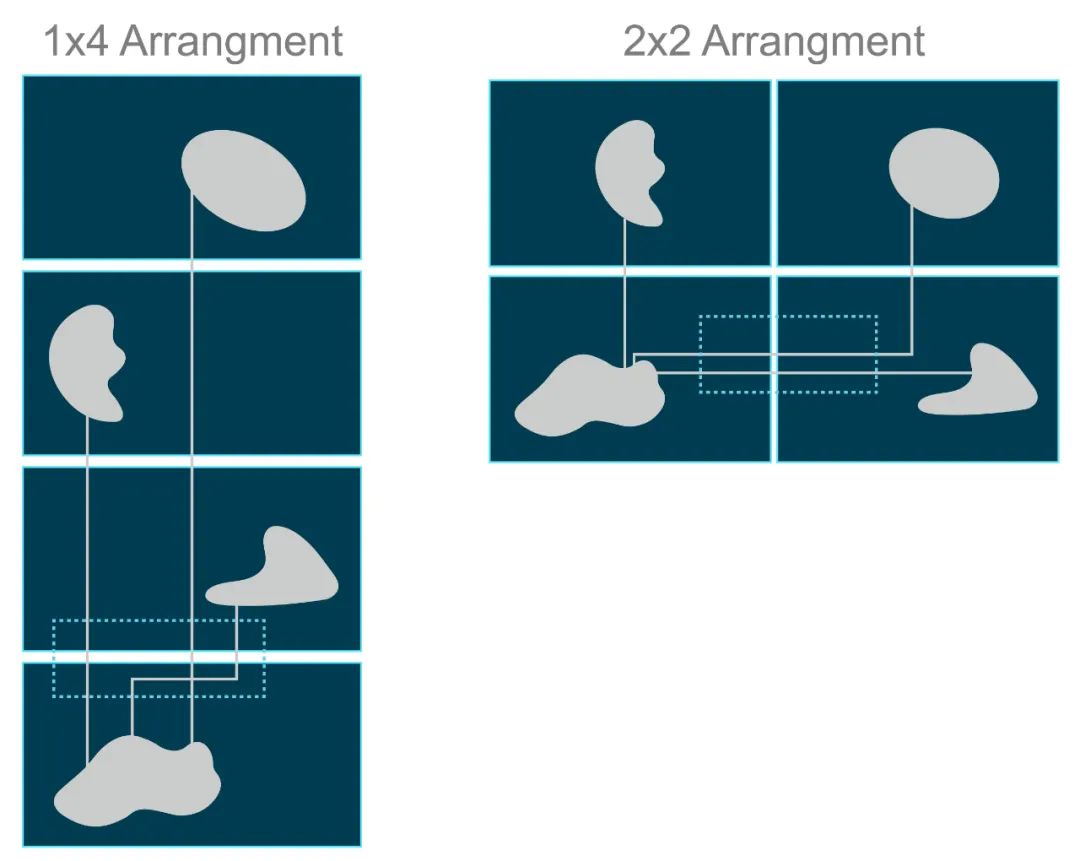

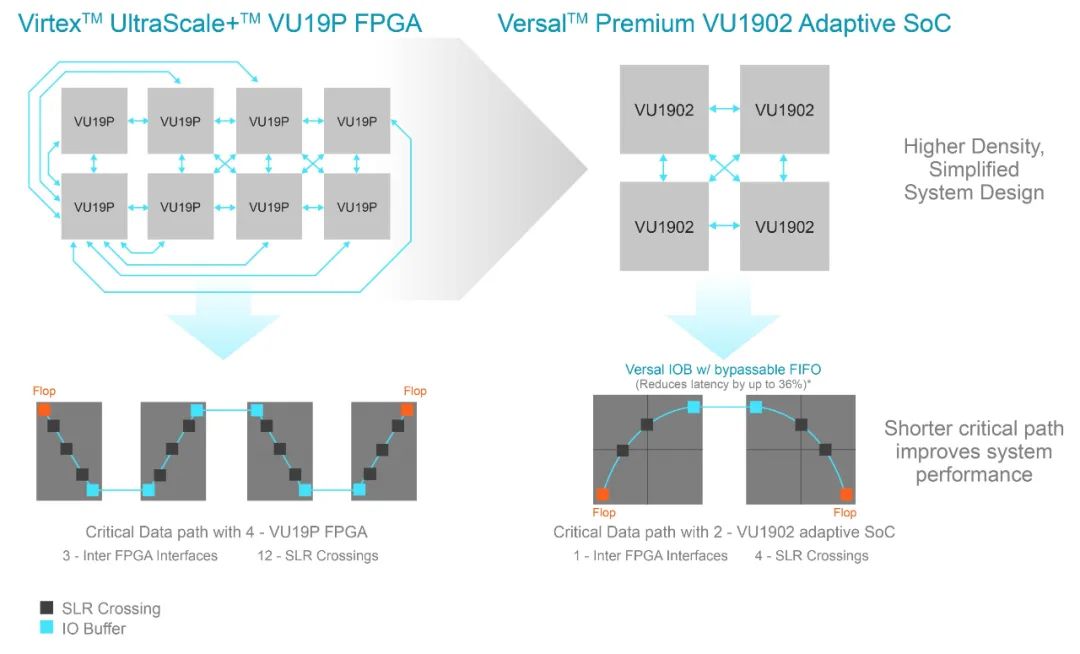

- 架構優(yōu)化:采用改進的布線架構,支持更大規(guī)模器件。器件尺寸提升2倍,單顆芯片可集成更多設計。Die采用2x2排列,最遠路徑從3階縮短至2階,減少性能損耗。

- 級聯(lián)優(yōu)化:VP1902容量擴大后分割更高效,SLR(超長線資源)跨區(qū)減少,互聯(lián)簡化,F(xiàn)PGA跨區(qū)整體大幅降低。

- I/O優(yōu)化:I/O延遲僅為UltraScale+架構的64%

這些優(yōu)化共同實現(xiàn)了S8-100在性能和效率上的突破性提升。

值得一提的是,兩款產(chǎn)品均配備了完整的工具鏈,尤其在分割軟件方面實現(xiàn)了創(chuàng)新升級。該分割軟件具備自動分割功能,透過全自動時序驅動分割,一鍵實現(xiàn)從RTL到Bitstream自動生成,跑出了一個基準之后,可再手動調整進行迭代優(yōu)化,從而大幅提升驗證效率,為復雜芯片設計提供了高效可靠的驗證解決方案。

作為思爾芯芯神瞳邏輯系統(tǒng)的最新旗艦產(chǎn)品,S8-100通過搭載AMD VP1902,為超大規(guī)模芯片設計提供了卓越的解決方案。該系統(tǒng)專為復雜SoC設計優(yōu)化,具備三大核心優(yōu)勢:首先,其強大的容量與處理能力可直接應對超大規(guī)模設計需求,顯著降低設計復雜度;其次,經(jīng)過深度優(yōu)化的工具鏈可大大節(jié)省開發(fā)時間,大幅提升工程效率;第三,經(jīng)過一年多的市場驗證,該系統(tǒng)已在多個先進工藝節(jié)點項目中成功應用,服務了眾多行業(yè)領先客戶,其穩(wěn)定性和可靠性得到了充分驗證。這一成熟穩(wěn)定的解決方案,正在為全球芯片設計企業(yè)提供更高效、更可靠的驗證平臺選擇。

-

amd

+關注

關注

25文章

5566瀏覽量

135916 -

芯片驗證

+關注

關注

5文章

38瀏覽量

47541 -

驗證系統(tǒng)

+關注

關注

0文章

27瀏覽量

10237

發(fā)布評論請先 登錄

CMOS超大規(guī)模集成電路制造工藝流程的基礎知識

納微半導體推出12kW超大規(guī)模AI數(shù)據(jù)中心電源

西門子EDA邀您相約2025玄鐵RISC-V生態(tài)大會

新思科技推出基于AMD芯片的新一代原型驗證系統(tǒng)

新思科技推出全新硬件輔助驗證產(chǎn)品組合

新思科技全新升級業(yè)界領先的硬件輔助驗證產(chǎn)品組合,助力下一代半導體與設計創(chuàng)新

Cadence推出新一代驗證系統(tǒng)

思爾芯第八代原型驗證系統(tǒng)獲國內外頭部廠商青睞

思爾芯第八代原型驗證S8-100全系已獲客戶部署,雙倍容量加速創(chuàng)新

思爾芯第八代原型驗證S8-100全系已獲客戶部署,雙倍容量加速創(chuàng)新

解鎖SoC “調試”挑戰(zhàn),開啟高效原型驗證之路

快速部署原型驗證:從子卡到調試的全方位優(yōu)化

谷歌正在考慮在越南建設超大規(guī)模數(shù)據(jù)中心

形式驗證如何加速超大規(guī)模芯片設計?

超大規(guī)模芯片驗證:基于AMD VP1902的S8-100原型驗證系統(tǒng)實測性能翻倍

超大規(guī)模芯片驗證:基于AMD VP1902的S8-100原型驗證系統(tǒng)實測性能翻倍

評論