本期開發(fā)筆記由費(fèi)神編寫主要會(huì)為大家介紹HPM6000系列的各類片上SRAM并結(jié)合Segger Embedded Studio的linker文件介紹,提供了如何使用這些SRAM的建議,趕快來(lái)了解吧~

簡(jiǎn)介

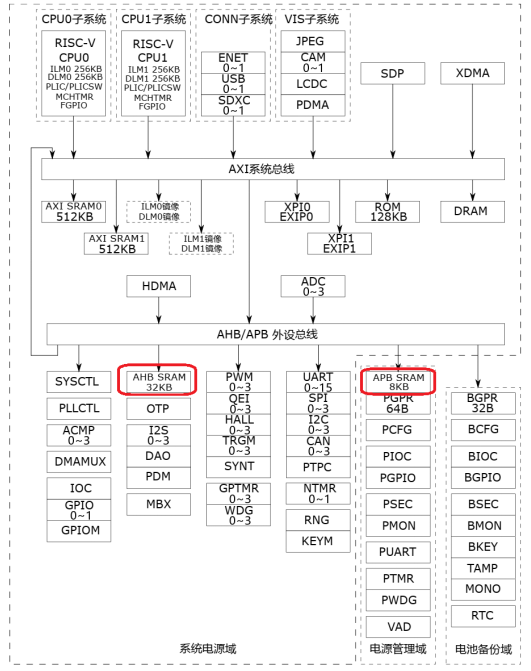

在HPM6000系列微控制器上,集成了大容量的SRAM,可供用戶存放代碼,數(shù)據(jù)等,滿足各類應(yīng)用的需要。其中片上SRAM有多種分類,包括RISC-V CPU的指令和數(shù)據(jù)本地存儲(chǔ)器ILM,DLM,通用內(nèi)存AXI SRAM,AHB SRAM等,還包括AHB SRAM,APB SRAM等。這些SRAM的最高訪問(wèn)頻率不同,數(shù)據(jù)保持的條件也不同,恰當(dāng)?shù)厥褂盟麄儯梢詷O大的提升用戶應(yīng)用的效率。

片上SRAM介紹

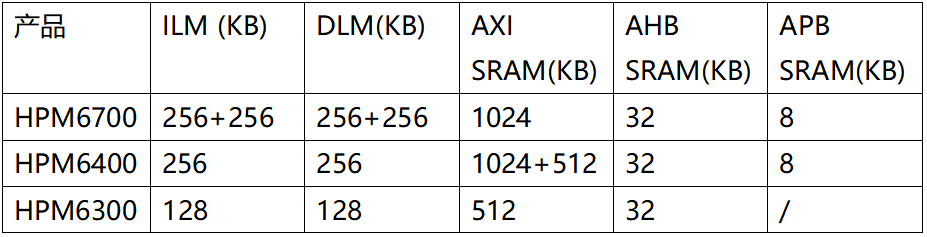

HPM6000系列高性能MCU均集成了大容量片上SRAM,總結(jié)如下:

HPM6000系列片上SRAM總結(jié)2.1 RISC-V CPU的本地存儲(chǔ)器ILM和DLM

HPM6000系列片上SRAM總結(jié)2.1 RISC-V CPU的本地存儲(chǔ)器ILM和DLM

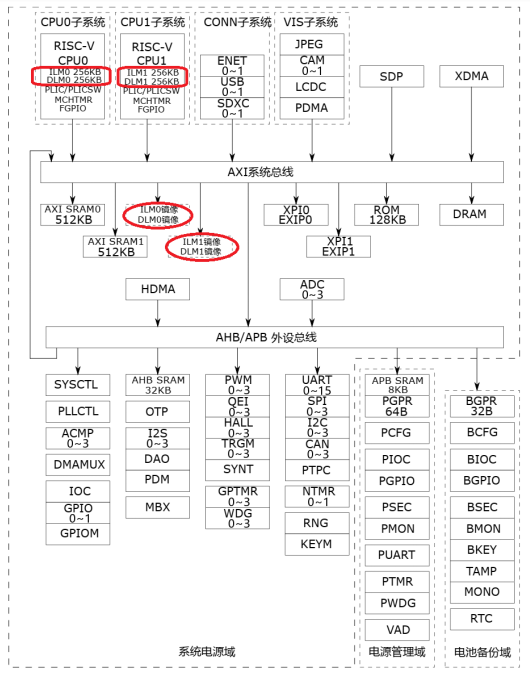

HPM6000系列高性能微控制器的RISC-V CPU都包含有指令和本地存儲(chǔ)器,分別稱為ILM(Instruction Local Memory,指令本地存儲(chǔ)器)和DLM(Data Local Memory,數(shù)據(jù)本地存儲(chǔ)器)。如下圖所示,RISC-V CPU的ILM和DLM各自對(duì)應(yīng)了內(nèi)存映射表(Memory Map)中的2塊地址映射區(qū)域。 HPM6700系列ILM/DLM示意圖ILM的映射有:

HPM6700系列ILM/DLM示意圖ILM的映射有:

ILM,以HPM6700系列為例,容量256 KB,地址范圍為0x00000000 ~ 0x0003FFFF。該地址區(qū)域只有RISC-V CPU可以通過(guò)自身的ILM接口訪問(wèn),RISC-V CPU從ILM取指時(shí),可以實(shí)現(xiàn)零等待周期,即ILM的訪問(wèn)時(shí)鐘頻率,與RISC-V CPU主頻一致,并且RISC-V CPU的一級(jí)高速指令緩存I-Cache-L1對(duì)ILM無(wú)效。CPUx_ILM_SLV,以HPM6700系列的CPU0 ILM為例,容量256 KB,地址范圍為0x01000000 ~ 0x0103FFFF。該地址區(qū)域也稱為ILM0鏡像,該地址區(qū)域可以供總線上所有的主設(shè)備訪問(wèn),如DMA等,包括RISC-V CPU自身,也可以通過(guò)CPUx_ILM_SLV訪問(wèn)ILM。如圖所示,CPUx_ILM_SLV是AXI系統(tǒng)總線的從接口,其訪問(wèn)時(shí)鐘頻率與總線時(shí)鐘頻率一致。RISC-V CPU訪問(wèn)CPUx_ILM_SLV時(shí),一級(jí)高速指令緩存I-Cache-L1是有效的。

DLM的映射有:DLM,以HPM6700系列為例,容量256 KB,地址范圍為0x00080000 ~ 0x000BFFFF。該地址區(qū)域只有RISC-V CPU可以通過(guò)自身的DLM接口訪問(wèn),RISC-V CPU從DLM讀寫數(shù)據(jù)時(shí),可以實(shí)現(xiàn)零等待周期,即DLM的訪問(wèn)時(shí)鐘頻率,與RISC-V CPU主頻一致,并且RISC-V CPU的一級(jí)高速指令緩存D-Cache-L1對(duì)DLM無(wú)效。CPUx_DLM_SLV,以HPM6700系列的CPU0 DLM為例,容量256 KB,地址范圍為0x01040000 ~ 0x0107FFFF。該地址區(qū)域也稱為ILM0鏡像,該地址區(qū)域可以供總線上所有的主設(shè)備訪問(wèn),如DMA等,包括RISC-V CPU自身,也可以通過(guò)CPUx_DLM_SLV訪問(wèn)ILM。如圖所示,CPUx_DLM_SLV是AXI系統(tǒng)總線的從接口,其訪問(wèn)時(shí)鐘頻率于總線時(shí)鐘頻率一致。RISC-V CPU訪問(wèn)CPUx_DM_SLV時(shí),一級(jí)高速指令緩存D-Cache-L1是有效的。

2.1.1HPM6700系列

HPM6700系列微控制器上,指令/數(shù)據(jù)本地存儲(chǔ)器的2塊地址映射xLM和CPUx_xLM_SLV雖然地址不同,但訪問(wèn)的是同一塊物理內(nèi)存,RISC-V CPU可以通過(guò)xLM訪問(wèn)自身的指令/數(shù)據(jù)本地存儲(chǔ)器,而其他總線主設(shè)備,比如DMA,需要通過(guò)CPUx_xLM_SLV來(lái)訪問(wèn)CPUx的指令/數(shù)據(jù)本地存儲(chǔ)器。注意,RISC-V CPU本身,也可以通過(guò)CPUx_xLM_SLV訪問(wèn)自己的指令/數(shù)據(jù)本地存儲(chǔ)器。

HPM6700系列支持雙核RISC-V CPU,CPU從xLM地址映射總是訪問(wèn)到自身指令/數(shù)據(jù)本地存儲(chǔ)器,而從CPUx_xLM_SLV可以訪問(wèn)到自身或者另一個(gè)CPU的指令/數(shù)據(jù)本地存儲(chǔ)器。

以HPM6700系列RISC-V CPU0為例,從0x00000000和0x01000000讀取到的,是CPU0指令本地存儲(chǔ)器ILM0的首地址。從0x01180000讀到的,是CPU1指令本地存儲(chǔ)器ILM1的首地址。

以RISC-V CPU1為例,從0x00000000和0x01180000讀取到的,是CPU1指令本地存儲(chǔ)器ILM1的首地址。從0x01000000讀到的,是CPU0指令本地存儲(chǔ)器ILM0的首地址。

2.1.2HPM6300系列

HPM6300系列為單核RISC-V CPU,RISC-V CPU和其他總線主設(shè)備都可以通過(guò)xLM地址映射訪問(wèn)CPU的指令/數(shù)據(jù)本地存儲(chǔ)器,其中RISC-V CPU仍然可以通過(guò)自身的xLM接口對(duì)xLM實(shí)現(xiàn)零等待周期訪問(wèn),即xLM的讀寫時(shí)鐘頻率與CPU的時(shí)鐘同頻。而其他總線主設(shè)備,需要以AXI系統(tǒng)總線的時(shí)鐘頻率訪問(wèn)xLM。

同時(shí),xLM的鏡像,CPUx_xLM_SLV映射仍然有效,包括RISC-V CPU在內(nèi)的所有總線主設(shè)備,訪問(wèn)CPUx_xLM_SLV與訪問(wèn)xLM效果相同,訪問(wèn)的是同一塊物理內(nèi)存。注意RISC-V CPU通過(guò)CPUx_xLM_SLV訪問(wèn)自身的xLM時(shí),會(huì)和其他總線主設(shè)備一樣,讀寫時(shí)鐘頻率與AXI系統(tǒng)總線時(shí)鐘頻率一致,不再支持零周期等待,但是CPU的高速一級(jí)緩存會(huì)生效。

比如,RISC-V CPU和DMA,從0x00000000讀取到的,是CPU0指令本地存儲(chǔ)器ILM0的首地址。從0x01000000讀取到的,也是CPU0指令本地存儲(chǔ)器ILM0的首地址。注意RISC-V CPU從0x01000000取值后,如果高速緩存打開,其數(shù)據(jù)會(huì)被存入緩存。

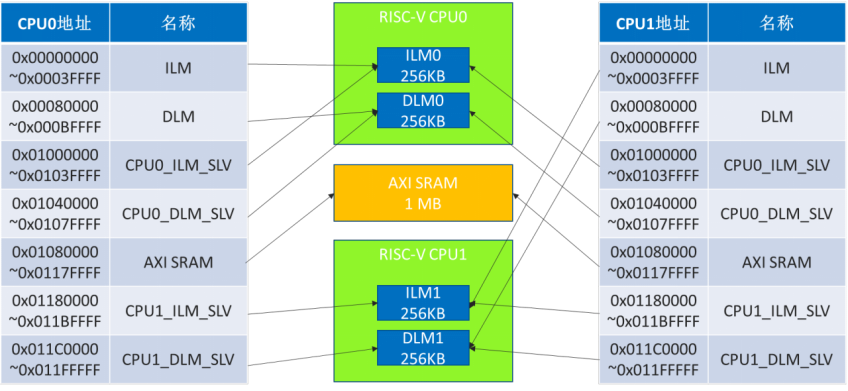

2.2AXI總線SRAM

HPM6000系列高性能MCU支持通用的片上SRAM,稱為AXI SRAM,可以用來(lái)存放數(shù)據(jù)或者代碼。

HPM6700系列AXI?SRAM示意圖上圖以HPM6700系列MCU為例,展示了AXI SRAM在系統(tǒng)中的位置。顧名思義,AXI SRAM連接到AXI系統(tǒng)總線的從接口,它的讀寫時(shí)鐘頻率就是AXI系統(tǒng)總線的時(shí)鐘頻率。所有的AXI系統(tǒng)總線主設(shè)備都可以訪問(wèn)AXI SRAM。

HPM6700系列AXI?SRAM示意圖上圖以HPM6700系列MCU為例,展示了AXI SRAM在系統(tǒng)中的位置。顧名思義,AXI SRAM連接到AXI系統(tǒng)總線的從接口,它的讀寫時(shí)鐘頻率就是AXI系統(tǒng)總線的時(shí)鐘頻率。所有的AXI系統(tǒng)總線主設(shè)備都可以訪問(wèn)AXI SRAM。

注意:系統(tǒng)內(nèi)存映射表上,AXI SRAM的地址映射與RISC-V CPU的ILM/DLM鏡像映射CPUx_xLM_SLV在地址上是連續(xù)的。因此可以把AXI SRAM和RISC-V CPU的本地存儲(chǔ)器當(dāng)作一塊聯(lián)系的大內(nèi)存使用。詳情請(qǐng)參考后文的SRAM使用建議。

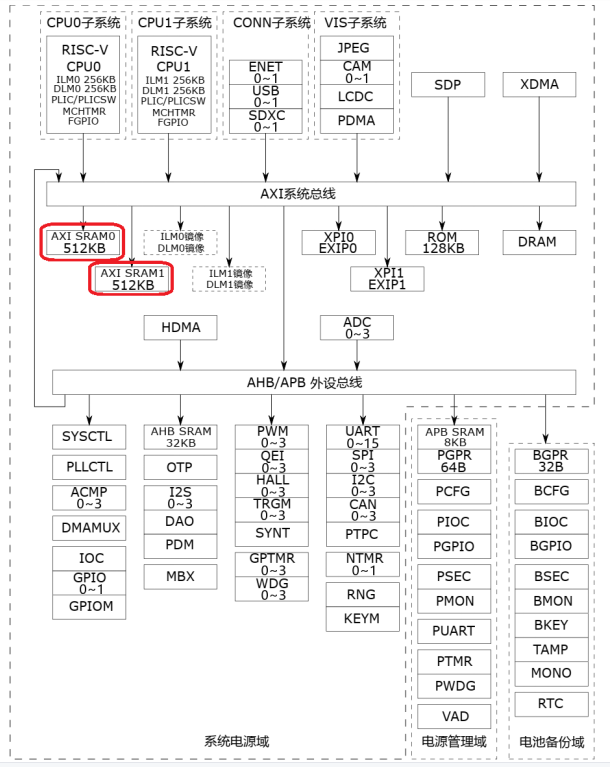

2.3AHB總線SRAM

HPM6000系列高性能MCU包含掛載在外設(shè)總線AHB的片上SRAM,稱為AHB SRAM,如下圖所示,AHB SRAM連接到AHB外設(shè)總線的從設(shè)備接口。

AHB SRAM的讀寫時(shí)鐘頻率為AHB外設(shè)總線的時(shí)鐘頻率。注意,包括RISC-V CPU在內(nèi)的總線主設(shè)備需要通過(guò)AXI系統(tǒng)總線,來(lái)訪問(wèn)AHB外設(shè)總線下的各個(gè)外設(shè)寄存器。而外設(shè)總線AHB上的主設(shè)備,比如HDMA,可以直接通過(guò)AHB總線訪問(wèn)外設(shè)寄存器,以及AHB SRAM。因此AHB SRAM比其他類型的片上SRAM更適合用作寄存器和SRAM之間的數(shù)據(jù)搬運(yùn)。基于同樣的理由,HDMA也比XDMA更適合用作AHB SRAM和寄存器之間的數(shù)據(jù)搬運(yùn)。

因此,當(dāng)使用HDMA用作通訊接口,如UART,SPI的數(shù)據(jù)收發(fā)時(shí),推薦使用AHB SRAM作為數(shù)據(jù)的緩沖區(qū)。 HPM6700系列AHB?SRAM和APB?SRAM示意圖

HPM6700系列AHB?SRAM和APB?SRAM示意圖

2.4APB總線SRAM

HPM6000系列高性能MCU的部分型號(hào)支持APB SRAM。上圖以HPM6700系列MCU為例,展示了APB SRAM在系統(tǒng)中的位置。

APB SRAM位于電源管理域,由VPMC引腳供電。當(dāng)MCU處于低功耗模式時(shí),有可能通過(guò)關(guān)閉系統(tǒng)電源域的電源,使得VDD_SOC掉電。此時(shí),APB SRAM可以作為片上的備份SRAM,保存必要的數(shù)據(jù)。

注意,對(duì)于不支持APB SRAM的型號(hào),可以使用電源管理域通用寄存器PGPR,保存一定的備份數(shù)據(jù)。

在電池模式(VBAT Only Mode)下,VPMC也掉電,HPM6000系列MCU僅VBAT保持供電。此時(shí),電池備份域通用寄存器BGPR,可以用來(lái)保存一定的備份數(shù)據(jù)。

-

mcu

+關(guān)注

關(guān)注

146文章

17851瀏覽量

360685

發(fā)布評(píng)論請(qǐng)先 登錄

支持HPM6P00/HPM5E00系列!HPMicro Manufacturing Tool v0.6.0發(fā)布

【強(qiáng)勢(shì)上新】HPM5E00:EtherCAT運(yùn)動(dòng)控制MCU,先楫半導(dǎo)體再拓工業(yè)總線產(chǎn)品新版圖

【強(qiáng)勢(shì)上新】HPM5E00:EtherCAT運(yùn)動(dòng)控制MCU,先楫半導(dǎo)體再拓工業(yè)總線產(chǎn)品新版圖

淺談MCU片上RAM

重磅更新 | 先楫半導(dǎo)體HPM_SDK v1.9.0 發(fā)布

開發(fā)者分享 | 適用于HPM的RustSBI實(shí)現(xiàn)

關(guān)于hpm6364的femc同時(shí)使用外接sdram和sram的問(wèn)題

TMS320C6000 EMIF轉(zhuǎn)外部異步SRAM接口

66AK2Hx片上系統(tǒng)(SoC)器件系列的功耗摘要

Keysight InfiniiVision 6000 X 系列示波器

支持HPM6E00!HPMicro Pintool Web v0.3.1正式上線!

應(yīng)用分享| HPM6000系列片上SRAM揭秘

應(yīng)用分享| HPM6000系列片上SRAM揭秘

評(píng)論