隨著我國傳統產業(yè)結構升級的加速,人們對設備越來越高的應用需求已無法滿足當前和未來高性能的應用與發(fā)展需求。同時,激烈的市場競爭和技術競爭,要求產品的開發(fā)周期越來越短,顯然,嵌入式系統的軟、硬件技術和開發(fā)手段,正日益受到重視,成為各領域技術創(chuàng)新的重要基礎。

根據IEEE(國際電氣和電子工程師協會)的定義,嵌入式系統是“控制、監(jiān)視或者輔助設備、機器和車間運行的裝置”。

目前國內一個普遍被認同的定義是:以應用為中心、以計算機技術為基礎,軟件硬件可裁剪,適應應用系統對功能、可靠性、成本、體積、功耗嚴格要求的專用計算機系統。

與通用計算機系統的不同:嵌入式系統是不同于常見計算機系統的一種計算機系統,它不以獨立設備的物理形態(tài)出現,嵌入式系統的部件根據主體設備及其應用的需要,嵌入在主體設備內部,發(fā)揮著運算、處理、存儲及控制的作用,是“用于控制、監(jiān)視或者輔助操作機器和設備的裝置”。

可以這樣認為,嵌入式系統是一種專用的計算機系統,作為裝置或設備的一部分。嵌入式系統一般由嵌入式微處理器、外圍硬件設備、嵌入式操作系統以及用戶應用程序4個部分組成。“嵌入性”、“專用性”與“計算機系統”是嵌入式系統的三個基本要素,對象系統則是指嵌入式系統所嵌入的宿主系統。

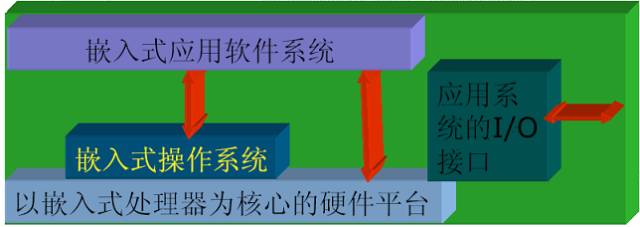

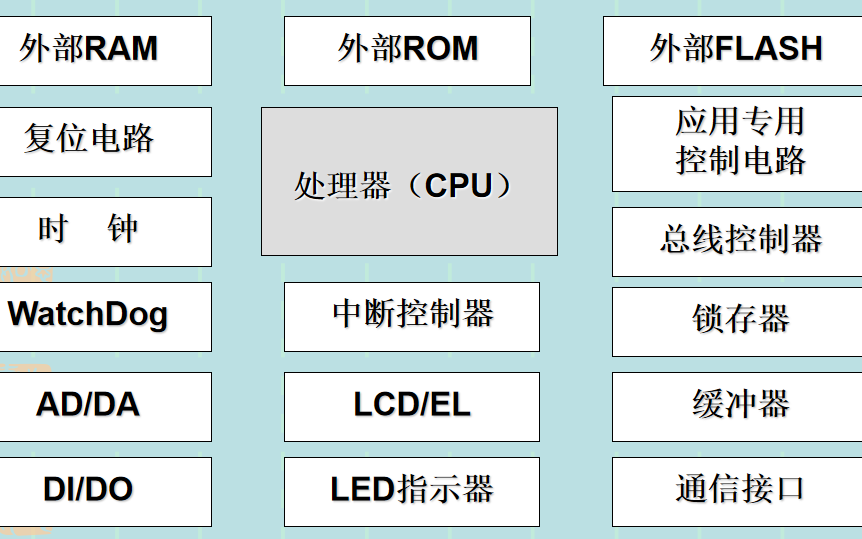

嵌入式系統的組成

嵌入式系統通常由包含有嵌入式處理器、嵌入式操作系統、應用軟件和外圍設備接口的嵌入式計算機系統和執(zhí)行裝置(被控對象)組成。嵌入式計算機系統是整個嵌入式系統的核心,可以分為硬件層、中間層、系統軟件層和應用軟件層。執(zhí)行裝置接受嵌入式計算機系統發(fā)出的控制命令,執(zhí)行所規(guī)定的操作或任務。

1.嵌入式計算機系統的硬件層

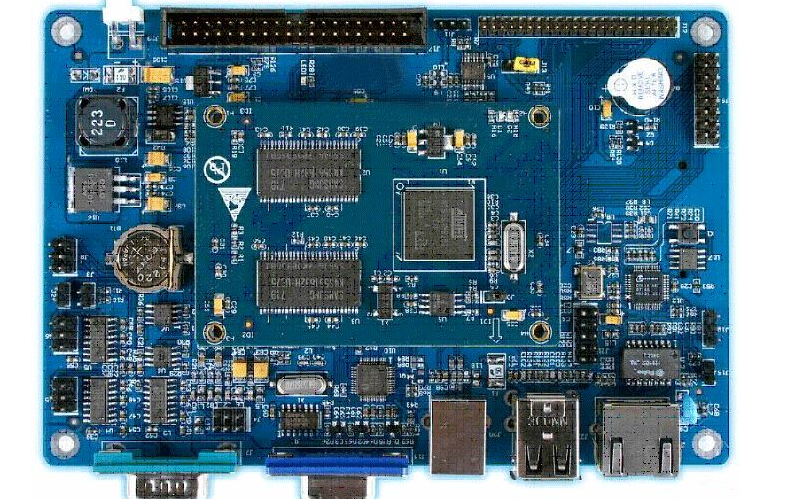

硬件層中包含嵌入式微處理器、存儲器(SDRAM、ROM、Flash等)、通用設備接口和I/O接口(A/D、D/A、I/O等)。硬件層通常是一個以嵌入式處理器為中心的,包含有電源電路、時鐘電路和存儲器電路的電路模塊,其中操作系統和應用程序都固化在模塊的ROM中。

1.1 嵌入式微處理器

嵌入式微處理器是嵌入式系統硬件層的核心,嵌入式微處理器將通用CPU中許多由板卡完成的任務集成到芯片內部,從而有利于系統設計趨于小型化、高效率和高可靠性。嵌入式微處理器大多工作在為特定用戶群所專門設計的系統中。n嵌入式微處理器的體系結構可以采用馮·諾依曼體系結構或哈佛體系結構,指令系統可以選用精簡指令系統(Reduced Instruction SetComputer,RISC)和復雜指令集系統CISC(Complex Instruction SetComputer, CISC)。

嵌入式微處理器有各種不同的體系,目前全世界嵌入式微處理器已經超過1000多種,體系結構有30多個系列,其中主流的體系有ARM、MIPS、PowerPC、X86等。即使在同一體系中,也可以具有不同的時鐘頻率、數據總線寬度、接口和外設。目前沒有一種嵌入式微處理器可以主導市場,嵌入式微處理器的選擇是根據具體的應用而決定的。

1.2 存儲器

嵌入式系統的存儲器包含Cache、主存儲器和輔助存儲器,用來存放和執(zhí)行代碼。

①Cache是一種位于主存儲器和嵌入式微處理器內核之間的快速存儲器陣列,存放的是最近一段時間微處理器使用最多的程序代碼和數據。

Cache一般集成在嵌入式微處理器內,可分為數據Cache、指令Cache或混合Cache,Cache的存儲容量大小依不同處理器而定。

②主存儲器用來存放系統和用戶的程序及數據,是嵌入式微處理器能直接訪問的存儲器。主存儲器包含有ROM和RAM,可以位于微處理器的內部或外部。常用的ROM類存儲器有NOR Flash、EPROM和PROM等,RAM類存儲器有SRAM、DRAM和SDRAM等,容量為256KB~1GB。

③輔助存儲器通常指硬盤、NAND Flash、CF卡、MMC和SD卡等,用來存放大數據量的程序代碼或信息,一般容量較大,但讀取速度與主存相比要慢一些。

1.3 通用設備接口和I/O接口

嵌入式系統通常具有與外界交互所需要的通用設備接口,如GPIO、A/D(模/數轉換接口)、D/A(數/模轉換接口)、RS-232接口(串行通信接口)、Ethernet(以太網接口)、USB(通用串行總線接口)、音頻接口、VGA視頻輸出接口、I2C(現場總線)、SPI(串行外圍設備接口)和IrDA(紅外線接口)等。

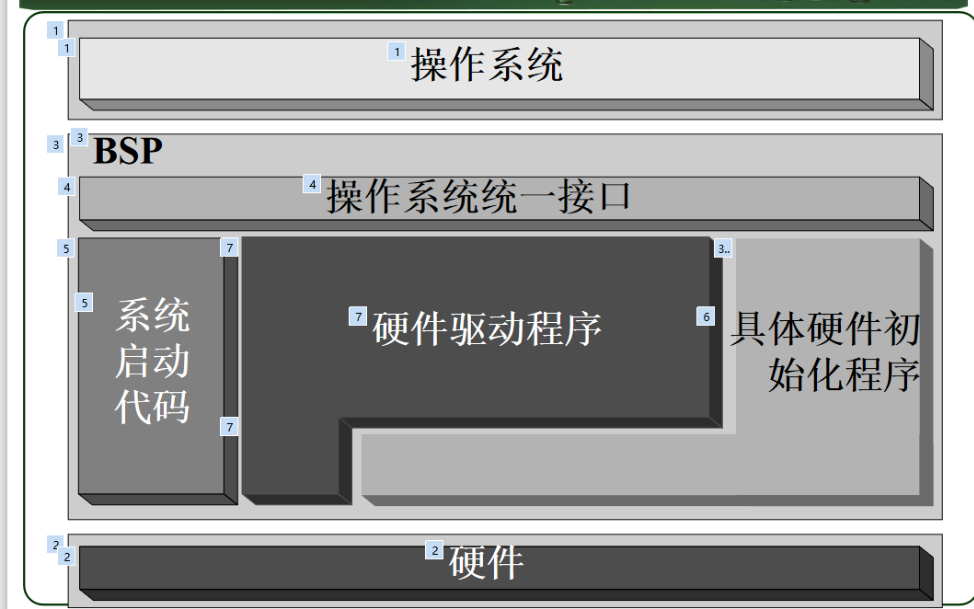

2.中間層

中間層也稱為硬件抽象層(Hardware Abstract Layer,HAL)或板級支持包(Board Support Package,BSP),位于硬件層和軟件層之間,將系統上層軟件與底層硬件分離開來。

BSP作為上層軟件與硬件平臺之間的接口,需要為操作系統提供操作和控制具體硬件的方法。不同的操作系統具有各自的軟件層次結構,BSP需要為不同的操作系統提供特定的硬件接口形式。BSP使上層軟件開發(fā)人員無需關心底層硬件的具體情況,根據BSP層提供的接口即可進行開發(fā)。

BSP是一個介于操作系統和底層硬件之間的軟件層次,包括了系統中大部分與硬件聯系緊密的軟件模塊。BSP一般包含相關底層硬件的初始化、數據的輸入/輸出操作和硬件設備的配置等功能。

2.1 嵌入式系統硬件初始化

系統初始化過程按照自底向上、從硬件到軟件的次序依次可以分為片級初始化、板級初始化和系統級初始化3個主要環(huán)節(jié)。

①片級初始化是一個純硬件的初始化過程,包括設置嵌入式微處理器的核心寄存器和控制寄存器、嵌入式微處理器核心工作模式和嵌入式微處理器的局部總線模式等。

②板級初始化是一個同時包含軟硬件兩部分在內的初始化過程,完成嵌入式微處理器以外的其他硬件設備的初始化,設置某些軟件的數據結構和參數,為隨后的系統級初始化和應用程序的運行建立硬件和軟件環(huán)境。

③系統級初始化主要進行操作系統的初始化。BSP將對嵌入式微處理器的控制權轉交給嵌入式操作系統,由操作系統完成余下的初始化操作。最后,操作系統創(chuàng)建應用程序環(huán)境,并將控制權交給應用程序的入口。

2.2 硬件相關的設備驅動程序

nnBSP中包含硬件相關的設備驅動程序,但是這些設備驅動程序通常不直接由BSP使用,而是在系統初始化過程中由BSP將他們與操作系統中通用的設備驅動程序關聯起來,并在隨后的應用中由通用的設備驅動程序調用,實現對硬件設備的操作。

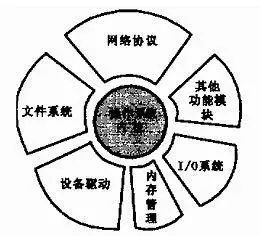

3.系統軟件層

系統軟件層通常包含有嵌入式操作系統(Embedded Operating System,EOS) 、文件系統、網絡系統及通用組件模塊組成。

3.1 嵌入式操作系統

EOS除具備了一般操作系統最基本的任務調度、同步機制、中斷處理、文件處理等功能外,還具有如下特點:

強實時性;

支持開放性和可伸縮性的體系結構,具有可裁減性;

提供統一的設備驅動接口;

支持TCP/IP協議及其他協議,提供TCP/UDP/IP/PPP協議支持及統一的MAC訪問層接口,提供強大的網絡功能;

嵌入式操作系統的用戶接口通過系統的調用命令向用戶程序提供服務;

嵌入式系統一旦開始運行就不需要用戶過多的干預;

嵌入式操作系統和應用軟件被固化在嵌入式系統計算機的ROM中;

具有良好的硬件適應性(可移植性)。

3.2 文件系統

嵌入式文件系統主要提供文件存儲、檢索和更新等功能。嵌入式文件系統通常支持FAT32、JFFS2、YAFFS等幾種標準的文件系統,一些嵌入式文件系統還支持自定義的實時文件系統。

嵌入式文件系統以系統調用和命令方式提供文件的各種操作,如設置、修改對文件和目錄的存取權限,提供建立、修改、改變和刪除目錄等服務,提供創(chuàng)建、打開、讀寫、關閉和撤銷文件等服務。

4.應用軟件層

應用軟件層用來實現對被控對象的控制功能,由所開發(fā)的應用程序組成,面向被控對象和用戶。

嵌入式實時操作系統

RTOS與通用計算機系統不同,要求系統中的任務不但執(zhí)行結果要正確,而且必須在一定的時間約束(Deadline)內完成。在RTOS中,一個邏輯上正確的計算結果,若其產生的時間晚于某個規(guī)定的時間,那么也認為系統的行為是不正確的。

1.實時系統RTOS的定義

RTOS是指能夠在指定或者確定的時間內完成系統功能和對外部或內部、同步或異步時間做出響應的系統,系統能夠處理和存儲控制系統所需要的大量數據。RTOS的正確性不僅依賴于系統計算的邏輯結果,還依賴于產生這個結果的時間。

2.RTOS的特點

2.1 約束性

RTOS任務的約束包括時間約束、資源約束、執(zhí)行順序約束和性能約束。

RTOS的任務具有時間約束性。時間約束性可分為“硬實時”和“軟實時”。

資源約束是指多個實時任務共享有限的資源時,必須按照一定的資源訪問控制協議進行同步,以避免死鎖和高優(yōu)先級任務被低優(yōu)先級任務堵塞的時間(即優(yōu)先級倒置時間)不可預測。

性能約束是指必須滿足如可靠性、可用性、可預測性、服務質量(Quality of Service,QoS)等性能指標。

2.2 可預測性

可預測性是指RTOS完成實時任務所需要的執(zhí)行時間應是可知的。

2.3 可靠性

大多數RTOS要求有較高的可靠性,要求系統在最壞情況下都能正常工作或避免損失。可靠性是RTOS的重要性能指標。

n(4)交互性n外部環(huán)境是RTOS不可缺少的一個組成部分,外部環(huán)境往往是被控子系統,兩者相互作用構成完整的實時系統。

3.RTOS調度

給定一組實時任務和系統資源,確定每個任務何時何地執(zhí)行的整個過程就是調度。而RTOS中調度的目的則是要盡可能地保證每個任務滿足它們的時間約束,及時對外部請求做出響應。

4.RTOS分類

RTOS主要分為強實時(Hard Real-Time)系統和弱實時(Soft Real-Time)系統兩類。強實時系統應用在航空航天、軍事、核工業(yè)等領域中,弱實時系統如視頻點播系統、信息采集與檢索系統等。

嵌入式微處理器體系結構

1.馮·諾依曼體系結構與哈佛結構

1.1 馮·諾依曼(Von Neumann)結構

馮·諾依曼結構的計算機由CPU和存儲器構成,其程序和數據共用一個存儲空間,程序指令存儲地址和數據存儲地址指向同一個存儲器的不同物理位置;采用單一的地址及數據總線,程序指令和數據的寬度相同。程序計數器(PC)是CPU內部指示指令和數據的存儲位置的寄存器。

CPU通過程序計數器提供的地址信息,對存儲器進行尋址,找到所需要的指令或數據,然后對指令進行譯碼,最后執(zhí)行指令規(guī)定的操作。處理器執(zhí)行指令時,先從儲存器中取出指令解碼,再取操作數執(zhí)行運算,即使單條指令也要耗費幾個甚至幾十個周期,在高速運算時,在傳輸通道上會出現瓶頸效應。

使用馮.諾依曼結構的CPU和微控制器有Intel公司的8086系列及其他CPU,ARM公司的ARM7、MIPS公司的MIPS處理器等。

1.2 哈佛(Harvard)結構

哈佛結構的主要特點是將程序和數據存儲在不同的存儲空間中,即程序存儲器和數據存儲器是兩個相互獨立的存儲器,每個存儲器獨立編址、獨立訪問。系統中具有程序的數據總線與地址總線,數據的數據總線與地址總線。

這種分離的程序總線和數據總線可允許在一個機器周期內同時獲取指令字(來自程序存儲器)和操作數(來自數據存儲器),從而提高執(zhí)行速度,提高數據的吞吐率。又由于程序和數據存儲器在兩個分開的物理空間中,因此取指和執(zhí)行能完全重疊,具有較高的執(zhí)行效率。

目前使用哈佛結構的CPU和微控制器品種有很多,有摩托羅拉公司的MC68系列、Zilog公司的Z8系列、ATMEL公司的AVR系列和ARM公司的ARM9、ARM10和ARM11等。

2 . 精簡指令集計算機

早期的計算機采用復雜指令集計算機(Complex Instruction Set Computer,CISC)體系。在CISC中,為了支持目標程序的優(yōu)化,支持高級語言和編譯程序,增加了許多復雜的指令,控制邏輯極不規(guī)整,給VLSI工藝造成很大困難。

精簡指令集計算機(Reduced Instruction Set Computer,RISC)體系結構是在CISC的基礎上產生并發(fā)展起來的,RISC的著眼點不是簡單地放在簡化指令系統上,而是通過簡化指令系統使計算機的結構更加簡單合理,從而提高運算效率。

采用Load/Store指令訪問存儲器,其余指令的操作都在寄存器之間進行;增加CPU中通用寄存器數量,算術邏輯運算指令的操作數都在通用寄存器中存取;大部分指令控制在一個或小于一個機器周期內完成;以硬布線控制邏輯為主,不用或少用微碼控制;采用高級語言編程,重視編譯優(yōu)化工作,以減少程序執(zhí)行時間。

3 . 流水線技術

流水線技術應用于計算機系統結構的各個方面, 是將一個重復的時序分解成若干個子過程,而每一個子過程都可有效地在其專用功能段上與其他子過程同時執(zhí)行。實現子過程的功能所需時間盡可能相等。形成流水處理,需要一段準備時間。指令流發(fā)生不能順序執(zhí)行時,會使流水線過程中斷,再形成流水線過程則需要時間。

4 . 信息存儲的字節(jié)順序

4.1 大端和小端存儲法

對于一個多字節(jié)類型的數據,在存儲器中有兩種存放方法。n低字節(jié)數據存放在內存低地址處,高字節(jié)數據存放在內存高地址處,稱為小端字節(jié)順序存儲法;

高字節(jié)數據存放在內存低地址處,低字節(jié)數據存放在內存高地址處,稱為大端字節(jié)順序存儲法。

4.2 可移植性問題

當在不同存儲順序的微處理器間進行程序移植時,要特別注意存儲模式的影響。把從軟件得到的二進制數據寫成一般的數據格式往往會涉及到存儲順序的問題。

4.3 通信中的存儲順序問題

在網絡通信中,Internet協議(即IP協議)定義了標準的網絡字節(jié)順序。該字節(jié)順序被用于所有設計使用在IP協議上的數據包、高級協議和文件格式上。n很多網絡設備也存在存儲順序問題:即字節(jié)中的位采用大端法(最重要的位優(yōu)先)或小端法(最不重要的位優(yōu)先)發(fā)送。這取決于OSI模型最底層的數據鏈路層。

4.4 數據格式的存儲順序

嵌入式處理器的類型

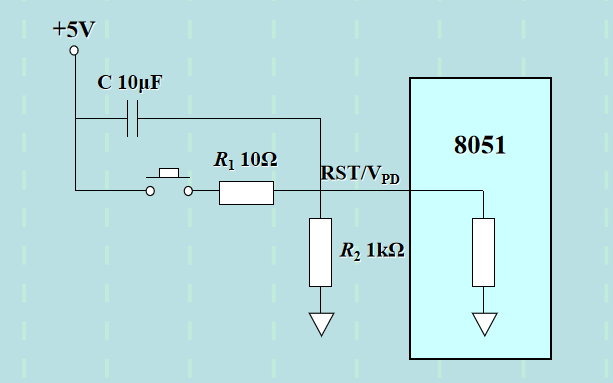

又稱為單片機,芯片內部集成ROM、EPROM、RAM、總線、總線邏輯、定時/計數器、看門狗、I/O、串行口、脈寬調制輸出(PWM)、A/D、D/A、Flash、EEPROM等各種必要功能和外設。

嵌入式微控制器具有單片化、體積小、功耗和成本低,可靠性高等特點,約占嵌入式系統市場份額的70%。

2 . 嵌入式微處理器(MPU)

由通用計算機中的CPU發(fā)展而來,嵌入式微處理器只保留和嵌入式應用緊密相關的功能硬件,去除其他的冗余功能部分,以最低的功耗和資源實現嵌入式應用的特殊要求。

3 . 嵌入式DSP

嵌入式DSP是專門用于信號處理方面的處理器,其在系統結構和指令算法方面進行了特殊設計,具有很高的編譯效率和指令執(zhí)行速度。

4 . 嵌入式片上系統SoC

SoC,System onchip,或者 System on a chip。基本定義是:以知識產權核為設計基礎,在單個芯片上集成處理器、存儲器、各種接口等部件,組成一個部分完整的計算機系統,可以完成特定的應用功能。

目前,大多數32位的嵌入式處理器芯片都是SoC。嵌入式SoC是追求產品系統最大包容的集成器件。絕大多數系統構件都在一個系統芯片內部。

5 . 多核處理器

將兩個或多個CPU核封裝在一個芯片內部,可節(jié)省大量的晶體管和封裝成本,同時還能顯著提高處理器的性能。實現兩個或多個內核協調工作.

嵌入式系統的發(fā)展史

1 . 以單芯片為核心的可編程控制器形式的系統。一般沒有操作系統的支持,通過匯編語言直接控制。

二十世紀七十年代1971年11月,世界上第一片微處理器Intel4004,嵌入式應用發(fā)展最重要的里程碑。

2 . 以嵌入式CPU為基礎,以簡單操作系統為核心的嵌入式系統。

有簡單操作系統的支持,但通用性較弱。

二十世紀八十年代,出現了單片機–Intel進一步完善了8048,在它的基礎上研制成功了8051單片機–其后發(fā)展的DSP 產品更快地提升了嵌入式系統的技術水平。

1981年,第1個商業(yè)嵌入式實時內核(VTRX32),隨后,出現了一些嵌入式操作系統。

3 . 以嵌入式操作系統為標志的嵌入式系統。

兼容性佳。

二十世紀九十年代至今。硬件方面,尤其是芯片方面的發(fā)展表現出三個特點:

軟件方面, 嵌入式操作系統出現了進一步的分化,誕生了一些嵌入式操作系統家族。

跨平臺的軟件開發(fā)技術從通用計算機上延展到嵌入式設備上

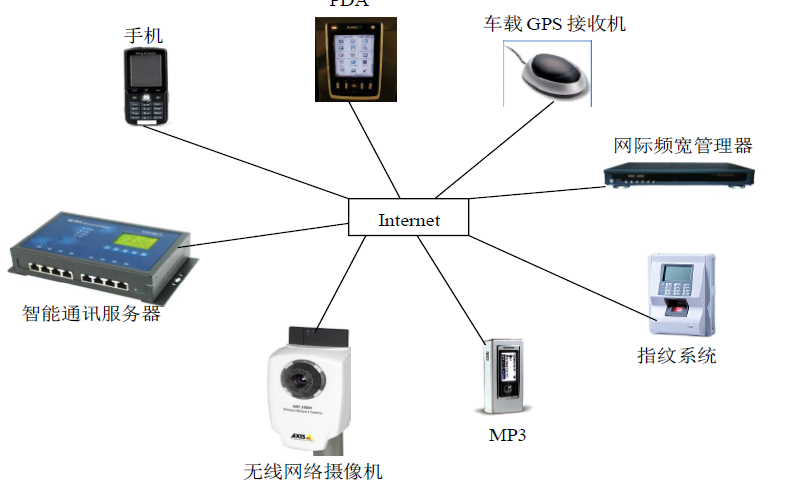

4 . 以Internet為標志的嵌入式系統。

與Internet相結合。

嵌入式控制器的應用幾乎無處不在:移動電話、家用電器、汽車……無不有它的蹤影。嵌入控制器因其體積小、可靠性高、功能強、靈活方便等許多優(yōu)點,其應用已深入到工業(yè)、農業(yè)、教育、國防、科研以及日常生活等各個領域,對各行各業(yè)的技術改造、產品更新換代、加速自動化化進程、提高生產率等方面起到了極其重要的推動作用。從上世紀90年代開始,嵌入式技術已全面展開,成為通信產品和消費類產品的共同發(fā)展方向,在通信領域、廣播電視領等得到廣泛應用。個人領域嵌入式產品主要是個人商用,作為個人移動的數據處理和通訊軟件得到普及。嵌入式系統技術發(fā)展的空間是無比廣。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19801瀏覽量

233519 -

嵌入式

+關注

關注

5141文章

19526瀏覽量

314861 -

存儲器

+關注

關注

38文章

7633瀏覽量

166391 -

嵌入式系統

+關注

關注

41文章

3665瀏覽量

130892 -

計算機

+關注

關注

19文章

7626瀏覽量

90160

原文標題:電子工程之嵌入式系統

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

嵌入式開發(fā)教程之程序設計與開發(fā)維護

嵌入式視頻教程之嵌入式系統開發(fā)對人才的技能要求

嵌入式視頻教程之嵌入式系統開發(fā)對人才的技能要求

WinCE實驗教程之--嵌入式系統

嵌入式系統教程之嵌入式系統設計與實例開發(fā)電子教材免費下載

嵌入式Linux開發(fā)教程之嵌入式系統介紹資料免費下載

嵌入式系統教程之嵌入式系統的IO模塊詳細資料說明

嵌入式系統教程之嵌入式處理器的詳細資料說明

嵌入式硬件系統教程之嵌入式存儲技術的詳細資料說明

嵌入式系統教程之嵌入式系統工程設計的詳細資料說明

ARM開發(fā)教程之ARM體系的嵌入式系統BSP的程序的設計說明

電子工程之嵌入式系統

電子工程之嵌入式系統

評論