新的工具和技術(shù)。

正在開發(fā)新的凸點(diǎn)結(jié)構(gòu)以在倒裝芯片封裝中實(shí)現(xiàn)更高的互連密度,但它們復(fù)雜、昂貴且越來越難以制造。

對(duì)于具有高引腳數(shù)的產(chǎn)品,倒裝芯片封裝長(zhǎng)期以來一直是一種流行的選擇,因?yàn)樗鼈兝谜麄€(gè)芯片區(qū)域進(jìn)行互連。該技術(shù)自 1970 年代以來一直在使用,從 IBM 的 C4開始,但真正廣泛使用是在 1990 年代。

從那時(shí)起,凸塊技術(shù)不斷發(fā)展,以處理內(nèi)存、高性能計(jì)算和移動(dòng)計(jì)算設(shè)備所需的不斷增加的功率和信號(hào)連接密度。滿足這一需求需要新的互連技術(shù),以實(shí)現(xiàn)更小的凸點(diǎn)間距,目前正在生產(chǎn)中。

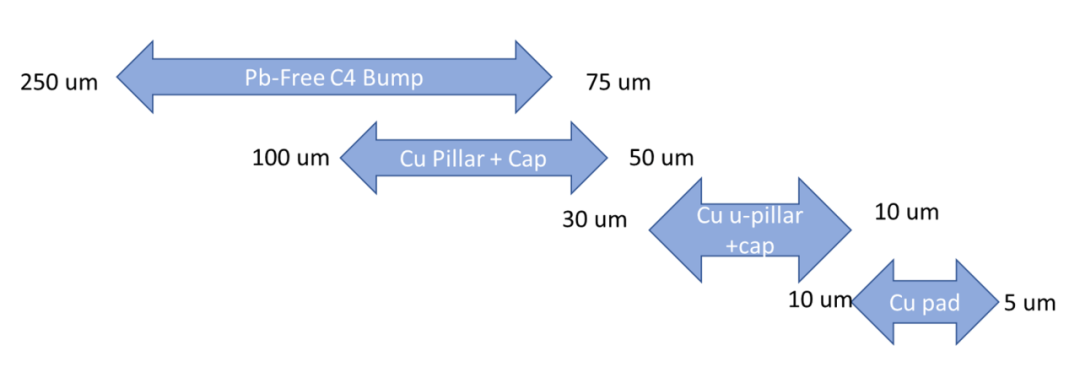

隨著時(shí)間的推移,倒裝芯片互連的路線圖從無鉛凸塊發(fā)展到銅柱,再到銅微凸塊。間距尺寸繼續(xù)縮小,這反過來又給凸塊和鍵合帶來了制造挑戰(zhàn)。

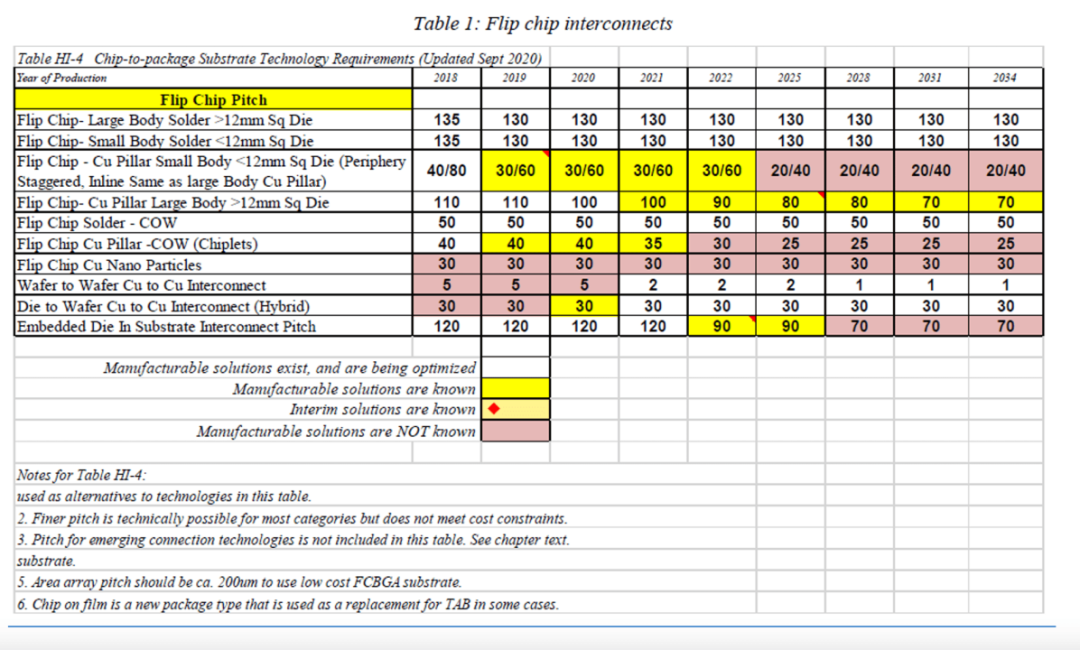

圖 1:倒裝芯片技術(shù)間距范圍。來源:A. Meixner/半導(dǎo)體工程

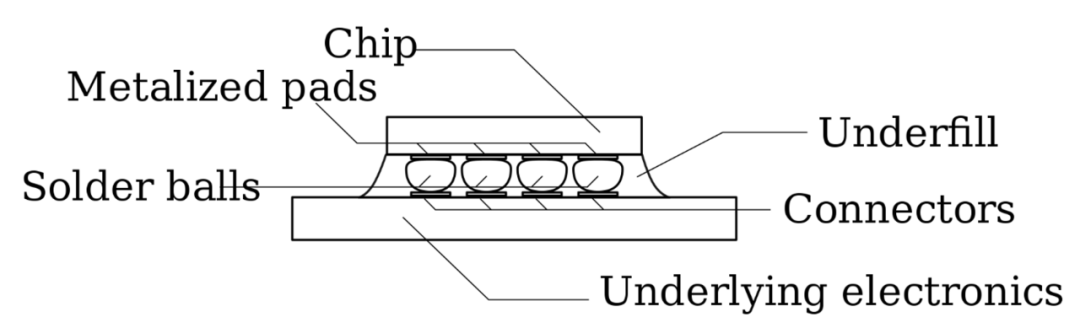

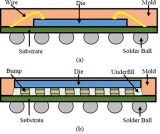

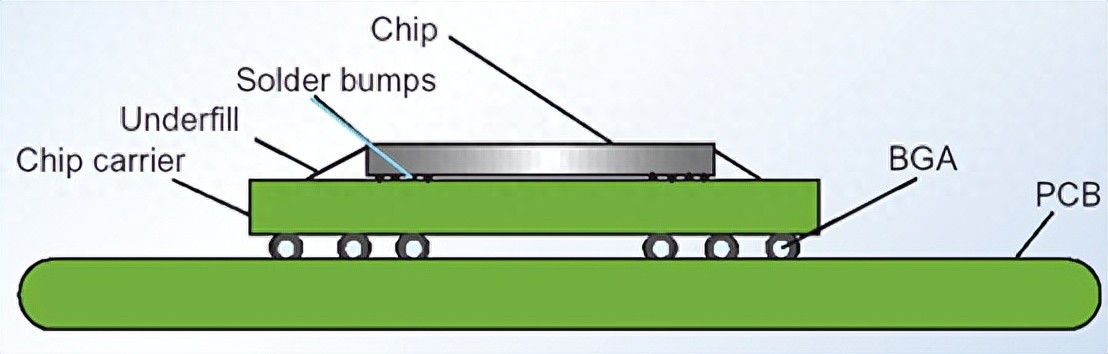

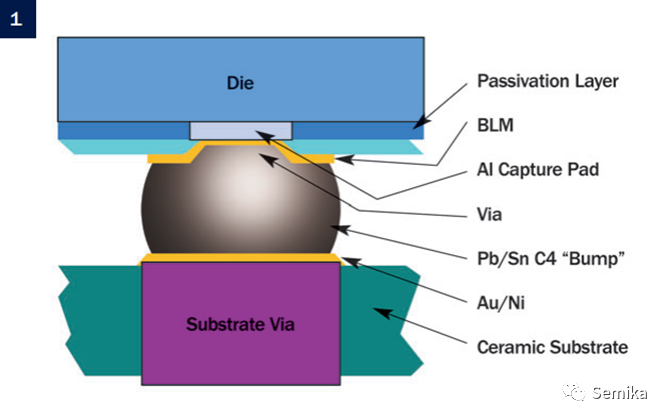

?圖 2:倒裝芯片組件。來源:維基百科

?圖 2:倒裝芯片組件。來源:維基百科

“在250微米及以下的倒裝芯片領(lǐng)域,最初是錫鉛凸塊其中一項(xiàng)重大舉措是無鉛化。但是,當(dāng)你開始達(dá)到 100 微米或以下時(shí),你會(huì)開始看到更多的銅柱,盡管當(dāng)我們看到高達(dá) 250 微米的銅柱時(shí)存在重疊,”Promex Industries 高級(jí)工藝工程師 Jeff Schaefer說。“對(duì)于 250 微米的間距,我們看到 130 微米的凸點(diǎn)尺寸或銅柱直徑。一旦我們達(dá)到 100 微米的間距,它就是 80 微米的直徑。我見過的最小間距是 62.5 微米間距和 40 微米柱。我預(yù)計(jì)很快就會(huì)看到 50 微米間距。”

基本的倒裝芯片工藝在電路制造之后開始,此時(shí)在芯片表面創(chuàng)建金屬焊盤以連接到 I/O。接下來是晶圓凸塊,將焊球沉積在每個(gè)焊盤上。然后晶圓被切割,這些芯片被翻轉(zhuǎn)和定位,使焊球與基板焊盤對(duì)齊。然后通常使用熱空氣使焊球熔化/回流,并且通常使用毛細(xì)管作用用電絕緣粘合劑在安裝的管芯底部填充。

圖 3:倒裝芯片制造工藝。來源:維基百科

轉(zhuǎn)向銅柱或微凸塊需要光刻來創(chuàng)建這些結(jié)構(gòu)。

Amkor Technology晶圓級(jí)封裝高級(jí)副總裁 Doug Scott 表示:“銅柱通常用于 130μm 間距以下,因?yàn)殂~柱不是圓形焊料凸點(diǎn),而是主要是頂部有焊料的銅柱。”“這允許將銅柱凸點(diǎn)放置得更近,而不會(huì)在組裝回流期間焊料連接在一起的風(fēng)險(xiǎn)——通常,~40 μm Cu + ~25 μm。”

主題也有變化。“微凸塊是硅與硅之間互連的常用術(shù)語,它略有不同,因?yàn)?CTE(熱膨脹系數(shù))通常相同,” 日月光集團(tuán)工程/技術(shù)營(yíng)銷高級(jí)總監(jiān) Mark Gerber 說。“用于銅柱的一些一般設(shè)計(jì)規(guī)則是相同的,但平坦的表面形貌和低應(yīng)力接頭允許使用的底部填充物具有靈活性。這也可以驅(qū)動(dòng)單個(gè)凸點(diǎn)間距。今天,由于前面提到的路由考慮,對(duì)于所使用的晶圓級(jí)或晶圓廠級(jí)路由,35μm 的凸點(diǎn)全陣列間距是可能的。”

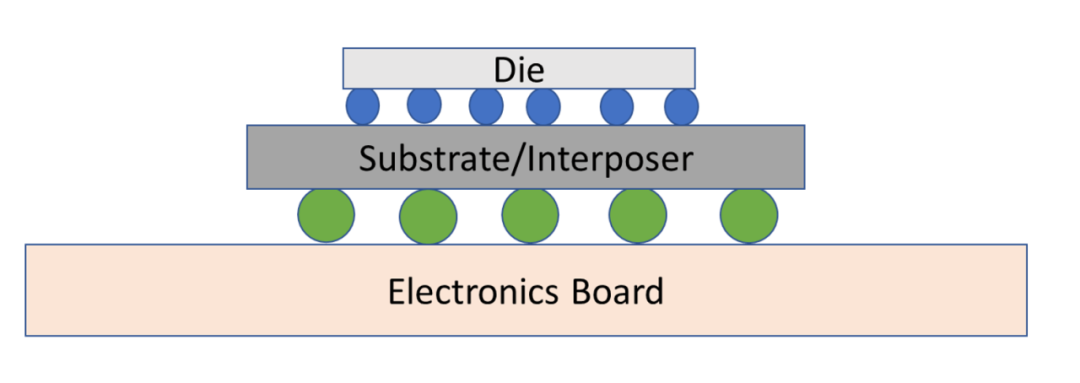

異構(gòu)集成路線圖描述了封裝的所有方面,包括從焊線到硅通孔的裸片到基板互連。對(duì)于倒裝芯片封裝,芯片到基板互連、基板重新分布區(qū)域和基板到板互連都在制造限制中發(fā)揮作用。

圖 4:倒裝芯片封裝的概念圖。來源:A. Meixner/半導(dǎo)體工程

表 1 中列出了每種倒裝芯片互連技術(shù)的最小間距。

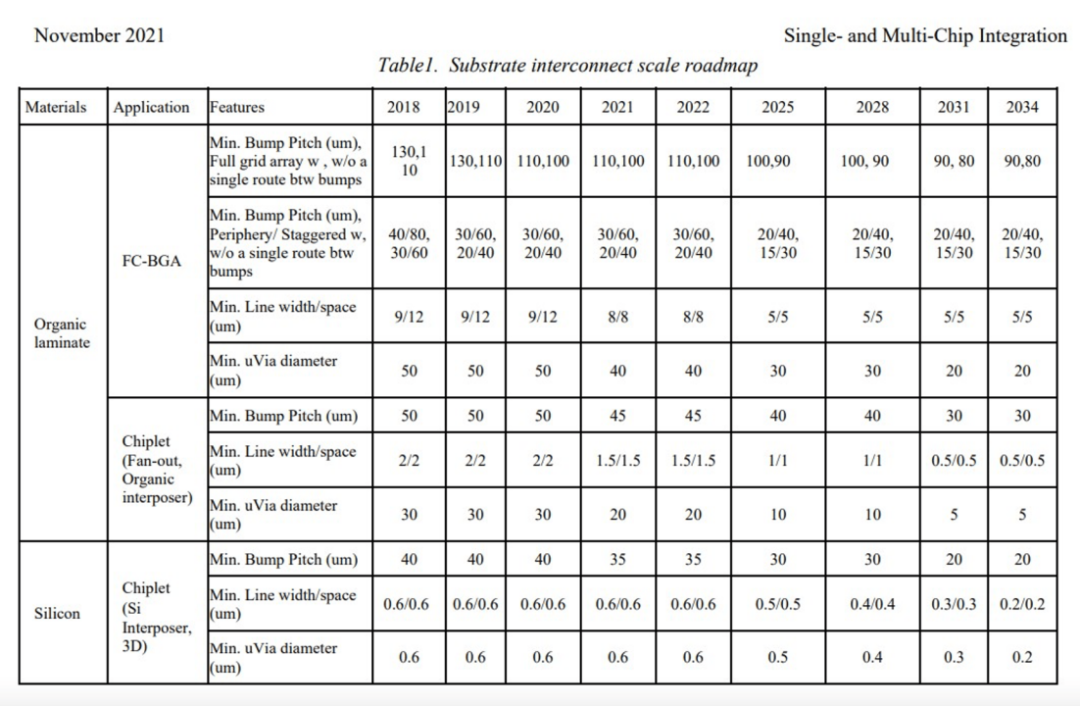

基板互連(將封裝連接到電路板的部分)的相應(yīng)表格。

互連技術(shù)的每一次變革都會(huì)帶來新的工藝及其局限性,從而推動(dòng)創(chuàng)新、良率管理和缺陷檢測(cè)。

凸塊技術(shù)限制

凸塊技術(shù)是通過間距、尺寸、高度以及電氣和機(jī)械特性來衡量的。熱注意事項(xiàng)因材料的 CTE 不匹配而異。翹曲是較大管芯和晶圓的一個(gè)問題,在管芯貼裝之前對(duì)晶圓進(jìn)行背面研磨會(huì)加劇翹曲。

“對(duì)于每種類型的互連,間距限制有許多驅(qū)動(dòng)因素,”ASE 的 Gerber 說。“從傳統(tǒng)的焊料凸點(diǎn)倒裝芯片互連開始,間距能力取決于底部填充的坍塌高度、走線布線的捕獲焊盤間距、焊球到焊球短路風(fēng)險(xiǎn)的捕獲焊盤間距以及其他幾個(gè)與間距相關(guān)的敏感性。預(yù)裝凸塊高度有一個(gè)定義的高度,但正如 IBM 定義的 C4 術(shù)語——受控塌陷芯片連接——焊料凸塊的直徑和捕獲焊盤尺寸將決定互連的“塌陷或最終高度”。這是使用與間距相關(guān)的焊料凸點(diǎn)的主要間距限制因素。”

凸點(diǎn)高度由設(shè)計(jì)決定,也有加工選擇。

“對(duì)于標(biāo)準(zhǔn)的電鍍焊料凸點(diǎn)和銅柱凸點(diǎn),預(yù)組裝凸點(diǎn)高度通常在 70μm 到 75μm 左右,組裝后塌陷的凸點(diǎn)高度約為 50μm,以便為凸點(diǎn)之間的底部填充流動(dòng)留出 x、y、z 空間。微凸塊的凸塊高度要低得多,并且涉及的焊料電鍍要少得多。具體來說,根據(jù)間距和末端需求,微凸塊的高度可以小于 10μm,同時(shí)減少銅和焊料的高度,”Amkor 的 Scott 說。“標(biāo)準(zhǔn)電鍍焊料凸點(diǎn)通常用于 130μm 至 250μm 的間距。在 130μm 以下,當(dāng)以 70μm 預(yù)組裝凸點(diǎn)高度開始時(shí),凸點(diǎn)之間沒有足夠的 xy 空間。”

創(chuàng)建銅柱需要比焊料凸點(diǎn)更多的處理步驟。

“當(dāng)我們過渡到 die-to-die 世界時(shí),技術(shù)是不同的,因?yàn)楝F(xiàn)在你正在處理晶圓,而與 die-to-substrate 相比,planerites 非常好。首先創(chuàng)建銅柱,在要獲得焊料或銅柱的初始晶圓上,先是凸點(diǎn)下金屬 (UBM)。它是向下進(jìn)入硅的開口上方的一個(gè)小蓋子。然后我們用它做一個(gè)銅芯,然后在上面放一個(gè)錫帽。然后是接收晶圓,它們看起來像是有一個(gè) UBM 焊盤,上面通常有一些鎳金類型的鍍層,因此它既漂亮又原始,”Promex Industries 的 Schaefer 解釋道。因此,您沒有像層壓基材那樣有輕微的壓痕,而是有輕微的擠壓。我們發(fā)現(xiàn)我們實(shí)際上能夠在沒有“焊盤上焊料”的情況下將它們濕焊。' 這就是它們的設(shè)計(jì)和建造方式。它幾乎就像焊料和焊盤一樣,因?yàn)樗且粋€(gè)小圓頂,而不是試圖進(jìn)入孔內(nèi)。”

銅柱形成所需的光刻步驟具有限制以及基板設(shè)計(jì)規(guī)則。

“對(duì)于由銅柱和尖端焊帽組成的銅柱,銅柱高度可以定義為一個(gè)或多個(gè)光致抗蝕劑層厚度的限制,并且當(dāng)您減小間距時(shí),銅柱的縱橫比銅柱高度與光刻膠材料和成像工具功能一起成為限制,”Gerber 說。“銅柱互連的第二個(gè)限制是使用的基板設(shè)計(jì)規(guī)則。對(duì)于 >110um 的精細(xì)間距,使用了 2 種主要方法 - BOT(跡線上鍵合)或 ET 嵌入式跡線,其中銅柱的焊帽放置在跡線頂部,而不是傳統(tǒng)的捕獲焊盤。銅柱尺寸和形狀,包括上述限制,可以限制繼續(xù)縮小間距的能力和路線圖。許多這些限制是由于能夠在基板側(cè)的柱子之間布線。隨著晶圓級(jí) RDL 等新技術(shù)的出現(xiàn),互連路線圖將得到進(jìn)一步推進(jìn),但在底部填充等制造工藝的高度/縱橫比方面仍然存在限制。”

其他人同意底部填充工藝會(huì)帶來挑戰(zhàn)。“當(dāng)你獲得更精細(xì)的間距和更小的凸起時(shí),它們會(huì)變得更短。現(xiàn)在越來越難找到底層填充材料。過去,底部填充膠被設(shè)計(jì)為小于 5 密耳的間隙,現(xiàn)在它們降至 3 密耳,即 75 微米,”Schaefer 說。“現(xiàn)在我們開始看到 60 和 25 微米的間隙。我敢肯定人們正在研究新的底部填充膠。但是還有很多事情要做。一方面,當(dāng)你得到更細(xì)的顆粒時(shí),它變得更像淤泥,這使得它更難流動(dòng)。這是一個(gè)需要移除的障礙。”

管理良率

隨著凸塊技術(shù)變得越來越小,額外的處理步驟——例如,用于創(chuàng)建銅柱的光刻——為良率檢測(cè)器開辟了新的機(jī)會(huì)。對(duì)于成功的鍵合工藝,微粒、表面污染物和焊料凸點(diǎn)空洞都會(huì)影響良率。這些需要過程控制、計(jì)量和檢查。

需要自然控制污染。“一級(jí) OSAT 投資于降低工廠污染源的水平,從而降低缺陷率,”Amkor 的 Scott 說。

底部填充工藝的準(zhǔn)備工作也不應(yīng)被低估。

“一般來說,對(duì)于層壓板,你需要在倒裝芯片之后進(jìn)行底部填充,”Promex 的 Schaefer 說。“我們決定將其放置在何處以及如何對(duì)其進(jìn)行回流。我們清潔它以清除芯片和基板之間間隙下的任何助焊劑材料。然后我們將用流動(dòng)的環(huán)氧樹脂進(jìn)行底部填充。它旨在浸濕而不留下空隙和那種性質(zhì)的東西。但是,隨著我們進(jìn)入更精細(xì)的球場(chǎng),我們面臨著挑戰(zhàn)。凸點(diǎn)變得更短,隨著它們變得更短,芯片和基板之間的間隙變得更小,因此更難清潔。想象一下,將兩個(gè)載玻片粘在一起,試圖清除它們之間的污垢。”

計(jì)量和檢測(cè)需求

對(duì)于管理過程控制和產(chǎn)量,計(jì)量和檢測(cè)工具發(fā)揮著重要作用。ASE 的 Gerber 說:“除了在設(shè)置和定義的生產(chǎn)間隔時(shí)使用的過程中橫截面分析之外,市場(chǎng)上還有一些工具可以幫助提供有關(guān)互連完整性的指導(dǎo)。”

凸塊工藝和鍵合工藝各自具有需要監(jiān)控的特定特性。對(duì)于凸塊,計(jì)量學(xué)側(cè)重于直徑、高度和共面性。更小的間距需要更嚴(yán)格的凸點(diǎn)直徑和高度控制。類似地,隨著凸塊高度的縮小,共面性窗口變得更小。通常,允許有 10% 的變化。例如,30μm 的凸點(diǎn)高度會(huì)導(dǎo)致 ±3μm 的允許偏差。超過此值會(huì)導(dǎo)致粘合不成功或粘合不良。

“鍵合通常使用大回流焊爐完成,”Amkor 高級(jí)封裝和技術(shù)集成副總裁 Mike Kelly 說。“回流工藝的初始特征是使用陰影波紋來量化回流期間的翹曲,并使用烘箱的溫度映射來確保倒裝芯片部件本身的溫度控制一致。在設(shè)置過程中,進(jìn)行機(jī)械芯片提升和檢查以確保良好的焊料潤(rùn)濕。此外,助焊劑通常通過“浸入式助焊劑”施加,其中芯片凸點(diǎn)“浸入”薄的、嚴(yán)格控制的助焊劑儲(chǔ)層中。這些物品的目視檢查是在抽樣的基礎(chǔ)上進(jìn)行的。”

目視檢查自動(dòng)化程度的提高減少了對(duì)操作員查看圖像和做出決定的依賴。凸塊連接的指數(shù)增長(zhǎng)是一個(gè)驅(qū)動(dòng)因素。鍵合工藝的改變提供了另一個(gè)。自對(duì)準(zhǔn)回流焊工藝是一項(xiàng)成熟的技術(shù)。與先進(jìn)封裝中常用的熱壓鍵合,有通過電氣測(cè)試的可靠性機(jī)制。這反過來又促使使用 X 射線檢測(cè)和計(jì)量工具來查看鍵合后的凸點(diǎn)。

“對(duì)于低復(fù)雜性包裝,設(shè)施可以擺脫操作員和手動(dòng)檢查。對(duì)于具有 100 個(gè)凸點(diǎn)的零件,此方法是可行的。在 1,000 次顛簸時(shí),這絕對(duì)是一種壓力。一旦零件有 10,000 個(gè)凸點(diǎn),就沒有機(jī)會(huì)了。我們超越了這一點(diǎn),我們需要轉(zhuǎn)向下一個(gè)方法,”Bruker 應(yīng)用和產(chǎn)品管理總監(jiān) Frank Chen指出“質(zhì)量和復(fù)雜性是相輔相成的,因?yàn)楫?dāng)你試圖制造更復(fù)雜的東西時(shí),你的產(chǎn)量會(huì)受到影響,并且需要一些新的工具。而工裝既是制程工具,又是計(jì)量工具,兩者需要并行推進(jìn)。從我們自己的研究中,我們看到,一旦你進(jìn)行了 1,000 次顛簸,你就需要開始思考‘我的手動(dòng)技術(shù)不夠用,我需要一些新的東西。”

各種檢測(cè)和計(jì)量工具可用于支持封裝制造。

“有幾種方法可以或應(yīng)該用于實(shí)現(xiàn)過程控制。首先,傳統(tǒng)二維檢測(cè) (AOI) 用于每個(gè)工藝流程(即 IQC、OQA、照片、清潔、電鍍等)的 100% 表面缺陷檢測(cè)。接下來,二維計(jì)量 (AOI) 可用于控制凸點(diǎn)尺寸和直徑尺寸控制。此外,3D 計(jì)量 (AOI) 可用于采樣凸塊高度/共面度計(jì)量信息采集(這通常使用基于激光三角測(cè)量的技術(shù)完成),”O(jiān)nto Innovation 產(chǎn)品營(yíng)銷經(jīng)理 Nathan Peng說“此外,3D 計(jì)量可以針對(duì)單個(gè)凸點(diǎn)高度特征,通常使用白光干涉儀技術(shù)收集。此外,還有一些方法可以檢測(cè)凸點(diǎn)頂部的有機(jī)殘留物,這些有機(jī)殘留物可能導(dǎo)致凸點(diǎn)與焊盤連接失敗。”

結(jié)論

需要更高互連數(shù)量的產(chǎn)品繼續(xù)推動(dòng)互連路線圖。每種倒裝芯片技術(shù)都有制造限制,包括材料特性、挑戰(zhàn)底部填充技術(shù)的縮小尺寸,以及增加使用光刻技術(shù)來創(chuàng)建互連結(jié)構(gòu)。鍵合工藝的任何變化都會(huì)導(dǎo)致計(jì)量和檢測(cè)步驟的增加,以滿足良率和質(zhì)量目標(biāo)。

審核編輯:劉清

-

倒裝芯片

+關(guān)注

關(guān)注

1文章

102瀏覽量

16516 -

UBM

+關(guān)注

關(guān)注

0文章

10瀏覽量

7778 -

CTE

+關(guān)注

關(guān)注

0文章

10瀏覽量

7925

原文標(biāo)題:倒裝芯片封裝的挑戰(zhàn)

文章出處:【微信號(hào):ICViews,微信公眾號(hào):半導(dǎo)體產(chǎn)業(yè)縱橫】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

全面剖析倒裝芯片封裝技術(shù)的內(nèi)在機(jī)制、特性優(yōu)勢(shì)、面臨的挑戰(zhàn)及未來走向

倒裝芯片封裝:半導(dǎo)體行業(yè)邁向智能化的關(guān)鍵一步!

倒裝封裝(Flip Chip)工藝:半導(dǎo)體封裝的璀璨明星!

倒裝芯片的優(yōu)勢(shì)_倒裝芯片的封裝形式

LED芯片封裝大揭秘:正裝、垂直、倒裝,哪種更強(qiáng)?

倒裝芯片(flip chip)算先進(jìn)封裝嗎?未來發(fā)展怎么樣?

芯片倒裝與線鍵合相比有哪些優(yōu)勢(shì)

探索倒裝芯片互連:從原理到未來的全面剖析

引腳封裝HotRod和FC-SOT上倒裝芯片的降額和壽命計(jì)算

芯片熱管理,倒裝芯片封裝“難”在哪?

底部填充工藝在倒裝芯片上的應(yīng)用

倒裝芯片封裝的挑戰(zhàn)

倒裝芯片封裝的挑戰(zhàn)

評(píng)論