為處理器驗證創建一個“瑞士奶酪模型”,以保證高效的驗證品質!

所有的處理器都有著很高的品質要求,其可靠性是處理器驗證團隊的主要關切。提供一流質量的產品需要一個戰略性的、勤勉的和徹底的方法去實現。因此,處理器驗證發揮著重要作用,它需要結合所有行業標準技術--而這就有點像心理學上的的瑞士奶酪模型(又稱Reason模型)原則。

我們強烈需要一個強大的、分層的處理器驗證策略!

我在之前曾經說過:處理器驗證是一門微妙的藝術。我們需要考慮到所有的不確定性,這意味著在優化資源的同時開放驗證范圍。一方面,我們要在最終交付前找到所有的關鍵漏洞。另一方面,我們必須有一個高效的驗證策略來滿足上市時間的硬性要求。交付智能處理器驗證意味著在產品開發過程中盡可能有效地、盡早地找到有意義的bug。實現這一目標的方法之一是結合所有行業標準的驗證技術。而正是通過創建冗余,最終找到并擊敗所有關鍵bug。

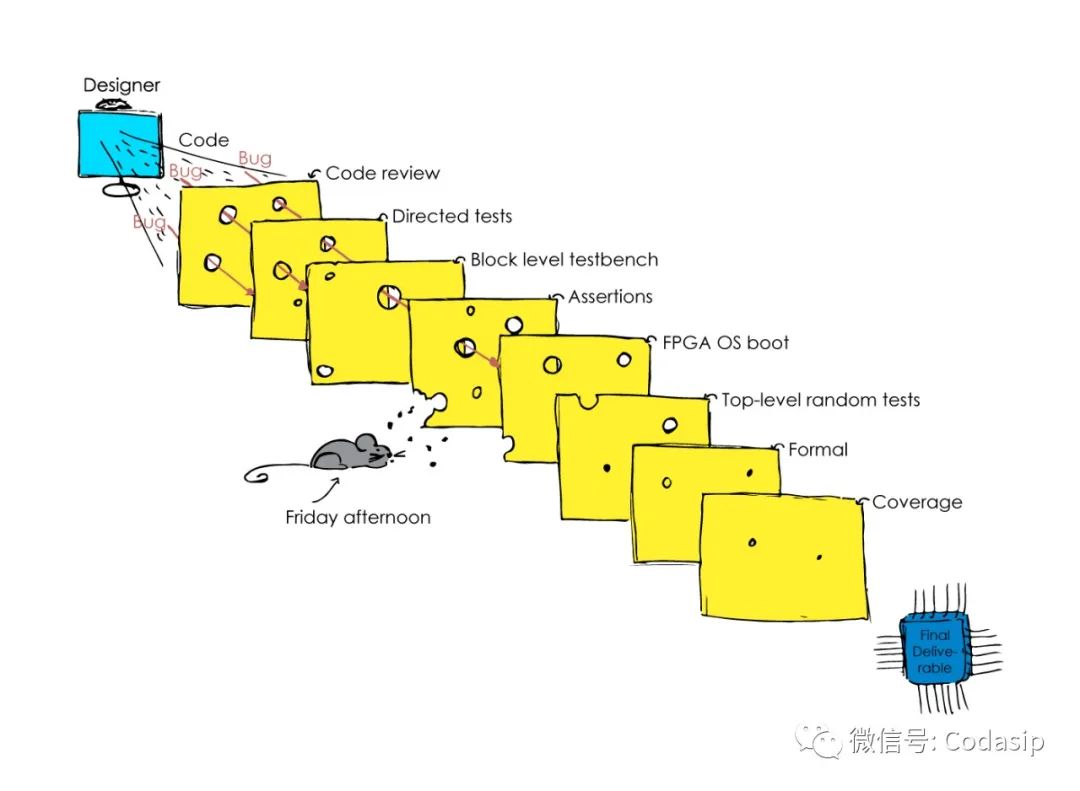

不同類型的bug都有一個復雜性--或bug評分--這取決于觸發bug所需的事件數量和類型。有些可能是用覆蓋率發現的,而有些是用形式證明發現的。想象一下,如果將”瑞士奶酪模型”應用于處理器驗證。每一片奶酪都象征著一種驗證技術,它有一些特定的優勢來捕捉特定類型的bug。漏洞逃脫并進入最終交付物的風險通過不同層次和類型的驗證來減輕,而這些驗證是相互分層的。

在應用于處理器驗證的瑞士奶酪模型中,其原理類似于航空業:如果有一條直接穿過所有切片的路徑,那么飛機就有墜毀的風險。這就是為什么航空業對程序、飛行檢查單和冗余系統要求嚴格?我們的目標是增加更多的切片,減少每一個切片上的孔的大小,直至最后沒有任何縫隙可以穿過,此時一個高質量的處理器正式完成。

應用于處理器驗證的瑞士奶酪模型原則

通過驗證方法(以瑞士奶酪模型為例):

首先需要創建冗余,以確保在其中一個layer上失敗時的連續性。

當在開發過程中發現bug時,表明漏洞出現在了其中的幾片奶酪上。因此,我們可以改進幾種驗證方法,以減少每片奶酪上的漏洞大小。利用這種方法,無論是簡易簡單的漏洞還是復雜的終極漏洞,都可以增加擊中bug的幾率。

最大限度地發揮每種驗證技術的潛力。

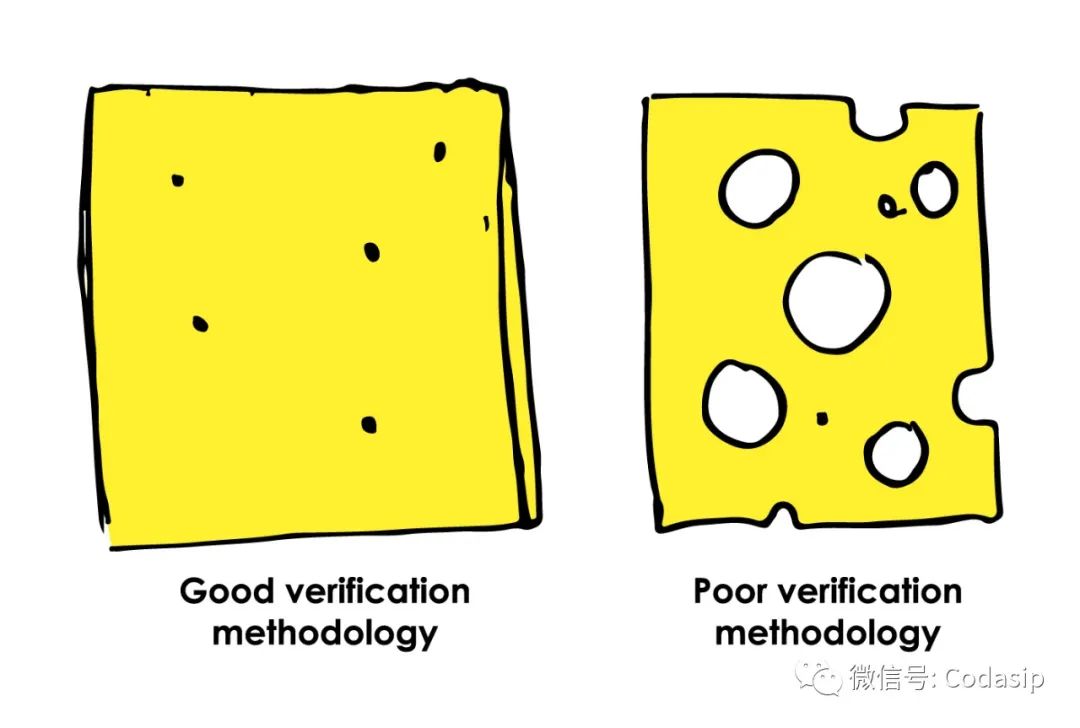

每個分片上的孔就是驗證方法中的一個洞。孔越多越大,意味著越多的bug可以逃脫。如果設計的同一區域(奶酪片之間的重疊孔)中沒有被任何一種驗證技術所覆蓋和測試,那么這個漏洞就會通過驗證,并最終出現在交付產品中。

一種好的驗證方法必須在每個切片上呈現盡可能少和小的孔。而這就要求驗證團隊有著扎實的策略、經驗和高效的溝通,這些品質也是交付高質量產品的重要因素。

在驗證過程中,當我們發現一個bug,或者一個切片上的孔時,及時修復并檢查其他切片是否有類似的漏洞。每一個切片都應該找到前一個切片中的漏洞,并在繼續運行之前解決掉它們。而實現這一目標的有效方式是全面健全性檢查!

在應用于處理器驗證的瑞士奶酪模型原則中,如果一種技術有改進的測試平臺、新的斷言等功能加持,那么在產品交付之前,該漏洞就會被及時發現和修復。所有的處理器驗證技術都很重要,正是所有技術的結合才能使每種技術更有效率。

同時我們需要意識到一個單一的驗證技術不可能完成所有的事情,是所有技術的綜合提高了驗證和處理器設計的整體質量。在產品的開發過程中,可能會有意想不到的變化或因素,這些外部行為會影響某種技術的效率。例如,設計中的變化沒有很好的傳達給驗證團隊,或者出小差的周五下午的工作效率導致了人為錯誤。這些因素都會增加切片上孔的大小,因此保持項目規范的及時更新以及設計者和驗證工程師之間有效的定期溝通極其重要。此外在Codasip,實現這一目標的另一個有效解決方案是執行由其他團隊成員進行的代碼審查。

Codasip使用的驗證技術和技巧,使我們能夠創建冗余,及時發現和修復漏洞并最終提供一流品質的RISC-V處理器!

審核編輯 :李倩

-

處理器

+關注

關注

68文章

19813瀏覽量

233617 -

驗證技術

+關注

關注

0文章

5瀏覽量

6290

原文標題:處理器驗證系列之五:為處理器驗證創建一個“瑞士奶酪模型”,以保證高效的驗證品質!

文章出處:【微信號:Codasip 科達希普,微信公眾號:Codasip 科達希普】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

硬件輔助驗證(HAV) 對軟件驗證的價值

筑牢汽車品質基石:深入剖析 DV 與 PV 驗證

芯華章以AI+EDA重塑芯片驗證效率

新思科技推出基于AMD芯片的新一代原型驗證系統

EE-218:為ADSP-TS201 TigerSHARC處理器編寫高效浮點FFT

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

為處理器驗證創建一個“瑞士奶酪模型”,以保證高效的驗證品質!

為處理器驗證創建一個“瑞士奶酪模型”,以保證高效的驗證品質!

評論