DDR3 地址線

DDR3為減少地址線,把地址線分為行地址線和列地址線,在硬件上是同一組地址線;地址線和列地址線是分時復用的,即地址要分兩次送出,先送出行地址,再送出列地址。

一般來說列地址線是10位,及A0...A9;行地址線數量根據內存大小,BANK數目,數據線位寬等決定(感覺也應該是行地址決定其他) ;

BANK

bank是存儲庫的意思,也就是說,一塊內存內部劃分出了多個存儲庫,訪問的時候指定存儲庫編號,就可以訪問指定的存儲庫,內存中劃分了多少個bank,要看地址線中有幾位BA地址,如果有兩位,說明有4個bank,如果有3位,說明有8個bank

DDR3 容量計算

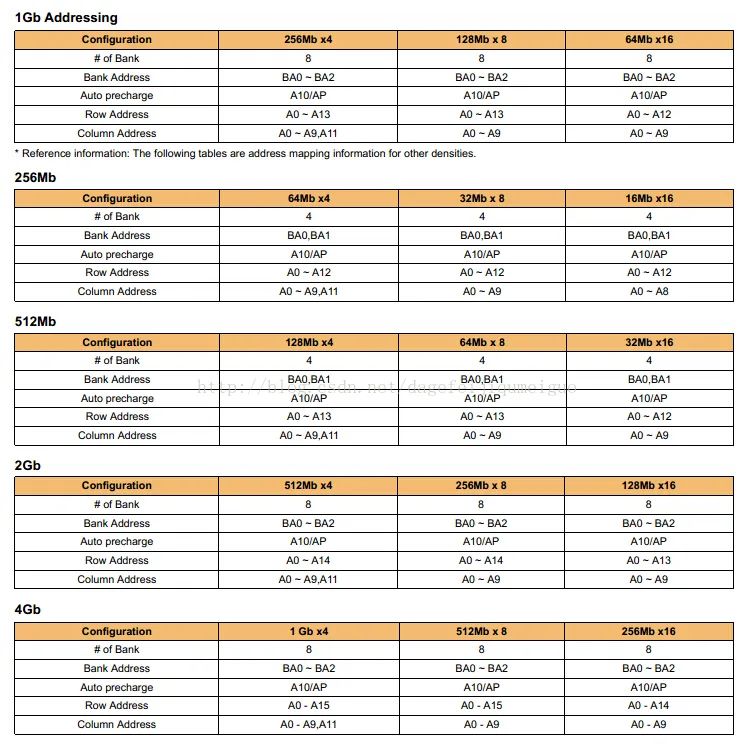

下面這張圖是芯片k4t1g164qf資料中截取的;以1Gb容量的DDR2顆粒為例(其他的類似);假設數據線位寬為16位,則看64Mb x 16這一列:

bank地址線位寬為3,及bank數目為 2^3=8;

行地址線位寬位13,及A0...A12;

列地址線位寬為10,及A0...A9;

有 2^3 * 2^13 * 2^10 = 2^26 =2^6Mb = 64Mb

再加上數據線,則容量為 64Mb x 16

-

DDR3

+關注

關注

2文章

284瀏覽量

43180 -

存儲

+關注

關注

13文章

4533瀏覽量

87488 -

容量計算

+關注

關注

0文章

6瀏覽量

6849

原文標題:DDR3地址和容量計算、Bank理解

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【RK3568+PG2L50H開發板實驗例程】FPGA部分 | DDR3 讀寫實驗例程

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據手冊

DDR3 SDRAM配置教程

關于DDR3地址的容量計算

關于DDR3地址的容量計算

評論