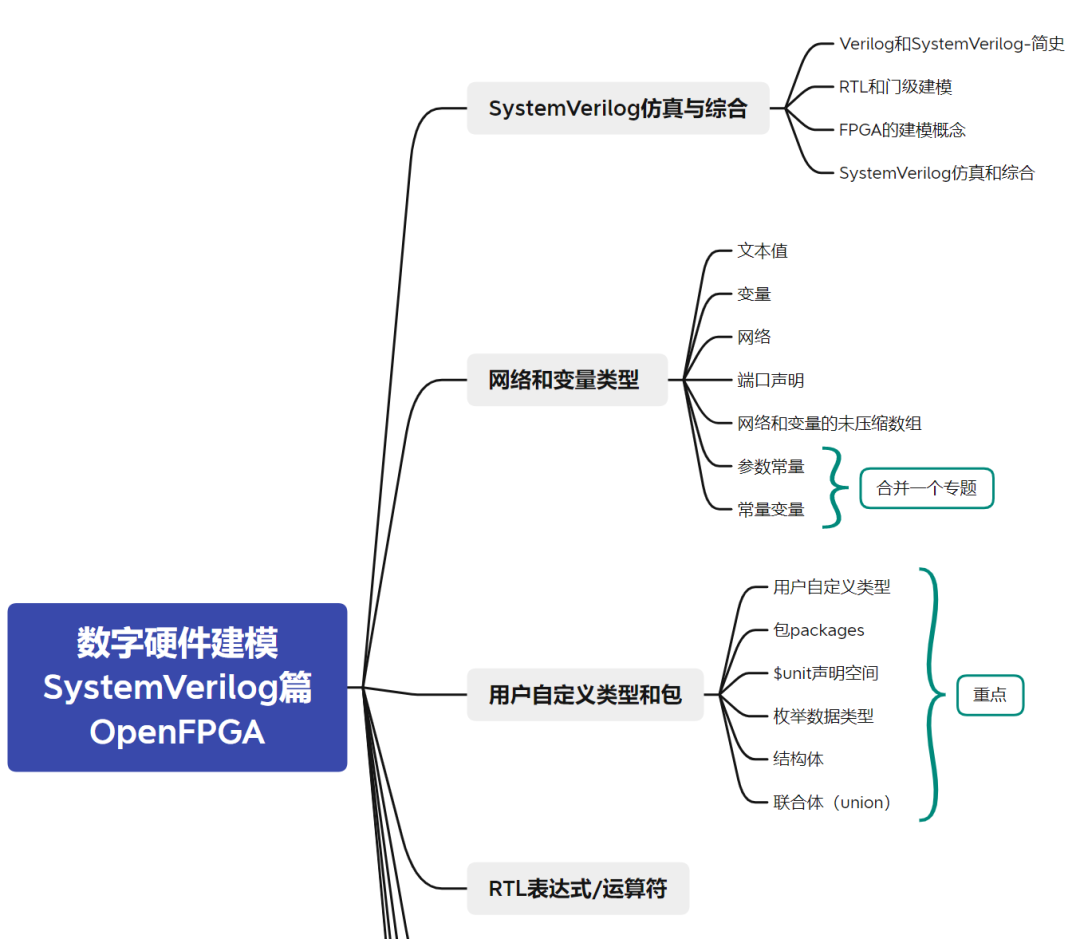

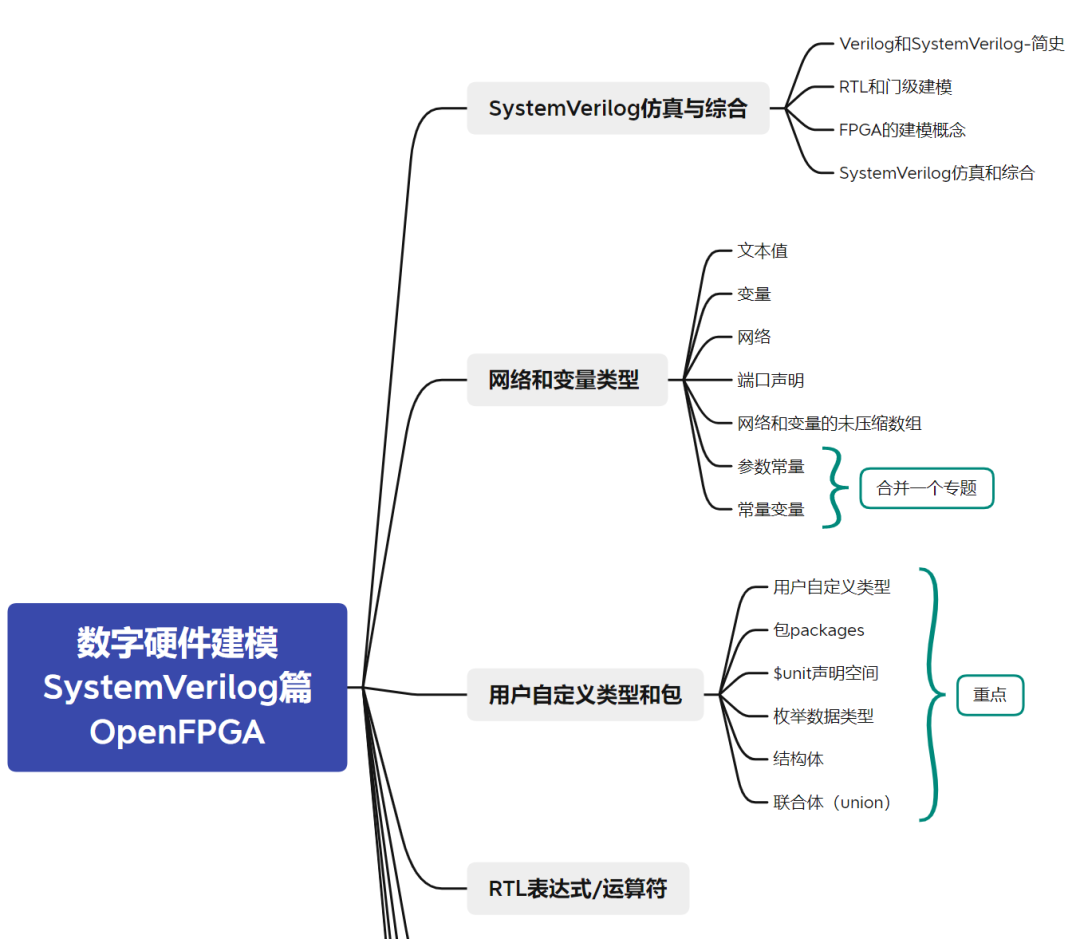

前面已經寫了大約10篇左右文章介紹了SV,效果不是特別理想,對于一些常規的概念還是比較好理解的,但是對于一些新的專業術語,翻譯的比較拗口還是比較難理解的,這是因為國內還沒有針對可綜合SystemVerilog系統的介紹,導致標準里的術語翻譯不精確,后續可能還是使用英語單詞來表示,然后用一些非專業術語去解釋,下面簡單總結一下這十幾篇內容。

最前面幾篇文章重點介紹SystemVerilog仿真與綜合概念及一些對比,總結如下:

SystemVerilog是硬件設計和驗證語言的IEEE行業標準。標準編號為IEEE 1800。SystemVerilog名稱將替換舊版Verilog名稱。SystemVerilog語言是原始Verilog硬件描述語言的完整超集。SystemVerilog是一種雙用途語言,用于描述數字硬件功能以及驗證測試臺。

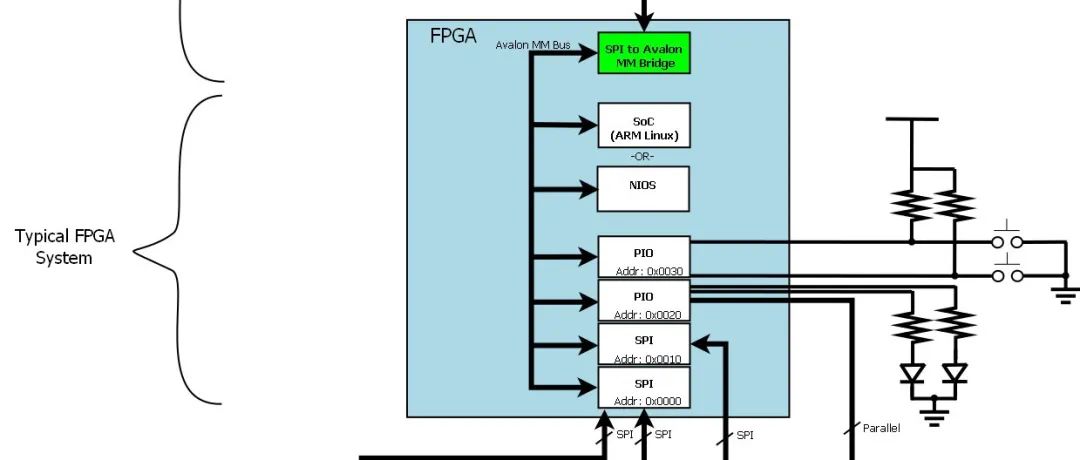

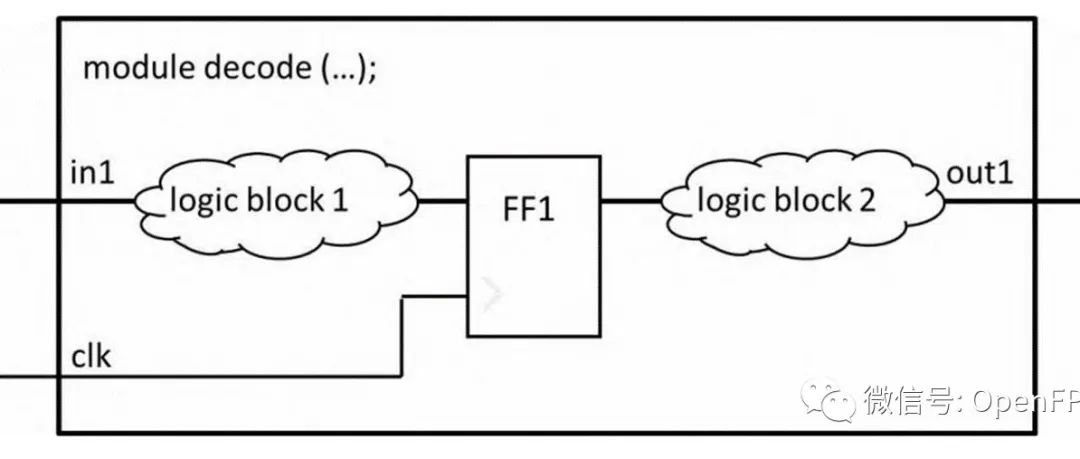

硬件行為可以在幾個抽象級別上表示,從非常詳細的門級模型到非常抽象的事務級模型。本系列的重點是在寄存器傳輸級別(RTL)編寫SystemVerilog模型。RTL模型表示基于周期的行為,很少或根本沒有提及如何在硅中實現功能。

SystemVerilog RTL模型如果編碼正確,可以進行仿真和綜合,仿真使用用戶定義的測試臺將激勵應用于設計輸入,并驗證設計功能是否符合預期。仿真對SystemVerilog語言的使用沒有任何限制。綜合將抽象的RTL功能轉換為詳細的門級實現。綜合編譯器限制了可以使用哪些SystemVeriIog語言結構以及如何使用這些結構。Lint checker工具可用于檢查RTL模型是否符合綜合編譯器的限制。

接下來完整的介紹了SV的數據類型:網絡和變量類型,總結如下:

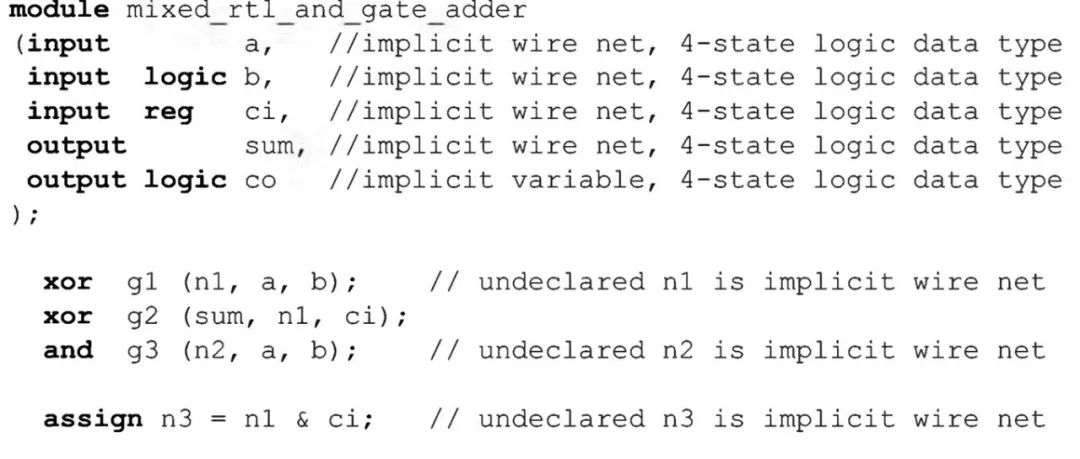

研究了SystemVerilog語言中預定義的內置類型和數據類型。重點是對編寫RTL模型有用的類型和數據類型,這些RTL模型將以最佳方式進行仿真和綜合。

SystemVerilog具有2-state和4-state數據類型。4-state數據類型的四值系統允許建模硬件行為值0、1和Z表示物理硬件。值X用于仿真不關心條件,其中設計工程師不關心物理硬件是否具有0或1值。仿真器還使用X值表示潛在問題,其中仿真無法確定實際邏輯門是否具有0、1或Z。SystemVerilog的2-state類型不應用于仿真硬件行為,因為它們沒有X值來表示仿真期間的潛在設計錯誤。

SystemVerilog網絡類型(如wire類型)用于將設計塊連接在一起。網絡始終使用4-state數據類型,并且當有多個源驅動同一網絡時,可以解析最終值。SystemVerilog變量類型用于接收賦值語句左側的值,并將存儲賦值=直到對變量進行另一次賦值。SystemVerilog有幾種網絡類型和變量數據類型。已經展示了聲明網絡和變量的語法,并討論了重要的語義規則。還討論了在RTL模型中如何正確使用這些不同的網絡和變量。

SystemVeriIog允許通過使用參數和localparam常量編寫可配置的模型。可以使用參數重寫(也稱為參數重新定義)為模塊的每個實例指定常數的唯一值。

優秀的 Verilog/FPGA開源項目介紹(二十二)- SystemVerilog常用可綜合IP模塊庫

談談Verilog和SystemVerilog簡史,FPGA設計是否需要學習SystemVerilog

SystemVerilog數字系統設計_夏宇聞 PDF

SystemVerilog(一)-RTL和門級建模

數字硬件建模-Verilog篇階段總結及SystemVerilog篇介紹

SystemVerilog(二)-ASIC和FPGA區別及建模概念

SystemVerilog(三)-仿真

FPGA的綜合和約束的關系

SystemVerilog(五)-文本值

SystemVerilog(六)-變量

SystemVerilog(七)-網絡

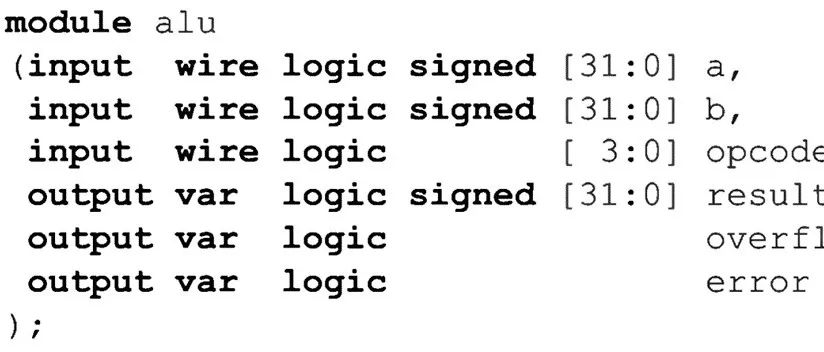

數字硬件建模SystemVerilog(八)-端口聲明

現在介紹完前兩級的內容,后續將介紹最重要的一章-《用戶自定義類型和包》。有什么問題可以后臺留言。

原文標題:SystemVerilog-階段性總結(一)

文章出處:【微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614032 -

IEEE

+關注

關注

7文章

388瀏覽量

48028 -

寄存器

+關注

關注

31文章

5421瀏覽量

123319 -

硬件

+關注

關注

11文章

3460瀏覽量

67188

原文標題:SystemVerilog-階段性總結(一)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB Layout 約束管理,助力優化設計

FPGA時序約束之設置時鐘組

【國產FPGA必備教程】——紫光同創FPGA圖像視頻教程,適用于小眼睛FPGA盤古全系列開發板

Design House與Fab的關系

時序約束一主時鐘與生成時鐘

FPGA的綜合和約束的關系

FPGA的綜合和約束的關系

評論