驗(yàn)證互連知識(shí)產(chǎn)權(quán) (IP) - 將片上系統(tǒng) (SoC) 中的內(nèi)核和 IP 塊粘合在一起的“粘合劑” - 對(duì)于高級(jí) SoC 變得更加復(fù)雜,這需要特殊的互連 IP 來執(zhí)行片上通訊功能。因此,這些 SoC 互連的功能和性能驗(yàn)證已經(jīng)達(dá)到了新的復(fù)雜程度。已經(jīng)開發(fā)了一些工具來簡(jiǎn)化驗(yàn)證,同時(shí)使設(shè)計(jì)工程師能夠在設(shè)計(jì)周期的早期發(fā)現(xiàn)和修復(fù)互連問題。

還記得工程師過去可以依靠總線在芯片中執(zhí)行片上通信功能的日子嗎?那些日子顯然已經(jīng)成為過去,尤其是在我們?nèi)找婊ヂ?lián)的世界需要我們的芯片提供更多功能的情況下。當(dāng)今先進(jìn)的 SoC 需要互連來充當(dāng) SoC 內(nèi)各種 IP 內(nèi)核的通信中心。考慮到主機(jī)和從機(jī)的數(shù)量、不同的協(xié)議、不同類型的事務(wù)以及涉及的多層拓?fù)洌?yàn)證 SoC 互連的功能和性能可能是一項(xiàng)復(fù)雜的任務(wù)。使用工具和技術(shù)的更全面的方法可以簡(jiǎn)化驗(yàn)證 SoC 互連功能和性能的過程。

通過功能驗(yàn)證防止意外

通過功能驗(yàn)證,設(shè)計(jì)人員希望確保多核芯片實(shí)現(xiàn)所需的功能,同時(shí)以相對(duì)順暢的方式處理錯(cuò)誤。從實(shí)際的角度來看,設(shè)計(jì)人員希望驗(yàn)證 SoC IP 塊以及芯片的互連。這里有兩個(gè)步驟。首先是通過驗(yàn)證 IP 驗(yàn)證 IP 塊是否正確實(shí)現(xiàn)了給定的接口協(xié)議,這可以警告任何協(xié)議違規(guī)。驗(yàn)證 IP 監(jiān)控仿真結(jié)果并根據(jù)協(xié)議規(guī)范執(zhí)行極端情況測(cè)試;在此過程中,帶有嵌入式斷言的驗(yàn)證 IP 可以自動(dòng)檢測(cè)協(xié)議違規(guī)。此外,IP 中的測(cè)試套件和驗(yàn)證計(jì)劃可以使驗(yàn)證過程快速結(jié)束。

使用互連驗(yàn)證 IP 塊的第二步是驗(yàn)證命令和數(shù)據(jù)是否會(huì)以正確的格式到達(dá)正確的目的地。設(shè)計(jì)人員需要注意諸如數(shù)據(jù)拆分、擴(kuò)大規(guī)模和縮小規(guī)模等問題。這很重要,因?yàn)榛ミB子系統(tǒng)上的不同接口使用不同的協(xié)議;例如,作為一系列 APB 傳輸進(jìn)入互連的數(shù)據(jù)事務(wù)可以在目標(biāo)端口作為 AXI 突發(fā)輸出。還應(yīng)驗(yàn)證諸如窺探對(duì)話、窺探傳播、窺探過濾器操作和跨緩存行等操作。換句話說,他們應(yīng)該確保高速緩存一致性互連正確地發(fā)揮其作為一致性管理器的作用。為了節(jié)省遠(yuǎn)程內(nèi)存訪問時(shí)間,相干互連窺探相關(guān)主設(shè)備的緩存,并根據(jù)它們的響應(yīng),確定是從緩存中返回請(qǐng)求的數(shù)據(jù)還是從遠(yuǎn)程內(nèi)存中返回請(qǐng)求的數(shù)據(jù),并相應(yīng)地更新相關(guān)主設(shè)備的緩存行狀態(tài)。這種行為是由一致性協(xié)議定義的。如果互連不遵循協(xié)議,系統(tǒng)將很快進(jìn)入非連貫狀態(tài)并很可能崩潰。

通過性能驗(yàn)證滿足帶寬和延遲目標(biāo)

性能驗(yàn)證是設(shè)計(jì)人員應(yīng)確保設(shè)計(jì)滿足其目標(biāo)帶寬和延遲水平的地方。考慮具有多個(gè)互連的 SoC 設(shè)計(jì),以防止局部流量影響設(shè)備的其余子系統(tǒng)。互連 IP 在這里發(fā)揮著重要作用,因?yàn)樗梢哉{(diào)整每個(gè)端口以獲得獨(dú)特的總線寬度、地址映射和時(shí)鐘速度。通常,還有一些機(jī)制可以調(diào)整帶寬和延遲,以調(diào)整每個(gè)域中的互連 IP。

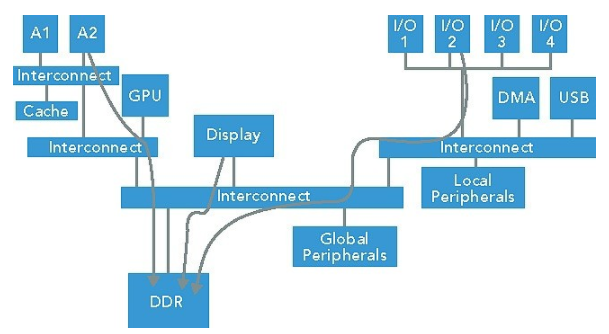

但是,仍然存在會(huì)發(fā)生流量沖突的情況,如圖 1所示。在這些情況下如何平衡流量?大多數(shù)系統(tǒng)沒有足夠的主存帶寬來容納同時(shí)處于活動(dòng)狀態(tài)的所有 IP 塊。重要的是防止一個(gè) IP 塊支配和壓倒其他 IP 塊;否則,系統(tǒng)性能會(huì)下降。在這種情況下,性能分析可能會(huì)有所幫助,從而最大限度地減少系統(tǒng)性能下降的影響。

圖 1:流量管理和系統(tǒng)性能。在此圖中,三個(gè)子系統(tǒng)正在嘗試同時(shí)訪問主存儲(chǔ)器。性能分析有助于評(píng)估 SoC 圖是否需要重新配置。

為了分析性能,設(shè)計(jì)人員需要比較來自不同 SoC 架構(gòu)或不同 SoC 用例的帶寬和延遲測(cè)量值。這種比較涉及對(duì)兩個(gè)或多個(gè)(通常是幾個(gè))SoC 架構(gòu)(或特定架構(gòu)的實(shí)現(xiàn))進(jìn)行建模、運(yùn)行仿真和測(cè)量性能,手動(dòng)執(zhí)行這些操作是不切實(shí)際的。畢竟,手動(dòng)工作將需要圍繞比較下的各種 SoC 架構(gòu)構(gòu)建測(cè)試平臺(tái)。對(duì)于復(fù)雜的 SoC(其中性能分析和調(diào)整最為重要),對(duì)于經(jīng)驗(yàn)豐富的工程師來說,創(chuàng)建必要的測(cè)試平臺(tái)可能需要幾天時(shí)間,而對(duì)于經(jīng)驗(yàn)不足的工程師來說則需要更長(zhǎng)的時(shí)間。

績(jī)效分析的五個(gè)重點(diǎn)領(lǐng)域

為了使績(jī)效分析盡可能有效和高效,您應(yīng)該努力將五個(gè)方面整合到流程中:

周期精確建模——利用周期精確度,邏輯仿真產(chǎn)生與在實(shí)際芯片中看到的具有相同時(shí)序的相同事件順序。周期精確的仿真模型包括在 SoC 設(shè)計(jì)過程中創(chuàng)建的 RTL 級(jí) Verilog 或 VHDL。

自動(dòng) RTL 生成——自動(dòng)生成的互連 RTL 是朝著創(chuàng)建完整的 SoC 周期精確模型邁出的一步。為了確定提供最佳整體性能的組合,設(shè)計(jì)人員需要能夠快速生成互連 IP 的多種變體。

驗(yàn)證 IP – 如前所述,驗(yàn)證 IP 有助于發(fā)現(xiàn)協(xié)議違規(guī)。

測(cè)試臺(tái)生成——自動(dòng)生成測(cè)試臺(tái)可以節(jié)省數(shù)周的時(shí)間,否則開發(fā)可能會(huì)花費(fèi)數(shù)周時(shí)間來創(chuàng)建互連測(cè)試環(huán)境。

深入分析——收集所有仿真數(shù)據(jù)(設(shè)計(jì)評(píng)估、測(cè)試臺(tái)和流量)的能力對(duì)于調(diào)試性能問題和確定設(shè)計(jì)更改可能如何影響帶寬和延遲是必要的。

圖形互連仿真比較

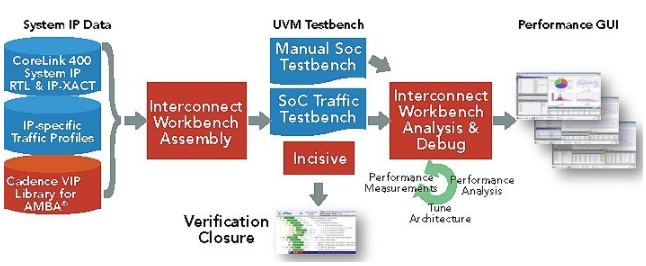

已經(jīng)開發(fā)了一種工具,它提供了一種圖形方式來比較互連仿真運(yùn)行,以便快速準(zhǔn)確地評(píng)估互連性能。Cadence Interconnect Workbench 有助于在設(shè)計(jì)周期的早期發(fā)現(xiàn)和修復(fù)互連問題,以達(dá)到 SoC 所需的帶寬和延遲水平。使用該工具,其流程如圖 2 所示,工程師可以拋開繁瑣的電子表格,利用帶有內(nèi)置過濾器的 GUI 來選擇主設(shè)備和/或從設(shè)備以及評(píng)估和執(zhí)行“假設(shè)”分析的路徑。GUI 可以讓您快速輕松地了解設(shè)計(jì)更改如何影響感興趣的仿真結(jié)果的帶寬和延遲。例如,工程師可以比較并找到特定用例或在單個(gè)配置上運(yùn)行的多個(gè)用例的理想配置。他們可以快速查看到每個(gè)從站的流量比例以及它們的延遲分布情況。實(shí)時(shí)過濾和分析功能消除了電子表格可能非常繁瑣的過程。

Interconnect Workbench 與 Cadence Interconnect Validator 集成,這是一個(gè)驗(yàn)證 IP 組件,可收集所有事務(wù)并在數(shù)據(jù)通過 SoC 互連結(jié)構(gòu)時(shí)驗(yàn)證數(shù)據(jù)的正確性和完整性。互連驗(yàn)證器連接到所有接口級(jí)驗(yàn)證 IP 實(shí)例(它們正在監(jiān)視 IP 塊的正確協(xié)議行為),因此對(duì)進(jìn)出互連的數(shù)據(jù)和命令有深入的了解。通過匹配這些數(shù)據(jù),該工具可以驗(yàn)證數(shù)據(jù)是否被傳送到正確的目的地。如果互連不遵循協(xié)議,則會(huì)發(fā)出錯(cuò)誤。

圖 2:通過 Cadence Interconnect Workbench 的數(shù)據(jù)流。在左側(cè),RTL、驗(yàn)證 IP 和流量模式描述移至工具中,該工具會(huì)自動(dòng)生成用于仿真的測(cè)試平臺(tái)。當(dāng)生成 SoC 的其他變體時(shí),該工具還會(huì)生成其他測(cè)試平臺(tái)。性能 GUI 提供了模擬結(jié)果的概覽。

高效且有效的互連驗(yàn)證

面對(duì)持續(xù)不斷的上市時(shí)間壓力和日益復(fù)雜的 SoC 設(shè)計(jì),很難找到不想從設(shè)計(jì)周期中縮短時(shí)間的工程師。特別是在高級(jí)節(jié)點(diǎn),驗(yàn)證 SoC 互連已成為一個(gè)耗時(shí)的步驟。但是,工具現(xiàn)在可以高效且有效地執(zhí)行周期精確的性能分析和互連驗(yàn)證。

作者:Nick Heaton,Avi Behar

審核編輯:郭婷

-

芯片

+關(guān)注

關(guān)注

459文章

52160瀏覽量

436055 -

soc

+關(guān)注

關(guān)注

38文章

4335瀏覽量

221647 -

GUI

+關(guān)注

關(guān)注

3文章

676瀏覽量

40738

發(fā)布評(píng)論請(qǐng)先 登錄

新思科技VSO.ai如何顛覆芯片驗(yàn)證

半導(dǎo)體芯片中的互連層次

是德科技推出多功能1.6T以太網(wǎng)平臺(tái)和互連測(cè)試系統(tǒng)

【「芯片通識(shí)課:一本書讀懂芯片技術(shù)」閱讀體驗(yàn)】芯片如何設(shè)計(jì)

研究透視:芯片-互連材料

芯華章推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

國產(chǎn)EDA公司芯華章科技推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

如何優(yōu)化SOC芯片性能

TMS320C64x DSP外圍組件互連(PCI)性能

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗(yàn)證之路

SoC芯片是什么?它有哪些功能和應(yīng)用?

探索通用互連解決方案的強(qiáng)大之處

SoC布局中各種IC簡(jiǎn)介

大規(guī)模 SoC 原型驗(yàn)證面臨哪些技術(shù)挑戰(zhàn)?

SoC互連的功能和性能驗(yàn)證

SoC互連的功能和性能驗(yàn)證

評(píng)論