文章來源:半導體與物理

原文作者:jjfly686

本文介紹了芯片中金屬互連線的各個層級的不同設計。

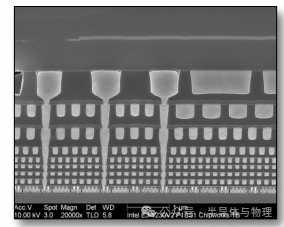

在半導體芯片中,數十億晶體管需要通過金屬互連線(Interconnect)連接成復雜電路。隨著制程進入納米級,互連線的層次化設計成為平衡性能、功耗與集成度的關鍵。芯片中的互連線按長度、功能及材料分為多個層級,從全局電源網絡到晶體管間的納米級連接,每一層都有獨特的設計考量。

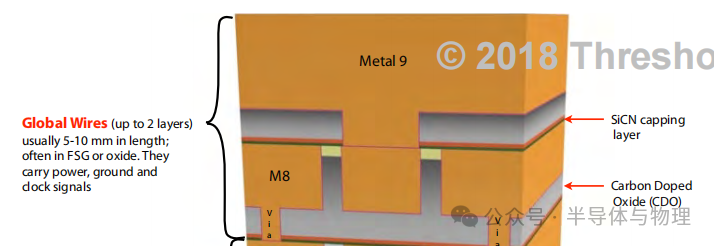

全局互連(Global Wires)

層級范圍:通常為最高層金屬(如M8、M9),最多2層。

長度:5-10mm,覆蓋整個芯片區域。

材料:采用摻氟硅酸鹽玻璃(FSG,k≈3.5)或傳統氧化物(SiO?,k≈3.9)作為絕緣介質,銅(Cu)為導體。

設計優勢:高層金屬厚度可達1-3μm,電流承載能力是低層金屬的2-3倍,適合大電流傳輸。

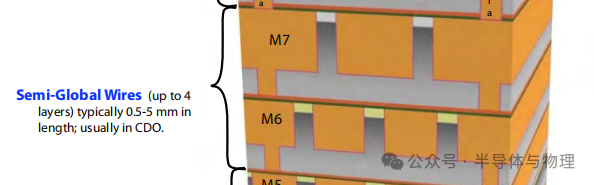

半全局互連(Semi-Global Wires)

層級范圍:中間層金屬(如M4-M7),最多4層。

長度:0.5-5mm,連接不同功能模塊(如CPU核心與緩存)。

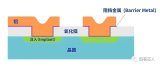

材料:絕緣介質為碳摻雜硅氧化物(CDO,k≈2.8-3.2),銅互連搭配氮化鉭(TaN)阻擋層。

性能優化:CDO的碳摻雜降低介電常數,減少信號串擾,同時保持機械強度。

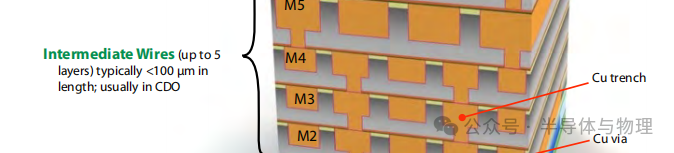

中間互連(Intermediate Wires)

層級范圍:低層金屬(如M2-M3),最多5層。

長度:<100μm,實現模塊內局部連接。

材料:同樣使用CDO介質,銅互連需更薄的阻擋層(1-2nm TaN)。

工藝挑戰:深寬比>5:1的通孔需原子層沉積(ALD)銅籽晶層,避免電鍍空洞。

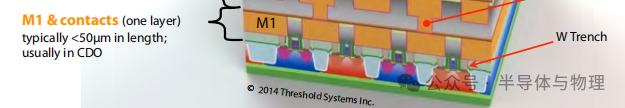

局部互連(M1 & Contacts)

層級范圍:最底層金屬(M1),直接連接晶體管源/漏極。

長度:<50μm,納米級線寬(10-20nm)。

材料:CDO介質,鈷(Co)或釕(Ru)逐步替代銅,減少電阻飆升問題。

關鍵技術:選擇性外延填充接觸孔,結合化學機械拋光(CMP)確保平坦化。

-

芯片

+關注

關注

459文章

52013瀏覽量

434572 -

半導體

+關注

關注

335文章

28435瀏覽量

230890 -

晶體管

+關注

關注

77文章

9929瀏覽量

140374

原文標題:半導體芯片中的互連層次

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片,集成電路,半導體含義

芯片,半導體,集成電路,傻傻分不清楚?

半導體芯片內部結構詳解

半導體元件與芯片的區別有哪些

半導體元件與芯片的區別

半導體封裝革新之路:互連工藝的升級與變革

半導體芯片中的互連層次

半導體芯片中的互連層次

評論