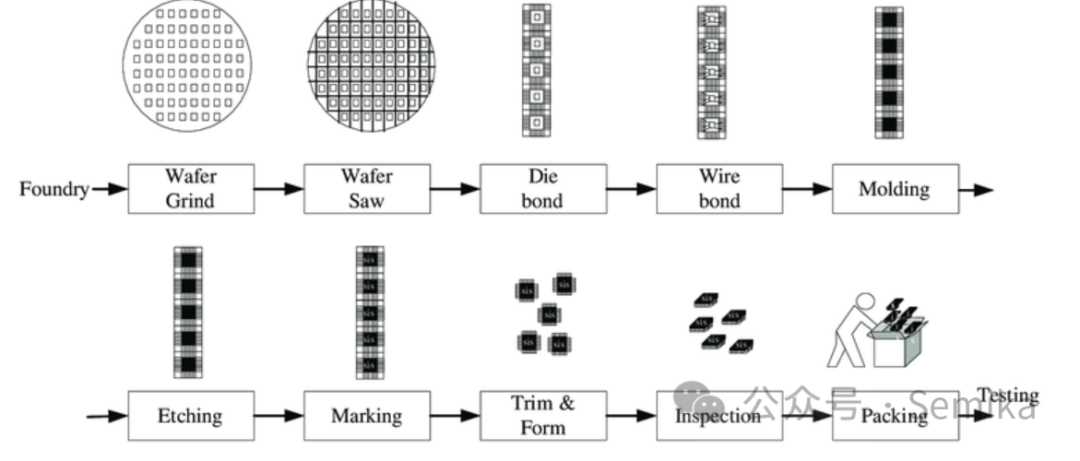

在半導體產業中,封裝是連接芯片與外界電路的關鍵環節,而互連工藝則是封裝中的核心技術之一。它負責將芯片的輸入輸出端口(I/O端口)與封裝基板或外部電路連接起來,實現電信號的傳輸與交互。本文將詳細介紹半導體封裝中的互連工藝,包括其主要分類、技術特點、應用場景以及未來的發展趨勢。

一、互連工藝概述

半導體封裝中的互連工藝是連接芯片與封裝基板或外部電路的關鍵環節。在集成電路中,各個器件或模塊之間需要進行信號傳輸和電力供應,這就需要使用互連技術來實現。互連工藝的好壞直接影響器件的電性能、可靠性和成本。因此,它是半導體封裝技術中不可或缺的一部分。

二、主要互連技術分類

1. 引線鍵合(Wire Bonding)

原理:

引線鍵合技術是通過金屬線(如金線、銅線或鋁線)將芯片的焊盤(Pad)與封裝基板的引腳連接。這種連接方式具有設備成本低、工藝成熟的特點,非常適合低密度封裝。

技術分類:

- 熱壓焊(Thermocompression Bonding):利用高溫加壓實現金屬擴散鍵合,常用于金線。

- 超聲焊(Ultrasonic Bonding):利用超聲波振動清潔表面并實現鍵合,適合鋁線。

- 熱超聲焊(Thermosonic Bonding):結合熱壓與超聲技術,主要用于金線。

金屬線材料:

- 金線:具有高導電性、抗腐蝕等優點,但成本較高。

- 銅線:低成本、高機械強度,但易氧化。

- 鋁線:用于低端封裝,成本低但導電性較差。

優點:

- 設備成本低,工藝成熟。

- 適合低密度封裝。

缺點:

- 互連密度低,高頻性能受限。

- 線長影響信號延遲。

2. 倒裝芯片(Flip Chip)

原理:

倒裝芯片技術是將芯片正面朝下,通過凸點(Bump)直接與基板焊接。這種連接方式具有高密度、短互連路徑、優異的高頻性能等優點。

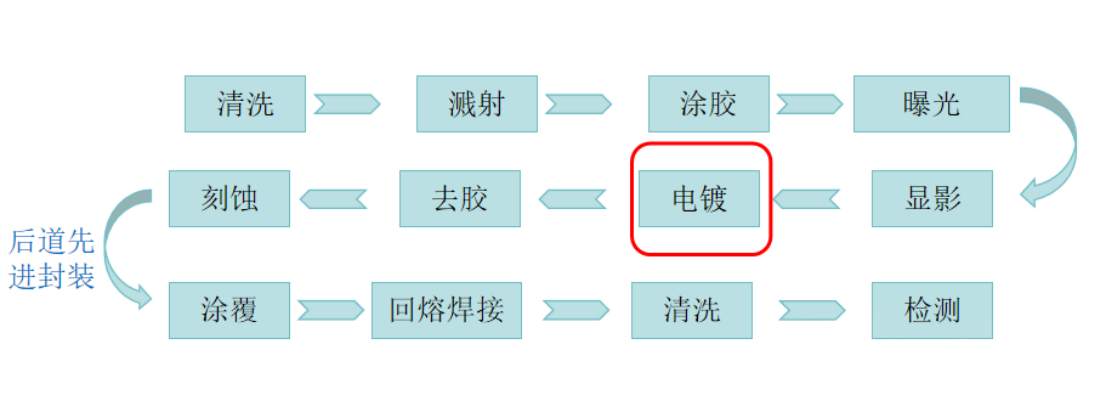

工藝流程:

- 晶圓凸塊制備:在芯片焊盤上制作金屬凸點,如焊料、銅柱等。

- 切割與倒裝:將晶圓切割為單個芯片,翻轉后對準基板焊盤。

- 回流焊接:加熱使焊料熔化形成電連接。

- 底部填充(Underfill):填充環氧樹脂以緩解熱應力。

凸點材料:

- 焊料凸點(Sn-Ag-Cu等):成本低,但需高溫回流。

- 銅柱凸點(Cu Pillar):高頻性能優,用于高密度互連。

優點:

- 高密度、短互連路徑。

- 優異的高頻性能。

缺點:

- 工藝復雜,需精準對準。

- 成本較高。

3. 晶圓級封裝(Wafer-Level Packaging, WLP)

原理:

晶圓級封裝技術是在晶圓階段完成封裝和互連,切割后直接得到成品芯片。這種技術具有封裝尺寸小、生產效率高等優點。

關鍵技術:

- 重分布層(RDL):通過光刻和電鍍在芯片表面重新布線,擴展焊盤位置。

- 銅柱凸點(Cu Pillar):實現高密度垂直互連。

應用場景:

- 適用于移動設備(如CIS、射頻芯片)等。

優點:

- 封裝尺寸小,生產效率高。

- 適用于大規模生產。

缺點:

- 技術復雜度較高。

- 需要高精度的設備支持。

4. 扇出型晶圓級封裝(Fan-Out WLP, FOWLP)

原理:

扇出型晶圓級封裝技術是將芯片嵌入環氧模塑料(EMC)中,通過RDL將焊盤扇出到更大區域。這種技術可以支持更多I/O,降低封裝成本。

優勢:

- 支持更多I/O。

- 無需基板,降低成本。

典型應用:

5. 硅通孔(Through-Silicon Via, TSV)

原理:

硅通孔技術是在芯片或硅中介層上制作垂直導電通道,用于3D堆疊封裝。這種技術可以極大地縮短芯片間的互連長度,減小信號延遲和功耗。

工藝流程:

- 深孔刻蝕:利用干法刻蝕在硅中形成通孔。

- 絕緣層沉積(SiO?或聚合物):隔離硅基體與導電材料。

- 阻擋層/種子層(Ti/Cu):防止金屬擴散并輔助電鍍。

- 電鍍填充:用銅填充通孔。

導電材料:

- 金:高可靠性,但成本高。

- 銅:主流選擇,導電性好,需防氧化。

- 焊料合金(Sn-Ag-Cu):用于倒裝芯片,熔點可調。

應用場景:

- 高帶寬存儲器(HBM)、3D IC集成等。

三、互連工藝的技術特點與應用場景

1. 技術特點

- 引線鍵合:設備成本低,工藝成熟,但互連密度低,高頻性能受限。

- 倒裝芯片:高密度、短互連路徑、優異的高頻性能,但工藝復雜,成本較高。

- 晶圓級封裝:封裝尺寸小,生產效率高,適用于大規模生產,但技術復雜度較高。

- 扇出型晶圓級封裝:支持更多I/O,降低成本,適用于高端芯片封裝。

- 硅通孔:實現3D堆疊封裝,縮短互連長度,減小信號延遲和功耗,但成本較高。

2. 應用場景

- 引線鍵合:適用于對成本敏感、互連密度要求不高的應用場景,如消費電子、家電等。

- 倒裝芯片:適用于對高頻性能、高密度互連要求高的應用場景,如處理器、GPU、高速接口芯片等。

- 晶圓級封裝:適用于大規模生產、對封裝尺寸要求高的應用場景,如移動設備、可穿戴設備等。

- 扇出型晶圓級封裝:適用于高端芯片封裝,如處理器、5G射頻模塊等。

- 硅通孔:適用于需要高密度集成、高速數據傳輸的應用場景,如高帶寬存儲器、3D IC集成等。

四、互連工藝的發展趨勢

1. 高密度、高頻性能提升

隨著電子產品向小型化、高性能化方向發展,對半導體封裝中的互連工藝提出了更高的要求。未來,互連工藝將向高密度、高頻性能提升方向發展。例如,銅柱凸點、RDL技術等將得到更廣泛的應用,以滿足對高頻性能、高密度互連的要求。

2. 先進封裝技術的興起

先進封裝技術如3D封裝、Chiplet技術等正在興起。這些技術需要更高效的互連工藝來支持。例如,硅通孔技術是實現3D封裝的關鍵工藝之一,未來將得到更廣泛的應用。同時,混合鍵合(Hybrid Bonding)等新型互連技術也在不斷發展,將進一步提升封裝的密度和性能。

3. 自動化與智能化升級

隨著人工智能、大數據等技術的發展,半導體封裝行業也將迎來自動化與智能化升級。通過集成人工智能技術,可以不斷優化焊接參數、實現實時工藝監控,從而提高封裝質量和生產效率。例如,Wire Bonder設備正在向自動化、智能化方向發展,以滿足對高精度、高效率封裝的需求。

4. 環保與可持續發展

環保與可持續發展是全球關注的熱點話題。半導體封裝行業也將積極響應這一趨勢,推動綠色封裝技術的發展。例如,研究并應用新型焊接材料(如銅線替代金線)以減少貴金屬的使用;開發環保型封裝材料以減少對環境的影響等。

五、結論

半導體封裝中的互連工藝是連接芯片與外界電路的關鍵環節,其好壞直接影響器件的電性能、可靠性和成本。隨著電子產品向小型化、高性能化方向發展,對互連工藝提出了更高的要求。未來,互連工藝將向高密度、高頻性能提升、先進封裝技術興起、自動化與智能化升級以及環保與可持續發展等方向發展。半導體封裝企業需要密切關注市場動態和技術發展趨勢,不斷創新和優化互連工藝,以滿足市場對高性能、高可靠性、低成本封裝的需求。

在半導體封裝領域,互連工藝的發展不僅關系到單個芯片的性能和可靠性,還對整個電子產品的性能、尺寸和成本產生重要影響。因此,半導體封裝企業需要加強技術研發和創新能力,不斷提升互連工藝的水平和競爭力。同時,政府和社會各界也應加大對半導體封裝技術的支持和投入,共同推動半導體產業的發展和進步。

此外,隨著全球半導體市場的競爭日益激烈,半導體封裝企業需要不斷提升自身的核心競爭力和市場響應速度。通過加強技術研發、優化生產流程、提高產品質量和服務水平等措施,可以在激烈的市場競爭中占據有利地位。同時,加強與國際先進企業的合作與交流也是提升半導體封裝技術水平的重要途徑之一。通過借鑒國際先進經驗和技術成果,可以加快

-

芯片

+關注

關注

459文章

52169瀏覽量

436114 -

封裝

+關注

關注

128文章

8494瀏覽量

144781 -

半導體封裝

+關注

關注

4文章

289瀏覽量

14287

發布評論請先 登錄

半導體封裝工藝流程的主要步驟

提供半導體工藝可靠性測試-WLR晶圓可靠性測試

半導體封裝:索尼FCB - EV9520L機芯與SDI編碼板的協同革新

半導體封裝中的裝片工藝介紹

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

半導體封裝的主要類型和制造方法

倒裝封裝(Flip Chip)工藝:半導體封裝的璀璨明星!

半導體封裝革新之路:互連工藝的升級與變革

半導體封裝革新之路:互連工藝的升級與變革

評論