任何系統(tǒng)或 SoC 架構(gòu)師最關(guān)心的是風(fēng)險以及如何降低風(fēng)險。他們不禁要問:

在具有強(qiáng)化系統(tǒng)功能的產(chǎn)品投放市場之前,標(biāo)準(zhǔn)會發(fā)生變化嗎?

如果新引入的功能不能完全滿足需求怎么辦?

設(shè)計(jì)如何經(jīng)得起未來考驗(yàn)?

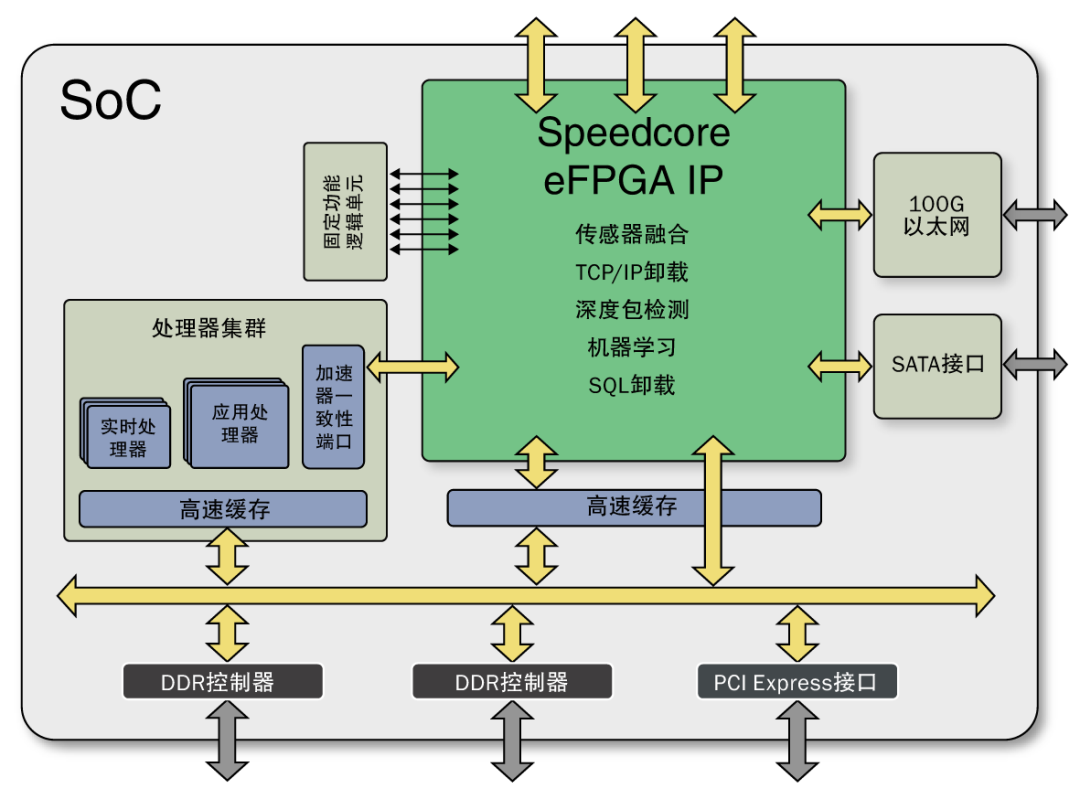

傳統(tǒng)上,系統(tǒng)架構(gòu)師會嘗試將設(shè)計(jì)中存在風(fēng)險的部分與可編程邏輯隔離開來。通常,獨(dú)立的 FPGA 無法提供所需的性能或滿足系統(tǒng)功耗和成本目標(biāo)。進(jìn)入嵌入式 FPGA (eFPGA),這是 SoC 設(shè)計(jì)人員在降低風(fēng)險的同時實(shí)現(xiàn)設(shè)計(jì)目標(biāo)的秘密武器。與使用獨(dú)立 FPGA 相比,在 SoC 中添加 eFPGA 可實(shí)現(xiàn)更靈活的設(shè)計(jì)、更低的功耗、更高的性能和更低的整體系統(tǒng)成本。

選擇 eFPGA 而不是 FPGA 的優(yōu)勢有很多。首先,與獨(dú)立 FPGA 相比,eFPGA 提供了更小的裸片面積,因?yàn)槿∠嗽试S PCB 上芯片到芯片連接的整個 I/O 功能,并且嵌入式結(jié)構(gòu)的尺寸專門針對應(yīng)用需求進(jìn)行了調(diào)整。由于 eFPGA 的芯片面積最小化,因此 SoC 的額外成本很小。

通過放棄獨(dú)立的 FPGA 并將可編程邏輯功能嵌入作為查找表、存儲器和 DSP 塊的個性化組合,eFPGA 在信號延遲、帶寬、延遲、功率和成本方面提供了根本性的改進(jìn)。電路板設(shè)計(jì)變得更容易,同時降低了電源和冷卻要求,提高了系統(tǒng)可靠性。從成本和組件數(shù)量的角度來看,系統(tǒng) BoM 都得到了改進(jìn),因?yàn)榉至⑹?FPGA 及其所有支持設(shè)備(包括電平轉(zhuǎn)換器、穩(wěn)壓器和旁路電容器)都被淘汰了,并且顯著節(jié)省了 PCB 空間。

在許多情況下,系統(tǒng)架構(gòu)師將定義他或她自己的自定義模塊功能,連同標(biāo)準(zhǔn)邏輯、嵌入式存儲器和 DSP 模塊一起包含在 eFPGA 中。這些定制塊與 LUT、RAM 和 DSP 的傳統(tǒng)構(gòu)建塊一起集成到邏輯結(jié)構(gòu)中,通過添加優(yōu)化的功能以減少面積和/或提高目標(biāo)應(yīng)用的性能,從而提高 eFPGA 的能力。

在計(jì)算工作量相當(dāng)大的人工智能 (AI) 應(yīng)用程序中,訓(xùn)練和推理方面的需求都在不斷發(fā)展。要在市場上推出專用于特定應(yīng)用的定制 ASIC,需要大量的財(cái)務(wù)資源和上市時間。當(dāng)芯片上市時,系統(tǒng)架構(gòu)師可能已經(jīng)在考慮實(shí)現(xiàn)當(dāng)前 AI 算法的優(yōu)化版本,這在 ASIC 流片后是不可能的。與 ASIC 相比,傳統(tǒng)的 FPGA 盡管不能理想地滿足未來的 AI 要求,但仍將繼續(xù)以更高的靈活性和可編程性來填補(bǔ)這一空白。

系統(tǒng)架構(gòu)師一致認(rèn)為,eFPGA 集成是一個成功的主張,它可以使 SoC 或 ASIC 適應(yīng)廣泛的高性能計(jì)算密集型應(yīng)用,包括人工智能和機(jī)器學(xué)習(xí)、5G 無線、數(shù)據(jù)中心、汽車和高性能計(jì)算 (HPC) )。

審核編輯:郭婷

-

dsp

+關(guān)注

關(guān)注

556文章

8157瀏覽量

357503 -

FPGA

+關(guān)注

關(guān)注

1645文章

22049瀏覽量

618389 -

存儲器

+關(guān)注

關(guān)注

38文章

7651瀏覽量

167380

發(fā)布評論請先 登錄

ADI收購了一家eFPGA公司,可重構(gòu)芯片成為FPGA發(fā)展新風(fēng)向?

PLL技術(shù)在FPGA中的動態(tài)調(diào)頻與展頻功能應(yīng)用

Microchip發(fā)布PolarFire Core FPGA和SoC產(chǎn)品

FPGA在AI方面有哪些應(yīng)用

SOLIDWORKS 2025更靈活的零件建模

FPGA 在人工智能中的應(yīng)用

Achronix Speedcore eFPGA的特性和功能

在SoC中添加eFPGA可實(shí)現(xiàn)更靈活的設(shè)計(jì)

在SoC中添加eFPGA可實(shí)現(xiàn)更靈活的設(shè)計(jì)

評論