楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence? 數字全流程獲得了 GlobalFoundries (GF) 12LP/12LP+ 工藝平臺認證,以推動移動和消費市場的航空航天、超大規模計算、人工智能、移動和消費電子應用的設計。此項認證證明,Cadence 數字全流程滿足了 GF 為12LP/12LP+ 工藝平臺規定的所有精度、集成度和結果質量 (QoR) 標準,使雙方的共同客戶能夠更快地實現功耗、性能和面積 (PPA) 目標,并以更短的設計周期向市場交付新產品。

Cadence 的工具針對 GF 12LP/12LP+ 工藝平臺進行了優化,并使用行業標準的高效處理器內核進行了認證。通過認證的工具包括 Innovus? 設計實現系統、Genus? 綜合解決方案、Tempus? 時序簽核解決方案、Voltus? IC 電源完整性解決方案、Quantus? 提取解決方案、Litho Physical Analyzer (LPA) 光刻物理分析工具和 Pegasus? 驗證系統。

數字全流程通過 Cadence iSpatial 技術為 GF 12LP/12LP+ 用戶提供了額外的優勢,使其可使用通用用戶界面和數據庫從 Genus 物理綜合無縫過渡到 Innovus 設計實現。該流程還提供了統一的實現、時序和 IR 簽核引擎,通過同時完成所有物理、時序和可靠性目標的設計收斂,提供了增強的簽核收斂。

“Cadence 數字全流程面向我們的 12LP/12LP+ 工藝平臺獲得的認證,驗證了物理實現和簽核方法的準確性。” GF 設計支持副總裁 Richard Trihy 表示,“通過與 Cadence 的合作,我們可以為客戶提供一個值得信賴的解決方案,以加快設計實現過程,這對于打造新興航空航天、超大規模計算和人工智能應用,并希望快速向市場交付新產品的客戶來說尤為關鍵。”

“通過我們的數字全流程提供的集成和創新,使用 GF 12LP/12LP+ 工藝平臺的客戶可以信心十足地專注于實現 PPA 目標。” Cadence 公司數字與簽核事業部產品總監 Kam Kittrell 表示,“GF 在 Cadence 數字全流程上進行了全面的關聯檢查,給用戶提供了額外的保障,確保他們可以快速實現高性能設計,以便在各自的市場上保持競爭力。”

Cadence 數字全流程提供了更好的可預測性和更快的設計收斂途徑,支持 Cadence 的智能系統設計 (Intelligent System Design?) 戰略,旨在實現 SoC 卓越設計。

-

處理器

+關注

關注

68文章

19893瀏覽量

235181 -

Cadence

+關注

關注

67文章

975瀏覽量

144401 -

人工智能

+關注

關注

1806文章

49014瀏覽量

249451

發布評論請先 登錄

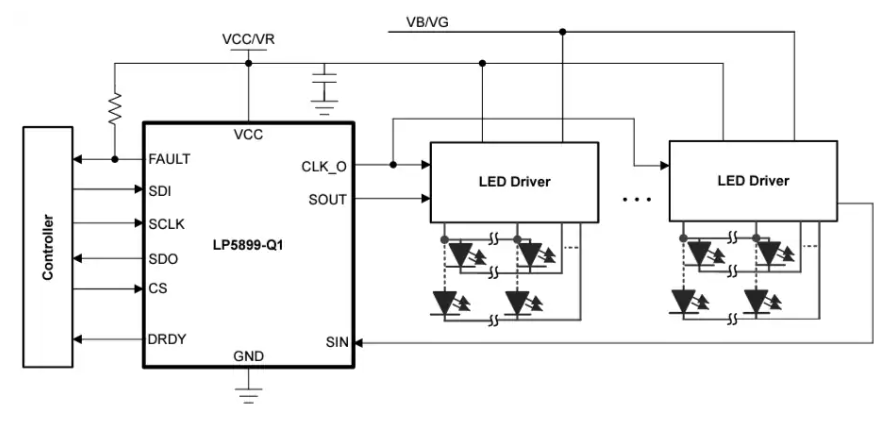

Texas Instruments LP5899/LP5899-Q1 LED驅動器數據手冊

【安裝教程】凌科LP-12系列90°工業級連接器安裝詳解

智簡連接!凌科LP-12 系列90°工業級連接器開啟高效運維新時代

上新 | 原創專利,巨省空間,LP-12系列90°工業級連接器新品隆重上市

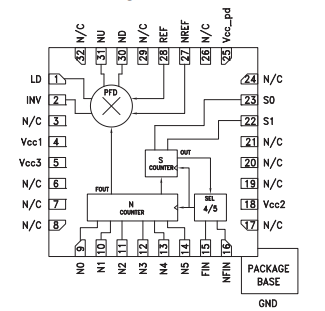

HMC698LP5/698LP5E 7GHz整數N分頻頻率合成器SMT技術手冊

12V1A隔離電源芯片LP3669CS

LP3718BSL芯茂微12V1A自供電PSR控制芯片

LP3783B貼片5V/2.4A 12W隔離電源芯片 替代 MT3612B

LP2801A/B/C/D/E 非隔離AC-DC電源芯片方案

為 AM570x 供電的 LP87332D 和 LP873220 用戶指南

西門子與GlobalFoundries達成進一步合作

LP3799-FBC-B,TO-220F-6隔離型開關電源芯片

使用LP87522E-Q1和LP873244-Q1的AC8015電源設計

LP8864-Q1 LP8864S-Q1 LP8866-Q1和LP8866S-Q1診斷說明和故障處理程序

Cadence? 數字全流程獲(GF) 12LP/12LP+工藝平臺認證

Cadence? 數字全流程獲(GF) 12LP/12LP+工藝平臺認證

評論