信息娛樂(lè)和儀表板系統(tǒng)通常需要多個(gè)時(shí)鐘:處理器時(shí)鐘、PCI Express 時(shí)鐘、USB 時(shí)鐘等——每個(gè)時(shí)鐘都有特定的頻率。在信息娛樂(lè)和儀表板應(yīng)用所需的所有時(shí)鐘中,LCD 面板點(diǎn)時(shí)鐘可能是最難實(shí)現(xiàn)的。目標(biāo)點(diǎn)時(shí)鐘頻率由 LCD 面板的構(gòu)造參數(shù)決定,例如分辨率、刷新率、活動(dòng)/非活動(dòng)像素比等。盡管存在標(biāo)準(zhǔn)的點(diǎn)時(shí)鐘頻率(例如 27 MHz 或 148.5 MHz),但某些 LCD 面板需要非標(biāo)準(zhǔn)頻率。我們以兩個(gè)隨機(jī)值為例,30.123 MHz 和 40.456 MHz。

傳統(tǒng)上,晶體振蕩器 (XO) 用于生成系統(tǒng)內(nèi)的每個(gè)時(shí)鐘。但某些頻率(例如我們的 30.123 MHz 和 40.456 MHz 示例)可能難以采購(gòu)或價(jià)格昂貴。

當(dāng)今的設(shè)計(jì)可以依靠集成的可編程時(shí)鐘發(fā)生器(例如汽車級(jí)VersaClock? 6E 5P49V60)來(lái)解決這個(gè)問(wèn)題。5P49V60 最多可生成 5 個(gè)不同的頻率,最高可達(dá) 350 MHz。由于采用小數(shù)輸出分頻器 (FOD) PLL 技術(shù),該器件適用于生成我們示例中的 30.123 MHz 和 40.456 MHz。

讓我們退后一步,更詳細(xì)地探索 PLL(鎖相環(huán))技術(shù)。PLL 由相位比較器、低通濾波器、壓控振蕩器 (VCO) 以及反饋分頻器 M 和(在 Versaclock 6E 的情況下)四個(gè)輸出分頻器 N1、N2、N3 和 N4 組成。PLL 調(diào)整 VCO 頻率,使相位比較器的兩個(gè)輸入“看到”相同的頻率。如果來(lái)自晶體的信號(hào),例如,25 MHz,連接到相位比較器的一個(gè)輸入端,而 VCO 的輸出,除以因子 M=100,連接到相位比較器的另一個(gè)輸入端,則PLL 將根據(jù) fVCO = 2500 MHz 的 VCO 頻率自行調(diào)整。適用于 VersaClock 6E 的 VCO 頻率范圍為 2500 MHz 至 2700 MHz。

鎖相環(huán)架構(gòu)

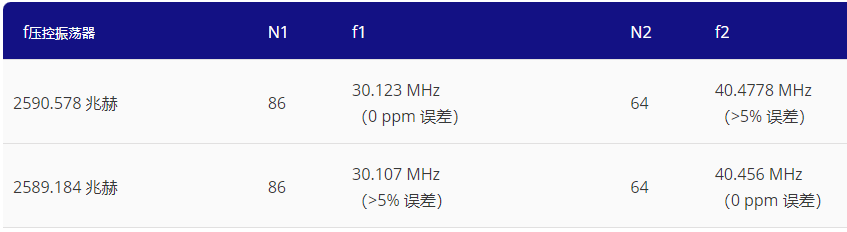

傳統(tǒng) PLL 的分頻器只能具有整數(shù)值。可以通過(guò)以下方式生成我們的示例頻率 30.123 和 40.456 MHz:(請(qǐng)注意,確實(shí)存在其他可能性)

正如我們所看到的,生成具有足夠低誤差的輸出頻率可能很困難。此外,我們只考慮了整數(shù)輸出除法器的局限性。如果我們想根據(jù)可用的晶體頻率調(diào)整 VCO 頻率,則反饋分頻器 M 存在類似的限制。

幸運(yùn)的是,分?jǐn)?shù)輸出分壓器技術(shù)近年來(lái)已經(jīng)發(fā)展到可以實(shí)現(xiàn)“任意”N1、N2、N3、N4 和 M 比率(在指定設(shè)計(jì)范圍內(nèi))。通過(guò)將 N1 和 N2 設(shè)置為:

這假設(shè) VCO 頻率為 2500 MHz。在這種特殊情況下,5P49V60 在 f1 上的誤差為 0 ppm,在 f2 上的誤差為 0.5 ppb。(0.5 ppb 遠(yuǎn)低于晶體諧振器的容差!)有時(shí),VCO 頻率可能會(huì)影響部件的性能。使用 IDT 的Timing Commander 軟件可以找到 VersaClock 6E 的最佳配置。IDT 的現(xiàn)場(chǎng)應(yīng)用工程師和應(yīng)用工程師團(tuán)隊(duì)幫助微調(diào)設(shè)備的配置以獲得最佳性能。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19811瀏覽量

233603 -

usb

+關(guān)注

關(guān)注

60文章

8146瀏覽量

270939 -

諧振器

+關(guān)注

關(guān)注

4文章

1146瀏覽量

66496

發(fā)布評(píng)論請(qǐng)先 登錄

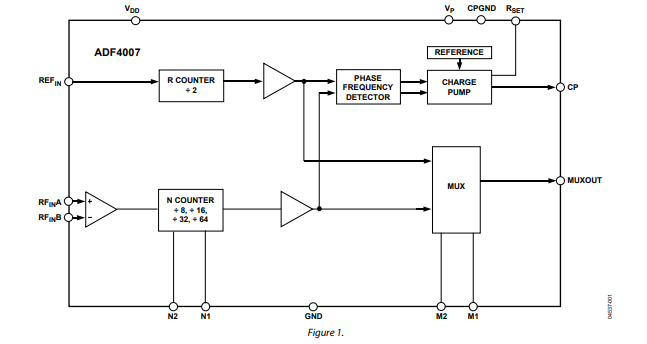

ADF4007高頻分頻器/PLL頻率合成器技術(shù)手冊(cè)

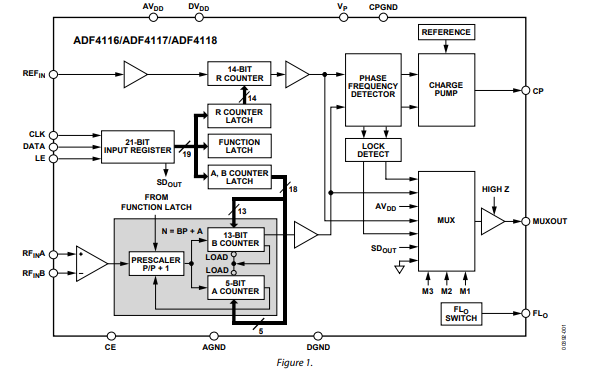

ADF4116/ADF4117/ADF4118單通道、整數(shù)N分頻550MHz PLL技術(shù)手冊(cè)

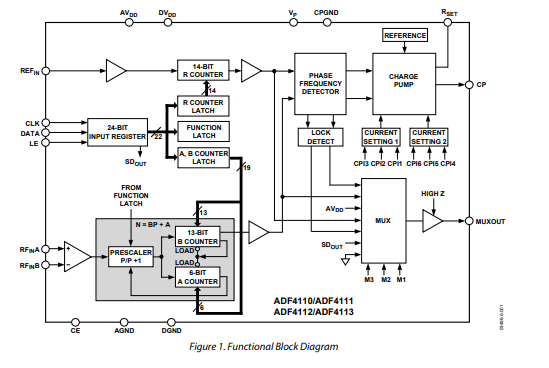

ADF4110/ADF4111/ADF4112/ADF4113單通道、整數(shù)N分頻、550 MHz PLL,內(nèi)置可編程預(yù)分頻器和電荷泵技術(shù)手冊(cè)

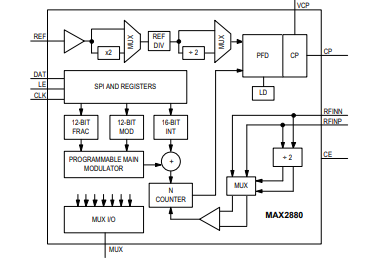

MAX2880 250MHz-12.4GHz、高性能、分?jǐn)?shù)/整數(shù)型N分頻PLL技術(shù)手冊(cè)

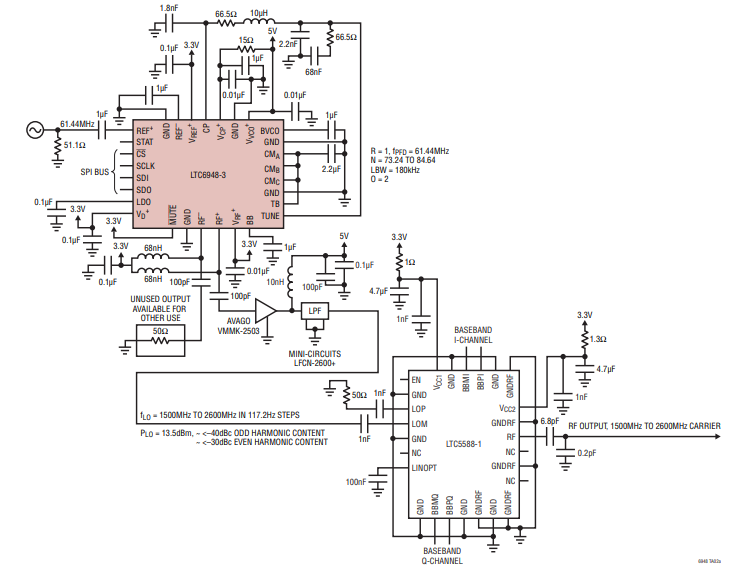

LTC6948具集成型VCO的超低噪聲0.37GHz至6.39GHz分?jǐn)?shù)N合成器技術(shù)手冊(cè)

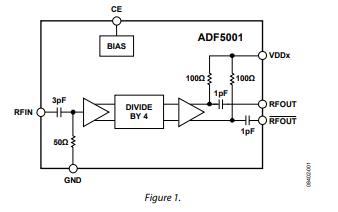

ADF5001 4GHz 至18GHz 4分頻預(yù)分頻器技術(shù)手冊(cè)

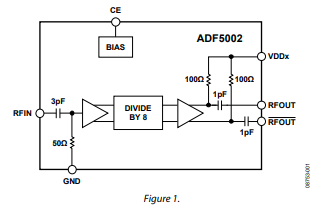

ADF5002 4GHz至18GHz 8分頻預(yù)分頻器技術(shù)手冊(cè)

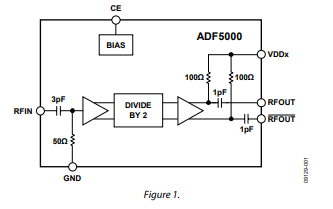

ADF5000 4GHz 至18GHz 2分頻預(yù)分頻器技術(shù)手冊(cè)

分頻器的定義和作用

CDC906可編程3-PLL時(shí)鐘合成器/乘法器/分頻器數(shù)據(jù)表

CDCE906 PLL頻率合成器/乘法器/分頻器數(shù)據(jù)表

CDCE706可編程3-PLL時(shí)鐘合成器/乘法器/分頻器數(shù)據(jù)表

什么是車載信息娛樂(lè)和集成駕駛艙? 汽車的未來(lái)及其實(shí)現(xiàn)的挑戰(zhàn)

分?jǐn)?shù)輸出分頻器PLL對(duì)信息娛樂(lè)和儀表板應(yīng)用的價(jià)值

分?jǐn)?shù)輸出分頻器PLL對(duì)信息娛樂(lè)和儀表板應(yīng)用的價(jià)值

評(píng)論