在開發(fā)FPGA綁定管腳時(shí),經(jīng)常會看到HP Bank、HR Bank和HD Bank,它們分別是什么意思?分別可以適用于哪些應(yīng)用個(gè)???

首先我們要明確一點(diǎn),這幾個(gè)概念都是在7系列之后才有的,其中7系列的FPGA中有HP Bank和HR Bank,UltraScale FPGA有HP Bank、HR Bank和HD Bank,但并不是一個(gè)FPGA中會同時(shí)包含HP/HR/HD Bank。

HP:High Performance

HR:High Range

HD:High Density

HP Bank,從名字就可以看出來,應(yīng)用于高性能也就是速度比較高的場景,比如DDR或者其它高速差分總線(不是gtx),由于速率比較高,Bank電壓最高也只能到1.8V。

HR Bank表示支持wider range of I/O standards,最高能夠支持到3.3V的電壓。

HD Bank應(yīng)用于低速I/O的場景,最高速率限制在250M以內(nèi),最高電壓也是支持到3.3V

Kintex UltraScale 和Virtex UltraScale中有HP Bank和HR Bank,Virtex UltraScale+系列中只有HP Bank,Zynq UltraScale+ MPSoC 和Kintex UltraScale+ 系列包含HP和HR Bank。

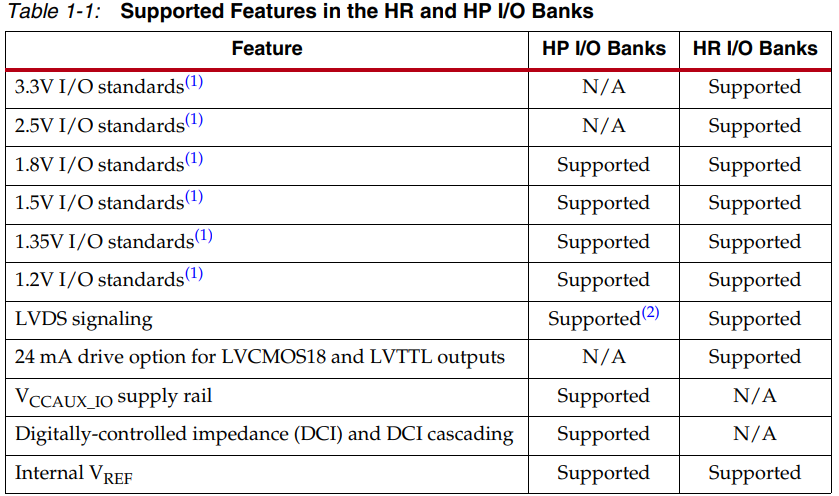

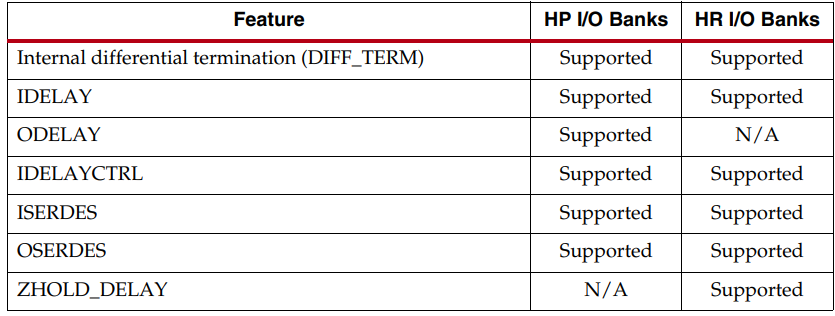

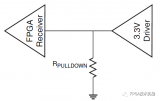

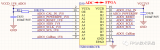

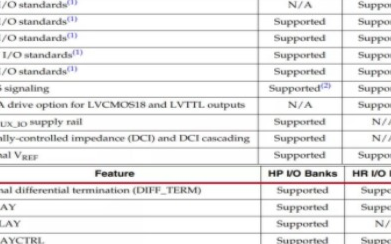

由于應(yīng)用場景不同,支持的IO原語也有差異,下圖是7系列FPGA HP Bank和HR Bank支持的特性:

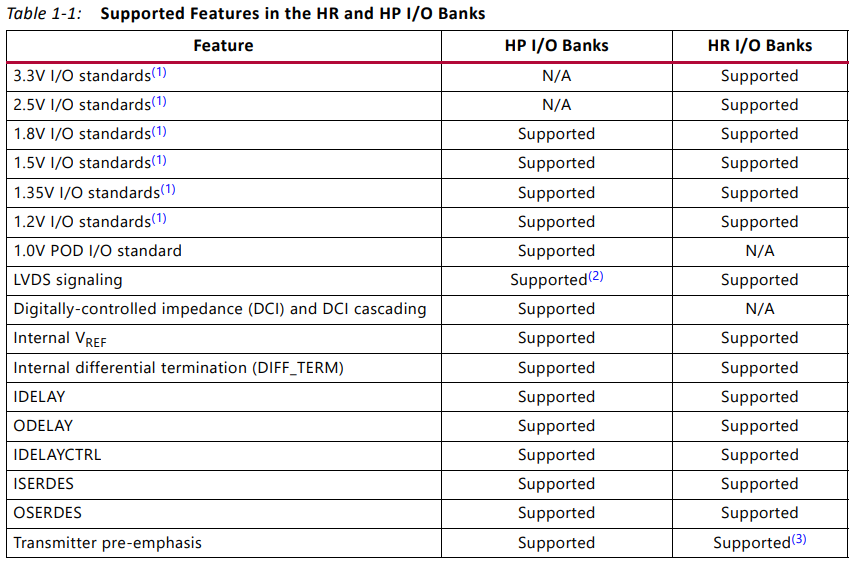

下圖是UltraScale系列FPGA HP Bank和HR Bank支持的特性:

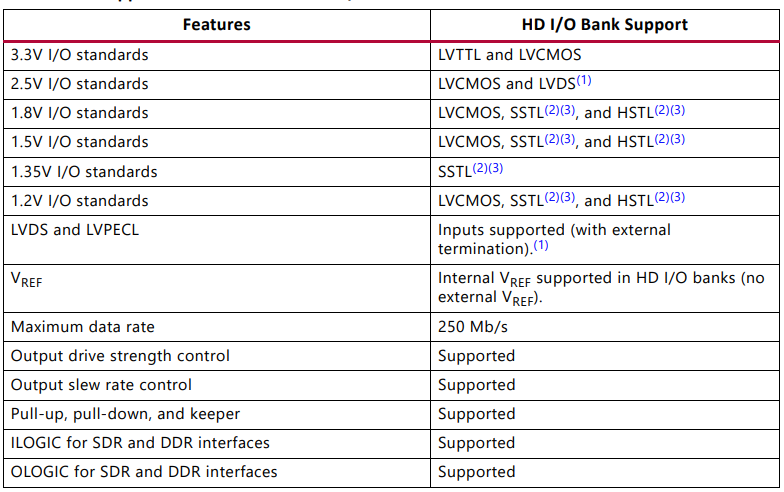

HD Bank由于相對特殊一些,單獨(dú)列了出來:

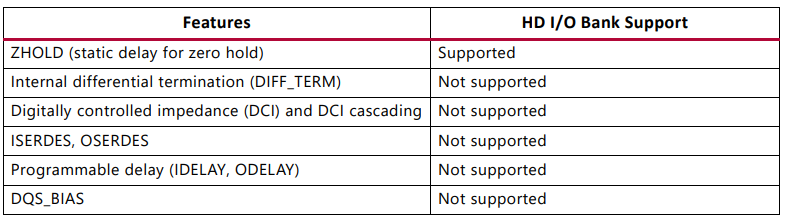

在UG575中也可以看到不同的FPGA中HR、HP和HD Bank的IO數(shù)量:

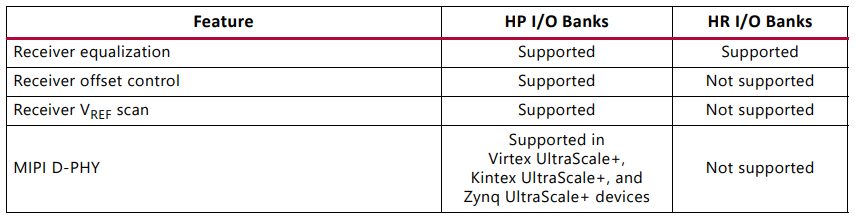

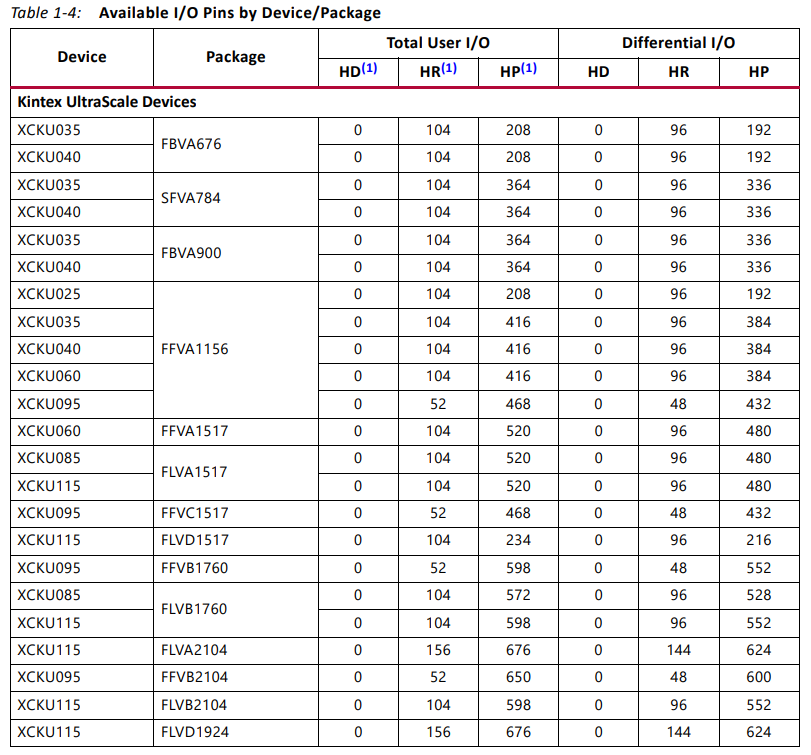

這里我們講到了7系列和UltraScale系列,就順便提一下UltraScale系列相對7系列的新的feature:

原文標(biāo)題:Xilinx FPGA中HP HR HD bank分別是什么用途

文章出處:【微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21956瀏覽量

614016 -

電壓

+關(guān)注

關(guān)注

45文章

5697瀏覽量

117270 -

bank

+關(guān)注

關(guān)注

0文章

16瀏覽量

15055

原文標(biāo)題:Xilinx FPGA中HP HR HD bank分別是什么用途

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

在HP Bank中如何連接PCI?

可以直接將時(shí)鐘緩沖器的輸出連接到HR庫嗎?

7系列FPGA HR bank IO如何與DDR3連接?

HR / HP bank中的7系列LVDS輸入延遲的解決辦法?

新手求助FPGA畫板bank電壓問題?

XAPP520將符合2.5V和3.3V I/O標(biāo)準(zhǔn)的7系列FPGA高性能I/O Bank進(jìn)行連接

DCI是什么?Xilinx 7系列FPGA的HP bank都支持DCI

如何解決FPGA引腳與LVDS信號相連時(shí)兼容性的問題

HR和HP banks基本介紹

Xilinx 7系列FPGA高性能接口與2.5V/3.3V外設(shè)IO接口設(shè)計(jì)

基于TXS0108實(shí)現(xiàn)FPGA IO Bank接不同外設(shè)IO接口電壓轉(zhuǎn)換

FPGA中HP/HR/HD Bank的應(yīng)用

FPGA中HP/HR/HD Bank的應(yīng)用

評論