從不成熟到成熟的推進(jìn)劑,但是

DCI肯定要為此付出一點(diǎn)代價(jià)!關(guān)于技術(shù)架構(gòu):

DCI早先采用一種分布式架構(gòu)。但是不知道為什么

DCI現(xiàn)在熱衷CWDM4技術(shù)。PSM4

支持數(shù)據(jù)的透明傳輸,透明傳輸?shù)暮锰幘褪敲恳宦?/div>

2017-02-08 15:53:31

本帖最后由 gk320830 于 2015-3-7 23:10 編輯

電子方面的新手,公司是做光伏逆變器的。最近領(lǐng)導(dǎo)說要我深入理解DCI和DCV保護(hù)電路,并寫出設(shè)計(jì)報(bào)告。感覺很有壓力。我需要重點(diǎn)學(xué)習(xí)哪方面的知識(shí)呢

2013-07-18 21:38:37

課程以實(shí)際項(xiàng)目為背景,詳細(xì)介紹XILINX 7系列FPGA硬件設(shè)計(jì),項(xiàng)目案例板卡標(biāo)準(zhǔn)呢PCIE卡,FPGA采用Xilinx的XC7A100T-2FGG676I系列FPGA,具有超微體積、低功耗的特點(diǎn)

2021-11-17 23:12:06

FPGA設(shè)計(jì)高級(jí)技巧Xilinx篇目錄414.3 減少關(guān)鍵路徑的邏輯級(jí)數(shù).............................................404.2IF語句和Case語句速度

2012-08-11 11:43:17

Xilinx 7系列FPGA簡介--選型參考

2021-02-01 06:10:55

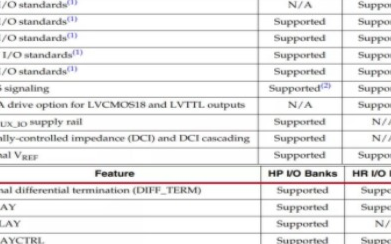

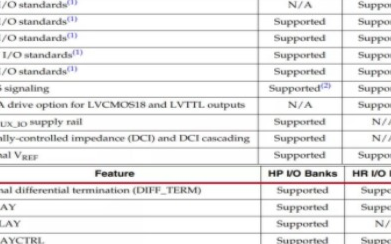

,支持最大1.8V的I/O信號(hào),HR主要為了支持更廣泛的I/O標(biāo)準(zhǔn),支持最大3.3V的I/O信號(hào)。 Xilinx 7系列FPGA的HR和HP bank,每個(gè)bank有50個(gè)I/O管腳,每個(gè)I/O管腳

2020-12-23 17:17:47

引言: 我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開發(fā)人員提供使用。通過本文,可以了解到

2021-05-28 09:23:25

引言: 我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開發(fā)人員提供使用。通過本文,可以了解到

2021-07-08 08:00:00

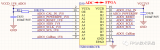

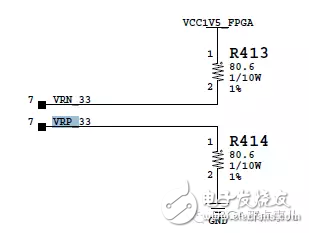

各位大神,請(qǐng)問Xilinx FPGA中的DCI是如何使用的?我知道是把每個(gè)Bank的VRP、VRN管腳分別下拉、上拉,除此之外,在HDL代碼和約束中應(yīng)該如何寫呢?查了半天資料沒有查到,所以來論壇問問。@LQVSHQ

2017-08-20 20:51:57

注意的是,CCLK的周期有-30%~+45%的偏差。ISE不同版本、不同FPGA系列,它默認(rèn)的配置時(shí)鐘是不一樣的。此外,還需要注意選擇的CCLK頻率能被PROM支持。我曾經(jīng)遇到過這個(gè)問題:用Virtex5

2015-09-22 23:36:50

,我們的問題就是,過了一段時(shí)間,DCI匹配完畢了,但是CCLK卻沒有 了,因此FPGA一直處在Start UP的前2個(gè)Phase上,不會(huì)到DONE。導(dǎo)致無法配置成功。看xilinx

2015-08-20 22:57:10

,過了一段時(shí)間,DCI匹配完畢了,但是CCLK卻沒有 了,因此FPGA一直處在StartUP的前2個(gè)Phase上,不會(huì)到DONE。導(dǎo)致無法配置成功。看xilinx DevelopmentSystem

2016-05-22 23:38:23

xilinx公司的7系列FPGA應(yīng)用指南

2012-08-14 12:17:40

xilinx的FPGA,BANK引腳VREF,VRN,VRP都是什么意思?如何使用,DATASHEET沒看明白,謝謝請(qǐng)幫忙解答謝謝!

補(bǔ)充一下:Virtex II Pro,XC2VP4,謝謝

2023-11-28 07:19:03

HI,我的FPGA是Kintex-7的XC7K410T-2FFG900。我的DDR3是2Gb,由128Mb * 16組成。 DDR3數(shù)據(jù)速率為1600Mbps,因此我必須在HP BANK中使用VRN

2020-07-21 14:47:06

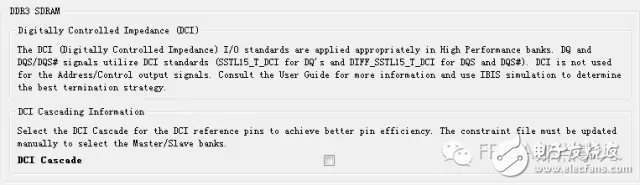

SSTL15_T_DCI嗎?謝謝!以上來自于谷歌翻譯以下為原文Hello, I use HP banks of Virtex7 to implement DDR3 controller.My controller

2019-03-25 11:04:50

親愛的團(tuán)隊(duì),我們正在為ZCU102 EVM板設(shè)計(jì)基于攝像頭的設(shè)計(jì)。 J4 FMC連接器信號(hào)用于連接攝像機(jī)板的MIPI CSI-2和I2C信號(hào)。由于我們正在連接MIPI CSI-2,我們正在將bank

2019-10-16 08:54:55

IDT2305-1DCI - 3.3V ZERO DELAY CLOCK BUFFER - Integrated Device Technology

2022-11-04 17:22:44

IDT2308-1DCI - 3.3V ZERO DELAY CLOCK MULTIPLIER - Integrated Device Technology

2022-11-04 17:22:44

IDT2308A-1DCI - 3.3V ZERO DELAY CLOCK MULTIPLIER - Integrated Device Technology

2022-11-04 17:22:44

IDT2308A-2DCI - 3.3V ZERO DELAY CLOCK MULTIPLIER - Integrated Device Technology

2022-11-04 17:22:44

IDT5V551DCI - 1:4 CLOCK BUFFER - Integrated Device Technology

2022-11-04 17:22:44

TUSB1046-DCI USB Type-C? DisplayPort? ALT Mode 10 Gbps Linear Redriver Crosspoin datasheet (Rev. C)

2022-11-04 17:22:44

TUSB1046A-DCI USB Type-C? DP ALT Mode 10 Gbps Linear Redriver Crosspoint Switch datasheet (Rev. A)

2022-11-04 17:22:44

TUSB546-DCI USB Type-C? DP ALT Mode Linear Redriver Crosspoint Switch datasheet (Rev. C)

2022-11-04 17:22:44

TUSB546A-DCI USB Type-C? DP ALT Mode 8.1 Gbps Linear Redriver Crosspoint Switch datasheet (Rev. A)

2022-11-04 17:22:44

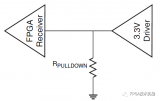

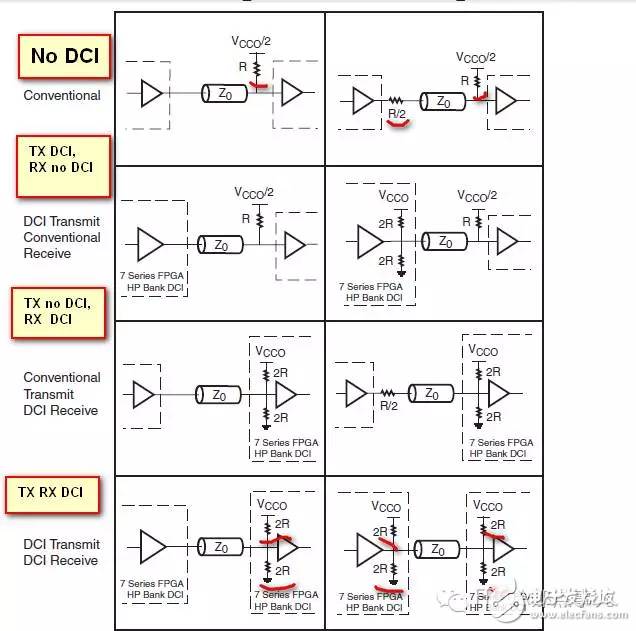

Xilinx FPGA提供了DCI(Digitally Controlled Impedance)技術(shù),包括兩個(gè)功能:(1).控制驅(qū)動(dòng)器的輸出阻抗;(2).為驅(qū)動(dòng)器或發(fā)送器添加一個(gè)并行端接,在傳輸線上得到精確的特征阻抗匹配,以提高信號(hào)完整性。

2019-05-27 07:22:12

能夠符合Xilinx最新的工具軟件和器件系列,因此選擇7系列FPGA作為原型平臺(tái)。經(jīng)朋友推薦,本開發(fā)板復(fù)雜度適中,學(xué)習(xí)開發(fā),因此特申請(qǐng)使用該開發(fā)板進(jìn)行學(xué)習(xí)開發(fā)相應(yīng)的資料教程。本人擬從以下幾個(gè)方面展開試用

2016-10-11 18:15:20

發(fā)燒友你們好,菜鳥想問問,在FPGA里面的bank,分為HR bank和HP bank,分別有什么區(qū)別啊?比如說,電平標(biāo)準(zhǔn)都有些什么限制?怎么配置IO standard?**************************************************************************** 菜鳥真是什么都不懂,望牛人可以解答,萬分感謝!!!!!!!

2014-09-04 10:13:49

我使用Hyperlynx 8.0進(jìn)行了模擬,如下所示: 將FPGA和DRAM芯片的DQ連接到54.5歐姆傳輸線,IBIS模型從Xilinx和Micron網(wǎng)站下載。 DRAM芯片可支持DDR-1066

2020-06-08 07:42:56

在ml_605的示意圖中,我發(fā)現(xiàn)在一個(gè)銀行(例如銀行16)中混合了LVDS信號(hào)和信號(hào)端信號(hào),所以銀行應(yīng)該收起2.5v,并且銀行有DCI匹配。但是在銀行24(銀行混合了LVDS信號(hào)和信號(hào)端信號(hào)),所以

2019-10-25 08:47:06

最近配置AD9139的時(shí)候,分別采用了兩種方式。一種是直接使用KC705板上晶振作為參考時(shí)鐘生成DCI和data,DAC單獨(dú)供參考時(shí)鐘,另一種是使用AD9139評(píng)估板分頻得到的DCO作為FPGA

2023-12-04 06:53:34

嗎?我明白LVTTL或LVCMOS輸入緩沖器不支持輸入DCI終止,但可能存在執(zhí)行此類技巧的任何方式?先謝謝你,

2020-05-28 06:16:57

嗨,我正在嘗試使用Hyperlynx來模擬K7上的DDR3L設(shè)計(jì)。我使用Vivado write_ibis根據(jù)我的FPGA設(shè)計(jì)生成ibis文件。對(duì)于SSTL135_DCI_HP_IN50_I信號(hào),我

2020-07-14 09:10:15

你好 我正在使用kintex 7系列FPGA我從xilinx獲得了通用的IBIS文件并將其轉(zhuǎn)換為適合我的應(yīng)用程序的特定文件(i:e)將引腳名稱和差分引腳更改為我的包中的引腳。如何找到模型針?例如

2020-07-23 07:41:46

我們用XC6VLX130T-1FF1156開發(fā)了一塊FPGA板。我們?cè)?b class="flag-6" style="color: red">BANK 12/22/23/32上安裝了帶有FPGA的DDR3 SODIMM。當(dāng)我調(diào)試DDR3 SODIMM時(shí),我發(fā)現(xiàn)我們錯(cuò)過

2020-06-15 16:36:57

/ O以進(jìn)行DCI級(jí)聯(lián)?現(xiàn)在我感興趣的部分是XC5VLX30,但后來我也需要FF676封裝中可用的較大部件的相同信息。我想最終得到一個(gè)可以與XC5VLX30到XC5VLX110全系列產(chǎn)品配合使用的電路板設(shè)計(jì)。 - Gabor

2020-06-02 14:05:43

你好我需要將LVDS輸出驅(qū)動(dòng)器連接到ZYNQ 7030的HP Bank。LVDS輸出驅(qū)動(dòng)器的電源電壓為VCCO_LVDSout_DRIVER = 2.5V,HP bank為VCCO_HP_BANK

2020-08-12 09:34:33

HI,我正在研究NetFPGA(XC7K325TFFG676)。我正在使用三模式以太網(wǎng)MAC和MIG(QDR控制器)IP內(nèi)核。在實(shí)現(xiàn)時(shí),我收到以下錯(cuò)誤:[放置30-110]以下IOB使用數(shù)字控制阻抗

2020-08-06 07:01:15

嗨!是否有可能不為7系列FPGA上的HP / HR庫供電? GTX怎么樣?

2020-03-18 07:46:17

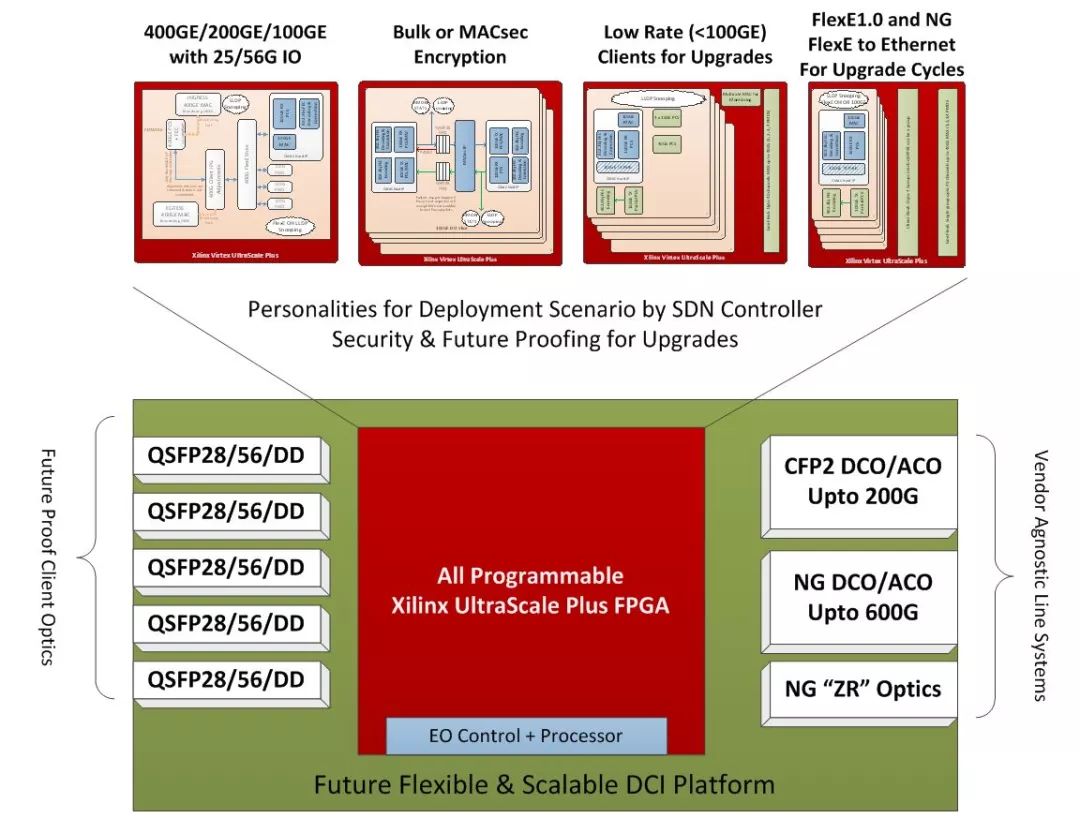

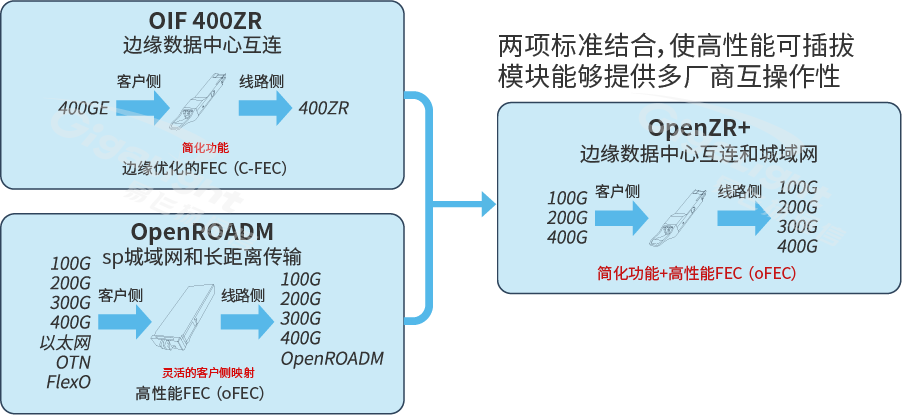

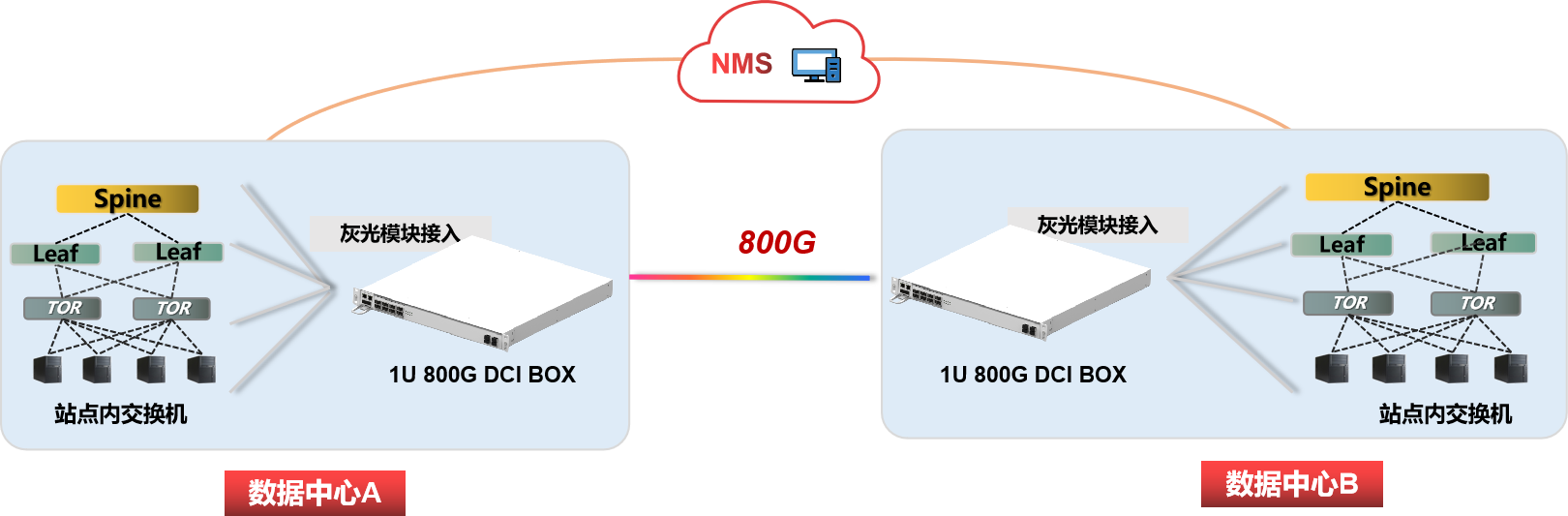

:系統(tǒng)支持10G/25G/40G/100G混合接入,按照25G信號(hào)要求進(jìn)行色散使用,能夠滿足其它速率信號(hào)傳輸要求。 對(duì)于超長距離的DCI,最有效的傳輸技術(shù)是相干光傳輸。通過建立快速、可靠的連接,物理上獨(dú)立

2021-07-26 16:37:31

port map(O => dci_p, OB => dci_n, I => clk);仿真結(jié)果:可以看出dci_p和dci_n之間的相位關(guān)系不對(duì)。請(qǐng)問有沒有人知道這是為什么??

2017-03-07 11:25:55

DDR3模塊存在于K705中。 ddr3模塊的地址和控制引腳使用sstl15標(biāo)準(zhǔn)連接到HP bank。根據(jù)圖1-57(第78頁)的7系列FPGA selectIO資源用戶指南,FPGA和DDR3端

2019-10-23 09:53:33

你好,我有一個(gè)來自SY58040的差分CML時(shí)鐘信號(hào),我需要將它連接到Kintex-7 HP bank。由于HP銀行已連接到DDR3內(nèi)存,因此該銀行的VCCO為1.5V。是否可以使用(外部)交流耦合

2020-07-21 15:40:55

晚上好,xilinx平臺(tái)有線u***和xilinx平臺(tái)有線電纜u*** ii是否支持FPGA Kintex系列?問候Vimala

2019-09-23 10:00:38

賽靈思(XILINX)全新7系列FPGA詳述

2012-08-14 12:20:22

XAPP520將符合2.5V和3.3V I/O標(biāo)準(zhǔn)的7系列FPGA高性能I/O Bank進(jìn)行連接 The I/Os in Xilinx 7 series FPGAs are classified

2012-01-26 18:47:15 75

75 本文是關(guān)于 xilinx公司的7系列FPGA應(yīng)用指南。xilinx公司的7系列FPGA包括3個(gè)子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對(duì)這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對(duì)比表

2012-08-07 17:22:55 201

201 Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發(fā)環(huán)境

2016-01-18 15:30:32 45

45 GD32-Colibri-F207實(shí)驗(yàn)板DCI_TLDI_320240,很好的GD32資料,快來學(xué)習(xí)吧。

2016-04-21 10:49:49 9

9 單片機(jī)GD32F207學(xué)習(xí)例程之GD32F207-DCI例程源碼

2016-06-03 15:40:34 10

10 DCI技術(shù)概述 隨著FPGA芯片越大而且系統(tǒng)時(shí)鐘越高,PCB板設(shè)計(jì)以及結(jié)構(gòu)設(shè)計(jì)變得越難,隨著速率的提高,板間的信號(hào)完整性變的非常關(guān)鍵,PCB板上若有關(guān)鍵信號(hào),那么需要進(jìn)行阻抗匹配,從而避免信號(hào)的反射

2017-11-18 11:04:01 4351

4351

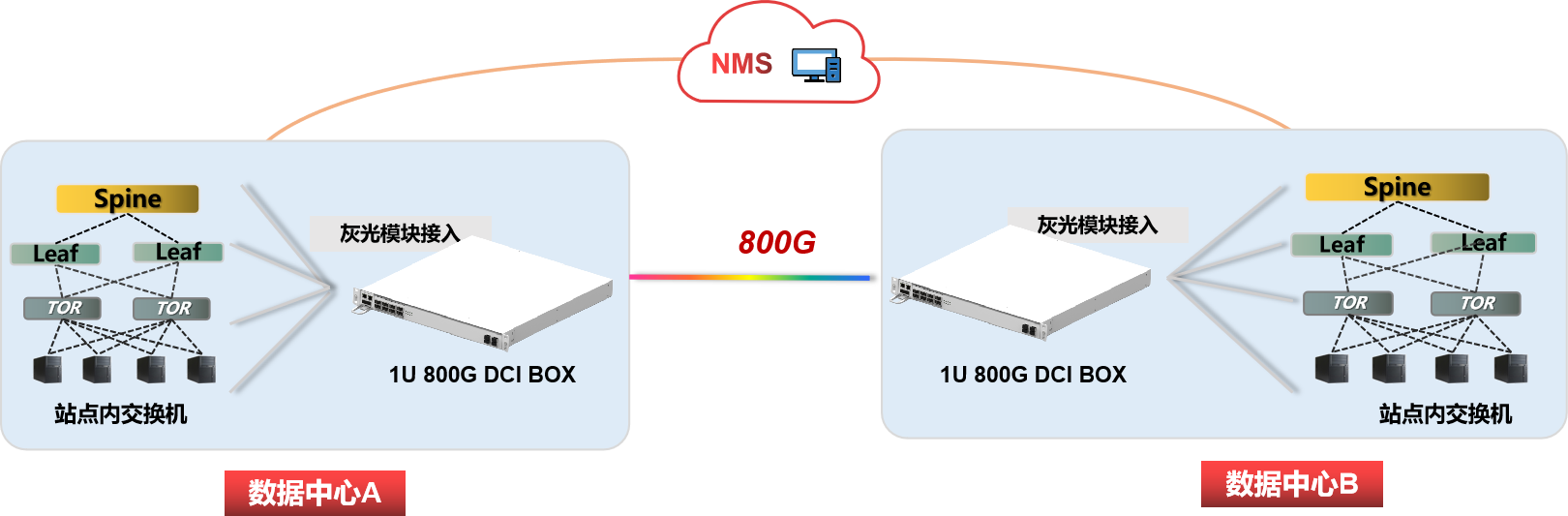

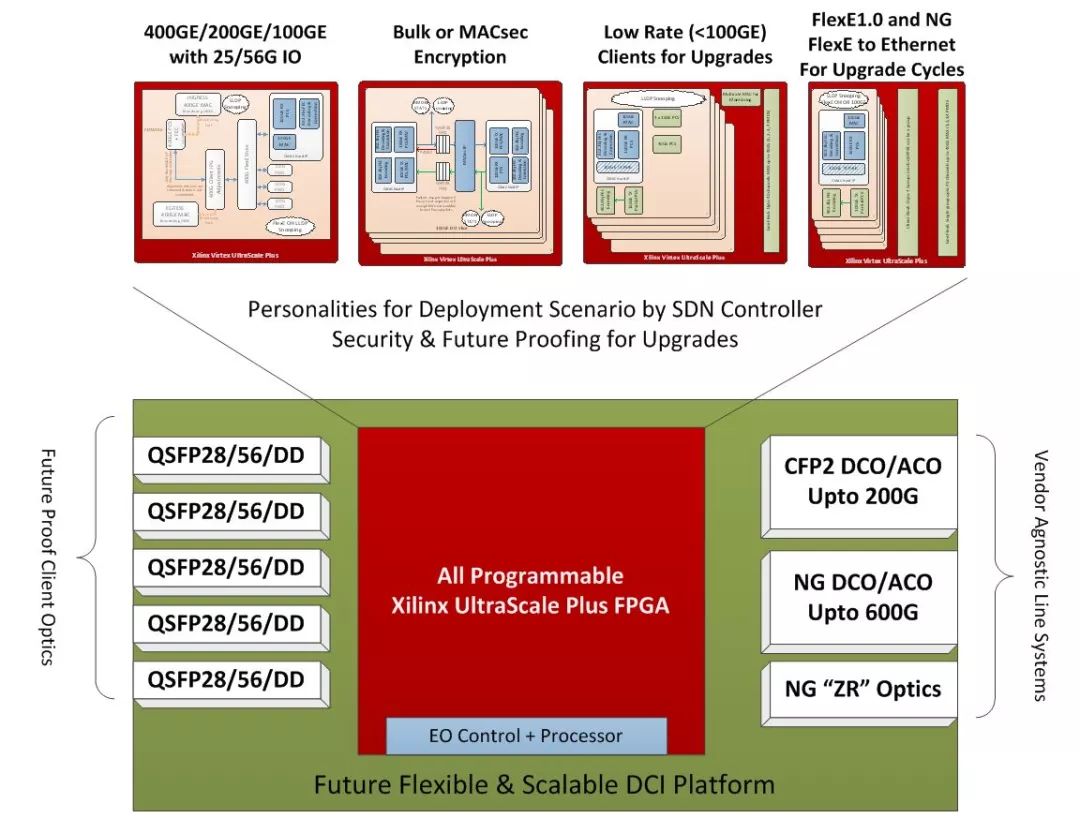

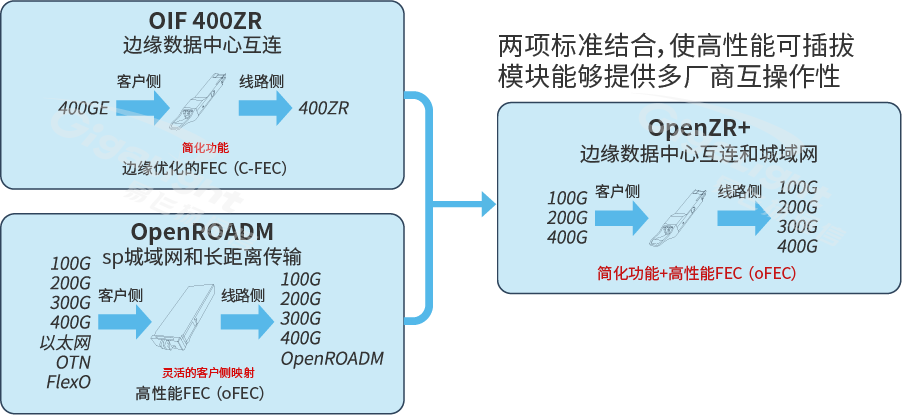

為支持數(shù)據(jù)中心間的通信,需要使用非常大的數(shù)據(jù)管道,同時(shí),用于在這些管道間傳輸數(shù)據(jù)的網(wǎng)絡(luò)通常稱為數(shù)據(jù)中心互連 (DCI)。

2018-02-03 11:37:38 11431

11431

本文主要介紹了dsPIC30F系列參考手冊(cè)之?dāng)?shù)據(jù)轉(zhuǎn)換器接口(DCI)。

2018-06-24 03:20:00 20

20 。Xilinx公司提供DCI可以在芯片內(nèi)部進(jìn)行阻抗匹配,匹配電阻更加接進(jìn)芯片,可以減少元器件,節(jié)省PDB板面積,并且也更方便走線。

2018-11-23 09:05:00 5183

5183

電子發(fā)燒友網(wǎng)為你提供TI(ti)TUSB546-DCI相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TUSB546-DCI的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TUSB546-DCI真值表,TUSB546-DCI管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:19:15

電子發(fā)燒友網(wǎng)為你提供TI(ti)TUSB546A-DCI相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TUSB546A-DCI的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TUSB546A-DCI真值表,TUSB546A-DCI管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

在西班牙巴塞羅那舉行的2019世界移動(dòng)大會(huì)(MWC2019)期間,華為發(fā)布了下一代DCI傳輸解決方案,以單波600G、OXC全光交換、NCE (Network Cloud Engine 網(wǎng)絡(luò)云化引擎) 三大技術(shù)構(gòu)建超寬、極簡、智慧的DCI網(wǎng)絡(luò)。

2019-03-01 10:01:28 3567

3567 DCI體系面向互聯(lián)網(wǎng)內(nèi)容平臺(tái)提供“嵌入式”服務(wù),發(fā)揮其對(duì)互聯(lián)網(wǎng)版權(quán)確權(quán)、授權(quán)和維權(quán)等核心環(huán)節(jié)的基礎(chǔ)性公共服務(wù)功能,解決困擾版權(quán)產(chǎn)業(yè)發(fā)展過程中因權(quán)屬證明和信用缺失所造成的一系列難題,為內(nèi)容產(chǎn)業(yè)提供

2019-03-29 11:18:10 719

719 中興通訊光傳送產(chǎn)品總經(jīng)理王泰立表示:“中興通訊這款專為DCI研發(fā)的新一代盒式600G OTN設(shè)備,能滿足當(dāng)下蓬勃發(fā)展的DC間的超高帶寬需求。中興通訊將繼續(xù)攜手合作伙伴,持續(xù)構(gòu)建一個(gè)超寬無阻、靈活智能的DCI網(wǎng)絡(luò),引領(lǐng)DCI進(jìn)入高速全光互聯(lián)時(shí)代。”

2019-05-22 10:22:25 2013

2013 =因此,從成本角度來看,每三年更換這些設(shè)備并不劃算。該功能有助于數(shù)據(jù)中心運(yùn)營商將 DCI 互連盒脫離升級(jí)周期。

2019-07-29 08:58:50 4149

4149

有關(guān)榮耀 X10 系列兩款新機(jī)榮耀 X10 Pro/Max 的消息逐漸增多,今日博主 @長安數(shù)碼君 爆料稱榮耀將推出的一款 7 英寸大屏 5G 手機(jī)將采用定制屏幕,支持 DCI-P3 廣色域。

2020-06-15 16:26:52 2823

2823 諾基亞今日宣布與中國互聯(lián)網(wǎng)巨頭騰訊和百度簽訂了兩份數(shù)據(jù)中心互聯(lián) (DCI) 網(wǎng)絡(luò)解決方案合同。騰訊和百度將進(jìn)一步強(qiáng)化與諾基亞的緊密合作伙伴關(guān)系,共同構(gòu)建軟件定義的DCI基礎(chǔ)設(shè)施。這將能夠?yàn)轵v訊和百度提供所需的動(dòng)態(tài)、大規(guī)模光網(wǎng)絡(luò),有效支持他們不斷增長的云運(yùn)營。

2020-06-17 16:56:24 2601

2601 Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個(gè)工藝級(jí)別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點(diǎn) 4.7系列

2020-11-13 18:03:30 14065

14065 LVDS-33,LVDS-25)信號(hào)相連時(shí)兼容性的問題,該專題就解決一下這類問題。 這里補(bǔ)充一點(diǎn)知識(shí),Xilinx的FPGA從7系開始分HR IO Bank和HP IO Bank,其中HR(High

2021-08-19 10:08:00 7755

7755

數(shù)字?jǐn)z像頭接口是一個(gè)同步并行接口,可以從數(shù)字?jǐn)z像頭捕獲視頻和圖像信息。它支持不同的顏色空間圖像,例如YUV/RGB,另外支持壓縮數(shù)據(jù)的JPEG格式圖像。1 IO初始化DCI一般選擇8bit接口,另外OV2640需要I2C接口設(shè)置寄存器。2 初始化DCI...

2021-12-05 15:51:03 12

12 在開發(fā)FPGA綁定管腳時(shí),經(jīng)常會(huì)看到HP Bank、HR Bank和HD Bank,它們分別是什么意思?分別可以適用于哪些應(yīng)用個(gè)???

2022-02-26 16:54:38 3992

3992

在開發(fā)FPGA綁定管腳時(shí),經(jīng)常會(huì)看到HP Bank、HR Bank和HD Bank,它們分別是什么意思?分別可以適用于哪些應(yīng)用個(gè)???

2022-04-07 11:57:27 7129

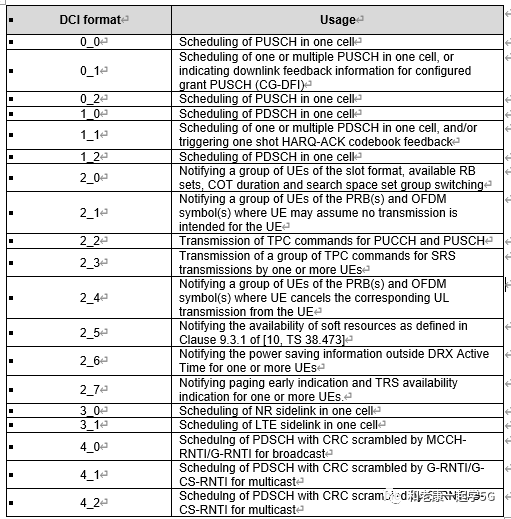

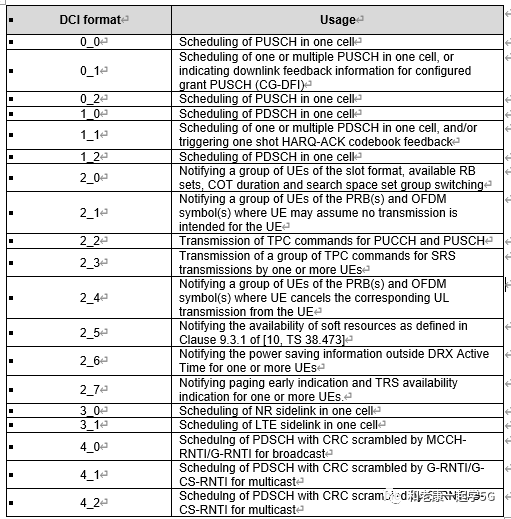

7129 DCI Format格式定義是從字段映射到具體的信息位,其中每個(gè)字段都按照它在描述中出現(xiàn)的順序進(jìn)行映射包括零填充位(如果有)

2022-11-12 16:16:54 3129

3129

但為什么會(huì)出現(xiàn)這個(gè)東西?在我看來,主要是場景和成本兩方面決定。場景上,DCI-BOX說高大上一點(diǎn)是面向新一代城域網(wǎng)的架構(gòu),如城域分發(fā)(POD),云網(wǎng)入網(wǎng)點(diǎn)(POP)等功能區(qū)的應(yīng)用場景。

2022-11-18 09:35:21 8786

8786 DCI-BOX,中國聯(lián)通叫模塊化波分設(shè)備,中國電信叫盒式波分設(shè)備DCI-BOX,是數(shù)據(jù)中心點(diǎn)到點(diǎn)互連(DCI)的設(shè)備。在DCI BOX出現(xiàn)之前,DCI通常使用WDM/OTN設(shè)備進(jìn)行互連,那么兩者之間

2023-03-26 14:29:09 1104

1104 在DCI BOX出現(xiàn)之前,DCI通常使用WDM/OTN設(shè)備進(jìn)行互連,那么兩者之間有什么區(qū)別呢?

2023-03-27 15:37:02 634

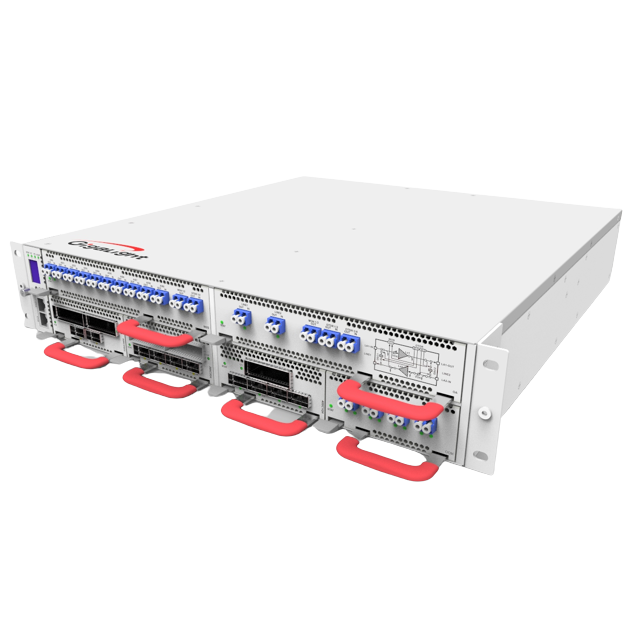

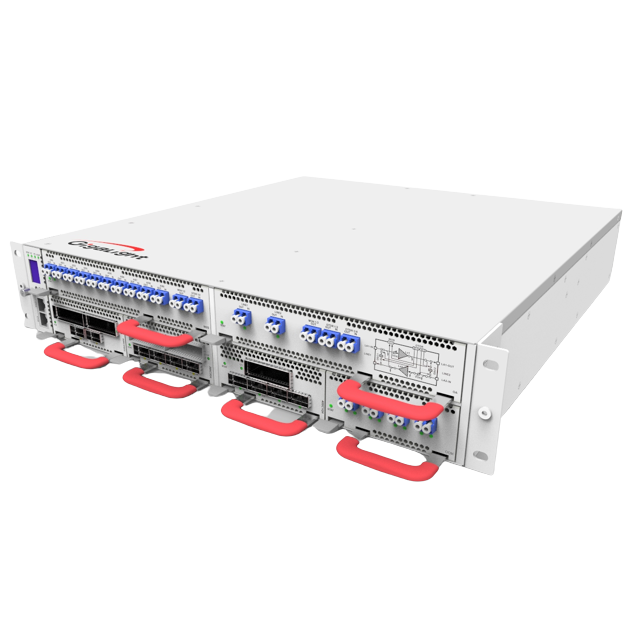

634 易飛揚(yáng)2U 6.4T DCI BOX

2023-04-14 17:46:39 753

753

易飛揚(yáng)推出的最新1U 800G DWDM DCI BOX是一款1U盒式的多業(yè)務(wù)波分傳輸平臺(tái),可滿足最大8×100GE業(yè)務(wù)點(diǎn)對(duì)點(diǎn)傳輸?shù)膽?yīng)用場景,單機(jī)框常規(guī)接入容量800G。它同樣滿足DCI對(duì)小體積、低功耗、極簡維護(hù)、低時(shí)延、大帶寬的需求。

2023-04-21 10:39:33 244

244 易飛揚(yáng)推出的最新1U 800G DWDM DCI BOX是一款1U盒式的多業(yè)務(wù)波分傳輸平臺(tái),可滿足最大8×100GE業(yè)務(wù)點(diǎn)對(duì)點(diǎn)傳輸?shù)膽?yīng)用場景,單機(jī)框常規(guī)接入容量800G。它同樣滿足DCI對(duì)小體積、低功耗、極簡維護(hù)、低時(shí)延、大帶寬的需求。

2023-04-21 10:40:18 635

635 上文,我們介紹了相干DCI BOX完美適配目前DCI傳輸?shù)膽?yīng)用,不過,相干子系統(tǒng)的成本向來比較高,那是否有成本較低的非相干設(shè)備可供選擇?考慮到不同用戶的預(yù)算需求,易飛揚(yáng)同樣提供經(jīng)濟(jì)型的非相干DCI BOX,本文介紹的1U 800G DWDM DCI BOX便是其中一款。

2023-04-24 09:46:24 463

463

易飛揚(yáng)緊湊型的DCI BOX相干傳輸子系統(tǒng)是為數(shù)據(jù)中心互連、城域網(wǎng)波分應(yīng)用所定制的業(yè)務(wù)平臺(tái)。完整方案包含相干光模塊,OTU業(yè)務(wù)板卡,多款業(yè)務(wù)板卡(可選),以及DCI BOX機(jī)框設(shè)備,可輕松滿足DCI需求。

2023-05-12 16:24:13 741

741

Xilinx 7系列FPGA IO Bank分為HP Bank和HR Bank,HP IO接口電壓范圍為1.2V~1.8V,可以實(shí)現(xiàn)高性能,HR IO接口電壓范圍為1.2V~3.3V。

2023-05-15 09:27:58 2119

2119

引言:上一篇文章我們介紹了通過添加電阻器、場效應(yīng)晶體管(FET)開關(guān)、電平轉(zhuǎn)換器甚至其他Xilinx FPGA等選項(xiàng)實(shí)現(xiàn)HP Bank IO與2.5V/3.3V外設(shè)對(duì)接的方法。本文介紹利用TI公司TXS0108實(shí)現(xiàn)FPGA IO Bank接不同外設(shè)IO接口電壓轉(zhuǎn)換。

2023-05-16 09:02:50 2100

2100

隨著國內(nèi)電影市場蓬勃發(fā)展,《“十四五”中國電影發(fā)展規(guī)劃》聚焦電影強(qiáng)國建設(shè),對(duì)電影科技研發(fā)、創(chuàng)新提出了明確要求。在影院顯示領(lǐng)域,DCI認(rèn)證就是橫跨在國產(chǎn)放映系統(tǒng)高質(zhì)量發(fā)展路上的難關(guān)。 ? 2023

2023-05-31 09:32:30 1059

1059 據(jù)高工LED觀察,利亞德在LED電影屏領(lǐng)域布局良久。早在2018年,以共同開拓全球電影院LED顯示市場為初衷,LG電子與利亞德強(qiáng)強(qiáng)聯(lián)合開發(fā)了14m-P3.3mm-4K(面積101m2)DCI電影屏,并于2019年11月通過了數(shù)字影院倡導(dǎo)聯(lián)盟(DCI)的認(rèn)證。

2023-09-07 16:43:26 487

487 電子發(fā)燒友網(wǎng)站提供《鉛框架 - DCI Ag 板塊 RoHS/鹵化物測試報(bào)告.pdf》資料免費(fèi)下載

2024-02-23 09:55:28 1

1 Xilinx FPGA芯片擁有多個(gè)系列和型號(hào),以滿足不同應(yīng)用領(lǐng)域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點(diǎn)。

2024-03-14 16:24:41 215

215

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論