實驗目的:

為了更方便的對DDR讀寫,我們對DDR再次封裝成可復用的讀寫模塊。

一、前言

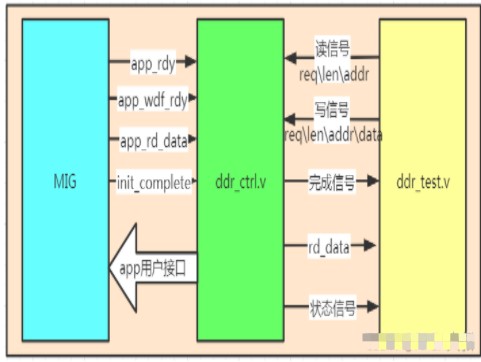

因為DDR3是半雙工,所以DDR讀寫模塊應該包括三部分內容:

ddr3_top.v :

1. ddr3讀操作子模塊

2. ddr3寫操作子模塊

3. ddr3讀/寫仲裁模塊

但是在實際項目使用時,DDR都要根據實際需求來進行讀寫操作,所以本文旨在提供一種思路,將讀/寫/仲裁合在一個模塊,實際使用當結合具體情況而定。

實現目標: 給出(寫請求、寫長度、寫數據、寫地址)就寫入ddr3,給出(讀請求、讀長度、讀地址)就從ddr3讀相應數量的數據出來。

二、方案設計

2.1 系統框圖

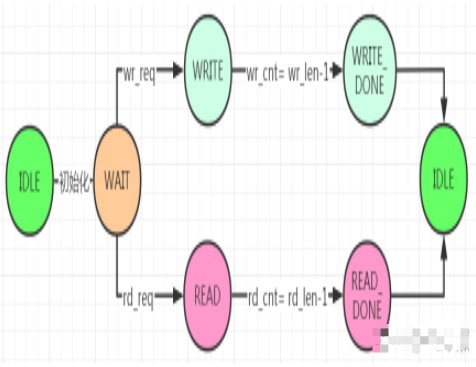

2.2設計狀態機

2.3代碼實現

代碼都是浮云~

記得帶我入門的老師傅說過:只寫代碼,那是碼農干的~

重點是方案,是思路~

2.4仿真驗證

寫入200個數,1-200;

讀出100個數,1-100;

驗證成功。

三、其他

本章寫的比較簡略,主要參考黑金教程而來。實際使用正如文章開始所說,視具體情況而定。

1. ddr讀寫大都以FIFO作銜接,方便操作;

2. 讀寫操作按照時序圖操作就ok,主要設計讀寫仲裁方案。

3.1后記

本章確實寫的比較簡陋,原因一是使用情況具體分析;二是時間耽擱太久了,還有很多東西需要學習;先把DDR放一放,后面有更深的理解的時候再來補充。

DDR3系列算是筆者第一個完整的系列文章,整理的同時順便加深自己理解,有點愛上寫博客了~

終于結束這個篇章了,這周末開始GTX接口系列文章的整理!

審核編輯:湯梓紅

-

FPGA

+關注

關注

1645文章

22036瀏覽量

618080 -

封裝

+關注

關注

128文章

8655瀏覽量

145413 -

Xilinx

+關注

關注

73文章

2184瀏覽量

125251

發布評論請先 登錄

【RK3568+PG2L50H開發板實驗例程】FPGA部分 | DDR3 讀寫實驗例程

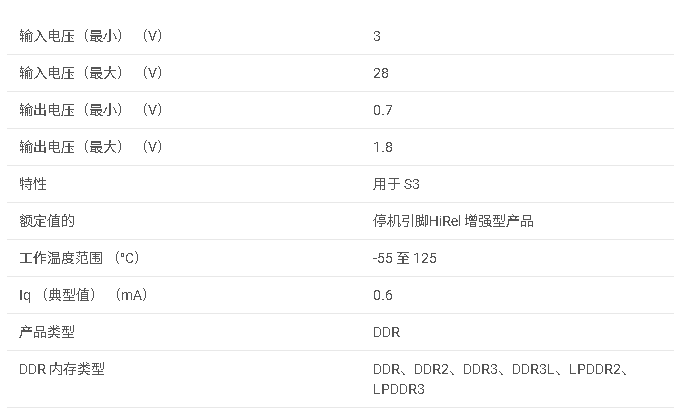

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據手冊

TPS51216-EP 增強型產品 完整的 DDR2、DDR3 和 DDR3L 內存電源解決方案 同步降壓控制器數據手冊

DDR3 SDRAM配置教程

燦芯半導體推出DDR3/4和LPDDR3/4 Combo IP

三大內存原廠或將于2025年停產DDR3/DDR4

基于Xilinx ZYNQ7000 FPGA嵌入式開發實戰指南

DDR3、DDR4、DDR5的性能對比

如何選擇DDR內存條 DDR3與DDR4內存區別

【米爾-Xilinx XC7A100T FPGA開發板試用】+01.開箱(zmj)

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx FPGA平臺DDR3設計保姆式教程(六)

Xilinx FPGA平臺DDR3設計保姆式教程(六)

評論