1、介紹

隨著電子行業技術的發展,特別是在傳輸接口的發展上,IEEE1284被 USB 接口取代,PATA被 SATA 取代,PCI被 PCI-Express 所取代,無一不證明了傳統并行接口的速度已經達到一個瓶頸了,取而代之的是速度更快的串行接口,于是原本用于光纖通信的SerDes 技術成為了為高速串行接口的主流。串行接口主要應用了差分信號傳輸技術,具有功耗低、抗干擾強,速度快的特點,理論上串行接口的最高傳輸速率可達到10Gbps 以上。

2、理論

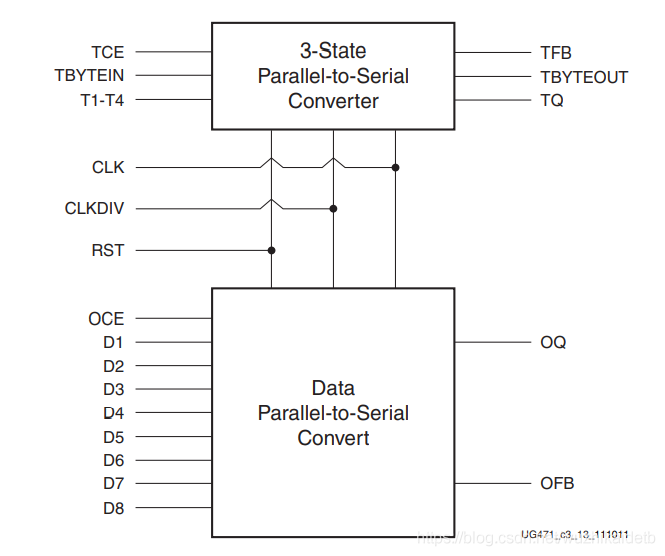

Xilinx的原語OSERDESE2是一種專用的并-串轉換器,每個OSERDESE2模塊都包括一個專用串行化程序用于數據和3狀態控制。數據和3狀態序列化程序都可以工作在SDR和DDR模式。數據串行化的位寬可以達到8:1(如果使用原語模塊級聯,則可以到10:1和14:1)。3狀態序列化最高可達14:1,有一個專用的DDR3模式可用于支持高速內存應用程序。

OSERDESE2的框圖如下:

OSERDESE2的端口說明如下:

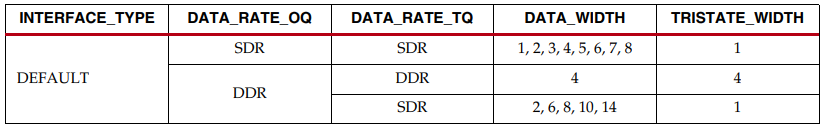

需要例化的一些可用屬性如下:

TRISTATE_WIDTH的選取見下表:

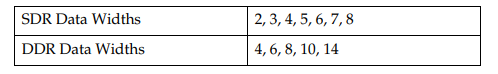

SDR、DDR輸出模式下位寬的選取有如下限制:

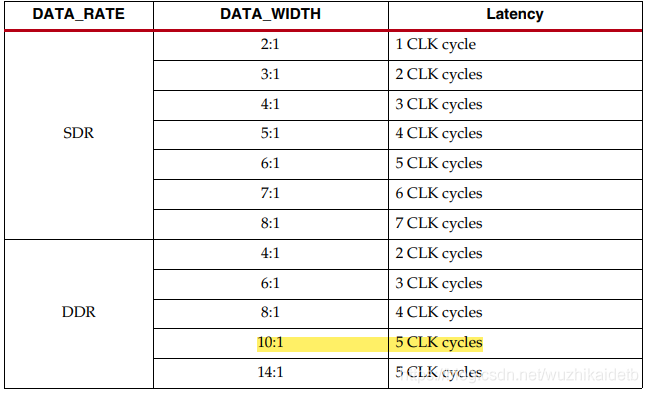

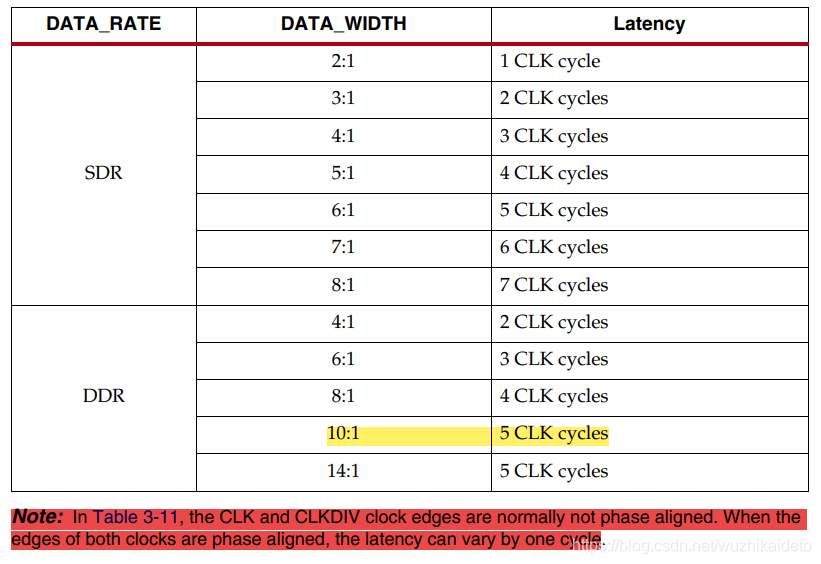

輸出數據會有一些時鐘周期的延遲,具體見下表:

3、8位數據的并串轉換

接下里例化一個原語來熟悉下用法,8位數據的并串轉換,采用DDR輸出。

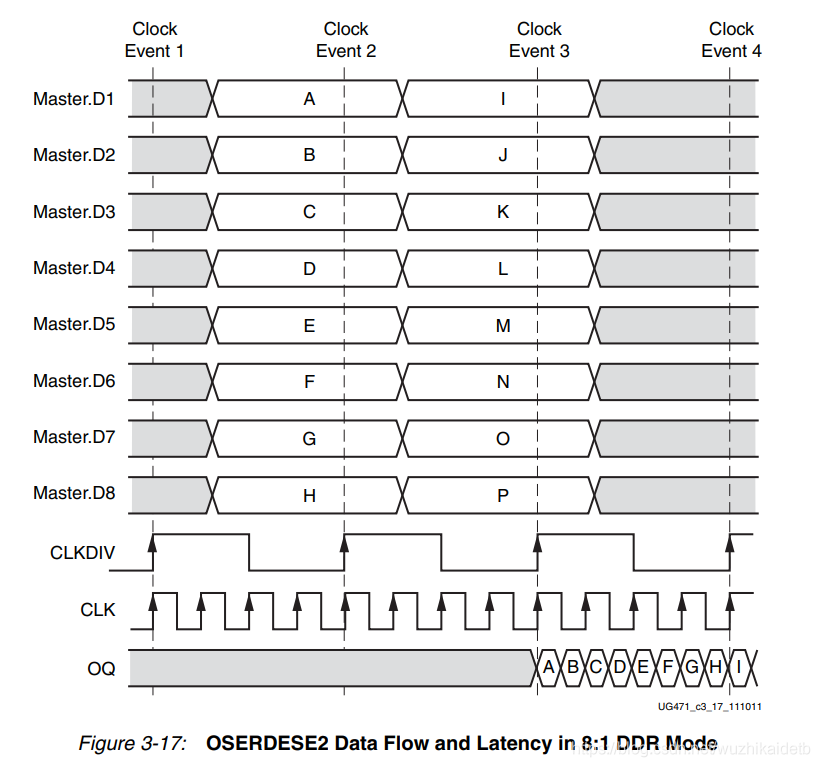

官方手冊的8位DDR轉化時序圖如下:

例化原語OSERDESE2(打開VIvado--Tools--Language Templates,搜索“OSERDESE2”,可以找到Xilinx提供的模板),與DDR、3態控制相關的端口,輸入全設置為0,輸出不關心,編寫Verilog如下:

//------------------------------------------------------------------------

//--OSERDESE2測試模塊

//------------------------------------------------------------------------

//--------------------------------------------------------

module serializer(

input clk_ser , //串行輸出時鐘,50M*4=200M

input clk_per , //并行輸入時鐘,50M

input rst_n , //復位信號,低電平有效

input [7:0] par_data , //并行輸入數據

output ser_data //串行輸出數據

);

//---------------------------------------------------------------

OSERDESE2 #(

.DATA_RATE_OQ ("DDR") , // DDR, SDR

.DATA_RATE_TQ ("SDR") , // DDR, BUF, SDR

.DATA_WIDTH (8) , // Parallel data width (2-8,10,14)

.INIT_OQ (1'b0) , // Initial value of OQ output (1'b0,1'b1)

.INIT_TQ (1'b0) , // Initial value of TQ output (1'b0,1'b1)

.SERDES_MODE ("MASTER") , // MASTER, SLAVE

.SRVAL_OQ (1'b0) , // OQ output value when SR is used (1'b0,1'b1)

.SRVAL_TQ (1'b0) , // TQ output value when SR is used (1'b0,1'b1)

.TBYTE_CTL ("FALSE") , // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC ("FALSE") , // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH (1) // 3-state converter width (1,4)

)

OSERDESE2_inst (

.OFB () , // 1-bit output: Feedback path for data

.OQ (ser_data) , // 1-bit output: Data path output

.SHIFTOUT1 () ,

.SHIFTOUT2 () ,

.TBYTEOUT () , // 1-bit output: Byte group tristate

.TFB () , // 1-bit output: 3-state control

.TQ () , // 1-bit output: 3-state control

.CLK (clk_ser) , // 1-bit input: High speed clock

.CLKDIV (clk_per) , // 1-bit input: Divided clock

.D1 (par_data[0]) ,

.D2 (par_data[1]) ,

.D3 (par_data[2]) ,

.D4 (par_data[3]) ,

.D5 (par_data[4]) ,

.D6 (par_data[5]) ,

.D7 (par_data[6]) ,

.D8 (par_data[7]) ,

.OCE (1'b1) , // 1-bit input: Output data clock enable

.RST (~rst_n) , // 1-bit input: Reset

.SHIFTIN1 () ,

.SHIFTIN2 () ,

.T1 (1'b0) ,

.T2 (1'b0) ,

.T3 (1'b0) ,

.T4 (1'b0) ,

.TBYTEIN (1'b0) , // 1-bit input: Byte group tristate

.TCE (1'b0) // 1-bit input: 3-state clock enable

);

endmodule

每隔20ns隨機生成1個8位2進制數據作為并行輸入,觀察串行輸出,Testbench如下:

//------------------------------------------------

//--OSERDESE2原語仿真

//------------------------------------------------

`timescale 1ns / 1ps //時間單位/精度

//----------------------------------------------------

module tb_serializer();

reg clk_per ;

reg clk_ser ;

reg rst_n ;

reg [7:0] par_data ;

wire ser_data ;

//----------------------------------------------------

initial begin

clk_per clk_ser rst_n par_data #180

rst_n end

//----------------------------------------------------------

always #10 clk_per = ~clk_per;

always #2.5 clk_ser = ~clk_ser;

always #20 par_data

//----------------------------------------------------

serializer serializer_inst(

.clk_per (clk_per) ,

.clk_ser (clk_ser) ,

.rst_n (rst_n) ,

.par_data (par_data) ,

.ser_data (ser_data)

);

endmodule

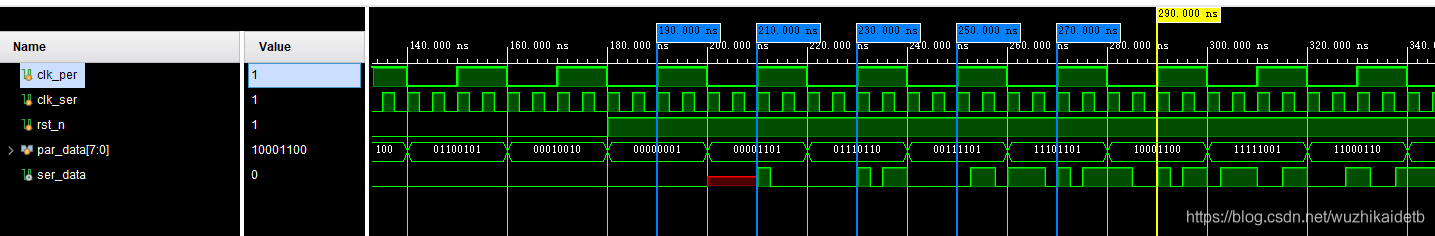

仿真結果如下:

可以看出:

在第1條藍線處,是復位后并行時鐘的第1個上升沿,此時采集到的數據為0000_0001

在第2條藍線處,也就是4個串行時鐘的延遲后,串行輸出開始有數據,分別為1-0-0-0-0-0-0-0,可以看出是第1個上升沿采集到的數據輸出(0000_0001從低位往高位輸出)

在第2條藍線處,是復位后并行時鐘的第2個上升沿,此時采集到的數據為0000_1101

在第3條藍線處,也就是4個串行時鐘的延遲后,串行輸出開始有數據,分別為1-0-1-1-0-0-0-0,可以看出是第2個上升沿采集到的數據輸出(0000_1101從低位往高位輸出)

其他與上述相同,符合官方給出的時序圖

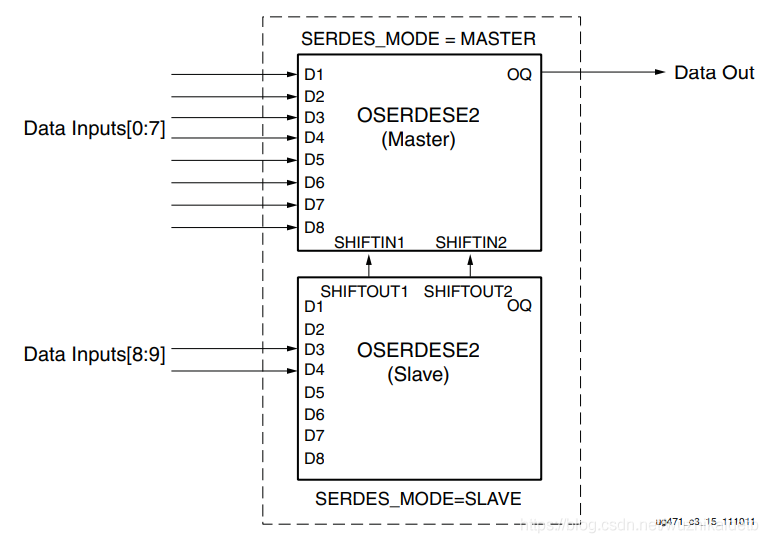

4、10位數據的并串轉換(級聯)

OSERDESE2原語還支持例化兩次原語級聯,以便實現10位、14位位寬的串行化轉換。下圖是10位位寬的級聯框圖,其中一個設置位MASTER,另一個設置為SLAVE,通過SHIFTIN與SHIFTOUT連接。

需要注意:數據的輸出從MASTER輸出,數據的高位輸入到SLAVE模塊時,需要從D3開始(只能使用D3~D8)

接下里例化一個原語來實現10位數據的并串轉換,采用DDR輸出。

例化2個原語OSERDESE2級聯(打開VIvado--Tools--Language Templates,搜索“OSERDESE2”,可以找到Xilinx提供的模板),與DDR、3態控制相關的端口,輸入全設置為0,輸出不關心,編寫Verilog如下:

//------------------------------------------------------------------------

//--OSERDESE2測試模塊

//------------------------------------------------------------------------

//--------------------------------------------------------

module serializer(

input clk_ser , //串行輸出時鐘,50M*5=250M

input clk_per , //并行輸入時鐘,50M

input rst_n , //復位信號,低電平有效

input [9:0] par_data , //并行輸入數據,位寬10

output ser_data //串行輸出數據

);

//------------------------------------------------------------------

wire shift1; //級聯線1

wire shift2; //級聯線2

//------------------------------------------------------------------

//例化主模塊MASTER

OSERDESE2 #(

.DATA_RATE_OQ ("DDR") , // DDR, SDR

.DATA_RATE_TQ ("SDR") , // DDR, BUF, SDR

.DATA_WIDTH (10) , // Parallel data width (2-8,10,14)

.INIT_OQ (1'b0) , // Initial value of OQ output (1'b0,1'b1)

.INIT_TQ (1'b0) , // Initial value of TQ output (1'b0,1'b1)

.SERDES_MODE ("MASTER") , // MASTER, SLAVE

.SRVAL_OQ (1'b0) , // OQ output value when SR is used (1'b0,1'b1)

.SRVAL_TQ (1'b0) , // TQ output value when SR is used (1'b0,1'b1)

.TBYTE_CTL ("FALSE") , // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC ("FALSE") , // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH (1) // 3-state converter width (1,4)

)

OSERDESE2_inst1 (

.OFB () , // 1-bit output: Feedback path for data

.OQ (ser_data) , // 1-bit output: Data path output

.SHIFTOUT1 () ,

.SHIFTOUT2 () ,

.TBYTEOUT () , // 1-bit output: Byte group tristate

.TFB () , // 1-bit output: 3-state control

.TQ () , // 1-bit output: 3-state control

.CLK (clk_ser) , // 1-bit input: High speed clock

.CLKDIV (clk_per) , // 1-bit input: Divided clock

.D1 (par_data[0]) ,

.D2 (par_data[1]) ,

.D3 (par_data[2]) ,

.D4 (par_data[3]) ,

.D5 (par_data[4]) ,

.D6 (par_data[5]) ,

.D7 (par_data[6]) ,

.D8 (par_data[7]) ,

.OCE (1'b1) , // 1-bit input: Output data clock enable

.RST (~rst_n) , // 1-bit input: Reset

.SHIFTIN1 (shift1) ,

.SHIFTIN2 (shift2) ,

.T1 (1'b0) ,

.T2 (1'b0) ,

.T3 (1'b0) ,

.T4 (1'b0) ,

.TBYTEIN (1'b0) , // 1-bit input: Byte group tristate

.TCE (1'b0) // 1-bit input: 3-state clock enable

);

//例化從模塊SLAVE

OSERDESE2 #(

.DATA_RATE_OQ ("DDR") , // DDR, SDR

.DATA_RATE_TQ ("SDR") , // DDR, BUF, SDR

.DATA_WIDTH (10) , // Parallel data width (2-8,10,14)

.INIT_OQ (1'b0) , // Initial value of OQ output (1'b0,1'b1)

.INIT_TQ (1'b0) , // Initial value of TQ output (1'b0,1'b1)

.SERDES_MODE ("SLAVE") , // MASTER, SLAVE

.SRVAL_OQ (1'b0) , // OQ output value when SR is used (1'b0,1'b1)

.SRVAL_TQ (1'b0) , // TQ output value when SR is used (1'b0,1'b1)

.TBYTE_CTL ("FALSE") , // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC ("FALSE") , // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH (1) // 3-state converter width (1,4)

)

OSERDESE2_inst2 (

.OFB () , // 1-bit output: Feedback path for data

.OQ () , // 1-bit output: Data path output

.SHIFTOUT1 (shift1) ,

.SHIFTOUT2 (shift2) ,

.TBYTEOUT () , // 1-bit output: Byte group tristate

.TFB () , // 1-bit output: 3-state control

.TQ () , // 1-bit output: 3-state control

.CLK (clk_ser) , // 1-bit input: High speed clock

.CLKDIV (clk_per) , // 1-bit input: Divided clock

.D1 () ,

.D2 () ,

.D3 (par_data[8]) ,

.D4 (par_data[9]) ,

.D5 () ,

.D6 () ,

.D7 () ,

.D8 () ,

.OCE (1'b1) , // 1-bit input: Output data clock enable

.RST (~rst_n) , // 1-bit input: Reset

.SHIFTIN1 () ,

.SHIFTIN2 () ,

.T1 (1'b0) ,

.T2 (1'b0) ,

.T3 (1'b0) ,

.T4 (1'b0) ,

.TBYTEIN (1'b0) , // 1-bit input: Byte group tristate

.TCE (1'b0) // 1-bit input: 3-state clock enable

);

endmodule

每隔20ns隨機生成1個10位2進制數據作為并行輸入,觀察串行輸出,Testbench如下:

//------------------------------------------------

//--OSERDESE2原語仿真

//------------------------------------------------

`timescale 1ns / 1ps //時間單位/精度

//----------------------------------------------------

module tb_serializer();

reg clk_per ;

reg clk_ser ;

reg rst_n ;

reg [9:0] par_data ;

wire ser_data ;

//----------------------------------------------------

initial begin

clk_per clk_ser rst_n par_data #180

rst_n end

//----------------------------------------------------------

always #10 clk_per = ~clk_per;

always #2 clk_ser = ~clk_ser;

always #20 par_data

//----------------------------------------------------

serializer serializer_inst(

.clk_per (clk_per) ,

.clk_ser (clk_ser) ,

.rst_n (rst_n) ,

.par_data (par_data) ,

.ser_data (ser_data)

);

endmodule

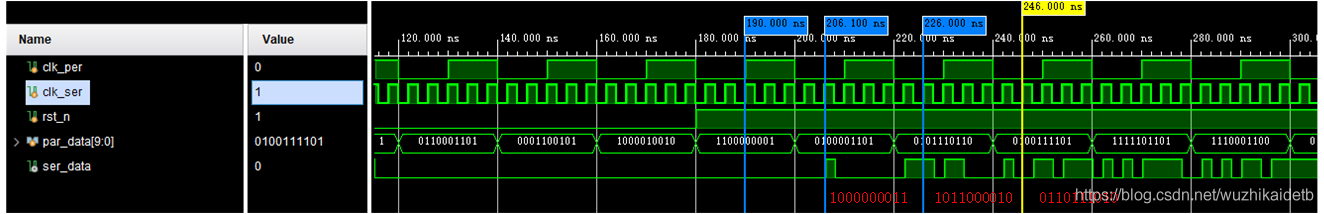

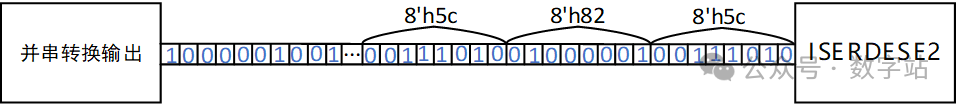

仿真結果如下:

可以看出:

在第1條藍線處,是復位后并行時鐘的第1個上升沿,此時采集到的數據為11000_00001

在第2條藍線處,也就是4個串行時鐘的延遲后,串行輸出開始有數據,分別為1-0-0-0-0-0-0-0-1-1,可以看出是第1個上升沿采集到的數據輸出(11000_00001從低位往高位輸出)

在第2條藍線處,是復位后并行時鐘的第2個上升沿,此時采集到的數據為01000_01101

在第3條藍線處,也就是4個串行時鐘的延遲后,串行輸出開始有數據,分別為1-0-1-1-0-0-0-0-1-0,可以看出是第2個上升沿采集到的數據輸出(01000_01101從低位往高位輸出)

其他與上述相同。

這里官方手冊沒有給出10bitDDR輸出的時序圖,輸出延遲給出的表如下圖:

可以看到這里10:1的輸出延遲應該是5個時鐘周期,但是我上面仿真的卻是4個時鐘周期,一開始我還以為是哪里錯了,搞得我重復仿真了好幾遍,后面又看了一下手冊,終于在延遲表的下面發現了這句話(上圖標紅):CLK、CLKDIV的時鐘沿通常不是相位一致的。當這兩個時鐘的時鐘沿相位一致時,延遲會存在一個周期的差異。

這樣的話,仿真結果應該是沒有問題。

審核編輯:湯梓紅

-

轉換器

+關注

關注

27文章

9014瀏覽量

151383 -

Xilinx

+關注

關注

73文章

2184瀏覽量

124899 -

仿真

+關注

關注

52文章

4255瀏覽量

135598

發布評論請先 登錄

詳解Xilinx的10G PCS PMA IP

ISERDESE2原語端口及參數介紹

Xilinx原語OSERDESE2的使用和仿真詳解

Xilinx原語OSERDESE2的使用和仿真詳解

評論