編者按:

模數(shù)轉(zhuǎn)換器 (ADC) 將模擬世界連接到數(shù)字世界,因此是連接到現(xiàn)實(shí)世界的任何電子系統(tǒng)的基本部件。它們也是決定系統(tǒng)性能的關(guān)鍵因素之一。本文將說(shuō)明三角積分ADC如何能夠生成超低噪聲結(jié)果。

三角積分 (Δ?) 集成電路拓?fù)淙栽谀?shù)轉(zhuǎn)換器 (ADC) 中廣泛使用,為過(guò)程控制、精密溫度測(cè)量和稱重儀應(yīng)用提供高分辨率、高集成度和低功耗的解決方案。

關(guān)于這種轉(zhuǎn)換器有一個(gè)令人費(fèi)解的事實(shí),它從1位轉(zhuǎn)換開(kāi)始,理論信噪比 (SNR) 為7.78dB,相當(dāng)于5V系統(tǒng)中存在2V (VRMS) 噪聲。在此基礎(chǔ)之上,該ADC可發(fā)展為真正的24位三角積分轉(zhuǎn)換器,提供146dB的理論SNR,相當(dāng)于5V系統(tǒng)中存在244nV的RMS噪聲。

分辨率能夠從1位躍升至24位,主要依賴過(guò)采樣算法、噪聲整形調(diào)制器和數(shù)字濾波器來(lái)降低量化噪聲并提高SNR。通過(guò)改用放大器輸入級(jí)饋入12位或16位逐次逼近寄存器(SAR) ADC,這種方法可以規(guī)避Δ?轉(zhuǎn)換器的復(fù)雜性及其相關(guān)的噪聲。此設(shè)計(jì)路徑行之有效,但需要在印刷電路板上使用更多的集成電路并增加BOM成本。

有一種更好的方法可以解決噪聲問(wèn)題:利用超低噪聲Δ? ADC,該問(wèn)題可以迎刃而解。

本文將簡(jiǎn)要討論低噪聲目標(biāo)應(yīng)用以及如何在內(nèi)部設(shè)計(jì)Δ? ADC來(lái)滿足這一要求。然后介紹Texas Instruments的兩款Δ? ADC,其中一款強(qiáng)調(diào)24位精度,另一款強(qiáng)調(diào)32位精度,同時(shí)還將說(shuō)明如何利用這兩款產(chǎn)品中強(qiáng)大的數(shù)字濾波功能。

Δ? ADC的適用場(chǎng)景

從模擬的角度來(lái)看,工程師在測(cè)量溫度、壓力、測(cè)壓元件和光學(xué)傳感器的輸出時(shí),需要不同的精度。從根本上講,放大器增強(qiáng)了設(shè)計(jì)人員量化這類較小模擬量(多數(shù)情況下接近于 DC)的能力。漸進(jìn)式數(shù)字化帶來(lái)了視角和功能上的變化,同時(shí)增強(qiáng)了存儲(chǔ)和修改傳感器信號(hào)的能力。

為實(shí)現(xiàn)數(shù)字捕獲,典型的傳感器信號(hào)路徑始于傳感器,經(jīng)過(guò)增益、多路復(fù)用和濾波器級(jí),然后到達(dá)ADC(圖1a)。

圖1a中的轉(zhuǎn)換器是一個(gè)SAR ADC,可以執(zhí)行12位到18位轉(zhuǎn)換,并且能以高達(dá)10兆次采樣/秒 (MSPS) 的轉(zhuǎn)換速率運(yùn)行。16位轉(zhuǎn)換器可提供216,即65,536個(gè)段。在5V系統(tǒng)中,最低有效位(LSB) 為5V/216298,即76.3μV,理論SNR等于98dB。通過(guò)在SAR轉(zhuǎn)換器之前執(zhí)行模擬增益,可以實(shí)現(xiàn)更高的精細(xì)度。

Δ?信號(hào)鏈(圖1b)利用單個(gè)轉(zhuǎn)換器提高了信號(hào)鏈的分辨率,同時(shí)也降低了BOM成本。Δ? ADC可提供16位到32位轉(zhuǎn)換。在此信號(hào)鏈中,24位Δ? ADC可提供224,即16,777,216個(gè)段。因此,在5V系統(tǒng)中,LSB為5V/224,即298nV,理論SNR等于146dB。此分辨率水平為轉(zhuǎn)換器提供了更加接近傳感器能力的精細(xì)度。

由于內(nèi)部數(shù)字濾波器需要時(shí)間來(lái)實(shí)現(xiàn)濾波計(jì)算,因此24位Δ? ADC的速度較慢。該轉(zhuǎn)換器的典型輸出數(shù)據(jù)速率范圍為幾赫茲至1MSPS。請(qǐng)注意,模擬濾波器現(xiàn)在采用的是便宜的一階電阻電容 (RC) 濾波器,而不是復(fù)雜的三重運(yùn)算放大器五階模擬濾波器。

這兩種方法的噪聲之間區(qū)別很明顯:Δ? ADC的低噪聲性能優(yōu)于SARADC(表1)。

* 備注:SNR = 6.02N + 1.76,其中N是位數(shù)

在溫度、壓力和測(cè)壓元件這類傳感器解決方案中,若不太注重速度規(guī)格,但精度至關(guān)重要,那么Δ? ADC可提供出色的解決方案。該ADC可通過(guò)使用數(shù)字而不是模擬降噪技術(shù),實(shí)現(xiàn)低至上述小電壓值的轉(zhuǎn)換。

Δ? ADC的內(nèi)部構(gòu)造

Δ? ADC的內(nèi)部80%為數(shù)字構(gòu)造。通常,轉(zhuǎn)換器接收輸入信號(hào),并立即將該模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)。然后,轉(zhuǎn)換器將該數(shù)字信號(hào)與后續(xù)的調(diào)制器轉(zhuǎn)換合并到一個(gè)數(shù)字濾波器級(jí),在該濾波器級(jí)中,累加的1位信號(hào)變?yōu)槎辔弧=酉聛?lái),轉(zhuǎn)換器通過(guò)數(shù)字輸出級(jí),以串行方式將最終的多位轉(zhuǎn)換發(fā)送到等待的微控制器。

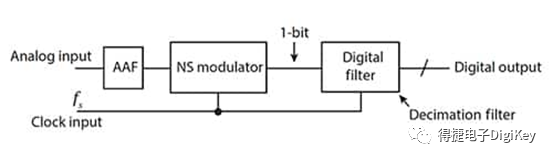

模擬信號(hào)首先通過(guò)外部的一階抗混疊濾波器 (AAF)。然后,噪聲整形 (NS)調(diào)制器獲取模擬信號(hào),并以轉(zhuǎn)換器的時(shí)鐘速率生成1位信號(hào)流進(jìn)入數(shù)字濾波器(圖2)。

圖2:典型Δ?使模擬信號(hào)通過(guò)一階AAF,使用NS調(diào)制器生成1位信號(hào)流,然后在連接到微控制器的數(shù)字輸出端產(chǎn)生一個(gè)多位結(jié)果。(圖片來(lái)源:CMOS:Mixed-Signal Circuit Design,2nd Edition,J. Baker,ISBN 978-0-470-29026-2)

數(shù)字濾波器按時(shí)鐘輸入1位信號(hào)流中的多個(gè)代碼,并在數(shù)字濾波器中創(chuàng)建完整的多位結(jié)果。這些多位結(jié)果將通過(guò)數(shù)字輸出進(jìn)行串行傳輸。

Δ?調(diào)制器

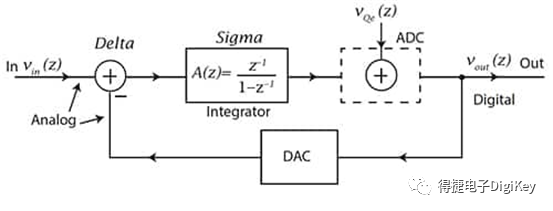

積分器/反饋回路的數(shù)量決定了Δ?調(diào)制器的階數(shù)。一階Δ? ADC調(diào)制器只有一個(gè)積分器和反饋環(huán)路(圖3)。

圖3:一階調(diào)制器具有一個(gè)模擬積分器以及1位ADC和反饋回路中的DAC。VQe(z) 是量化ADC噪聲。(圖片來(lái)源:CMOS: Mixed-SignalCircuit Design,2nd Edition,J.Baker,ISBN 978-0-470-29026-2)

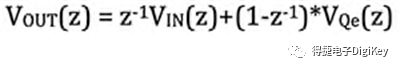

在圖3中,模擬信號(hào) (VIN(z)) 進(jìn)入調(diào)制器的Delta(Δ) 部分。然后,模擬信號(hào)經(jīng)過(guò)積分器級(jí)或Sigma (?) 級(jí)到達(dá)一個(gè)1位ADC(根據(jù)圖2,采樣率為fS),該ADC可以是比較器。現(xiàn)在,這一經(jīng)過(guò)時(shí)鐘數(shù)字化處理的信號(hào)反饋到1位數(shù)模轉(zhuǎn)換器 (DAC),同時(shí)繼續(xù)前往Δ級(jí)的VOUT(z)。1位DAC提供了一個(gè)需要從模擬輸入信號(hào)VIN(z) 中扣減的模擬電壓。該一階調(diào)制器的傳遞函數(shù)為:

公式1

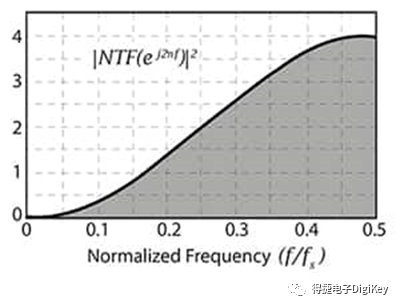

由于存在積分器和反饋回路,調(diào)制器在本身的數(shù)字輸出數(shù)據(jù)流上實(shí)現(xiàn)了噪聲整形算法(圖4)。

圖4:在位于Δ?調(diào)制器輸出端的噪聲整形函數(shù)中,噪聲傳遞函數(shù) (NTF) 等于1-z-1,其中0.5歸一化頻率等于FS/2。(圖片來(lái)源:Understanding Delta-Sigma Data Converters, Schreier,Temes,ISBN 0-471-46585-2)

在圖4中,噪聲整形特性是降低轉(zhuǎn)換1位量化噪聲的第一步。隨著噪聲成功推至更高頻率,由一個(gè)低通數(shù)字濾波器完成了降噪過(guò)程。

高階調(diào)制器包含更多積分器和反饋回路。例如,三階調(diào)制器具有三個(gè)積分器和三個(gè)反饋回路。噪聲整形函數(shù)通過(guò)降低DC附近的噪聲并增加整形噪聲,隨調(diào)制器階數(shù)的變化而變化。

高階調(diào)制器以增加硅硬件、降低穩(wěn)定性和信號(hào)范圍為代價(jià),提供了更高的性能。

Δ?數(shù)字濾波器

Δ? ADC在運(yùn)行時(shí)采用了過(guò)采樣 (OS)。過(guò)采樣是調(diào)制器采樣率 (FS) 與ADC輸出數(shù)據(jù)速率 (FD) 之比,如公式2所示:

公式2

公式2

過(guò)采樣通過(guò)使用低通數(shù)字濾波器,以數(shù)字方式限制經(jīng)過(guò)噪聲整形的數(shù)據(jù)的帶寬,來(lái)改善Δ? ADC的噪聲。

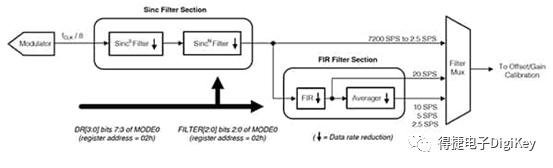

在Δ? ADC中,兩個(gè)常用的數(shù)字濾波器是sin(pf)/pf(sinc) 和線性相位有限沖激響應(yīng) (FIR) 濾波器。在TexasInstruments的ADS1235 24位Δ? ADC、ADS1262和ADS1263 32位Δ? ADC(其中ADS1263集成了一個(gè)適用于背景測(cè)量的24位輔助Δ? ADC)中,數(shù)字濾波器實(shí)現(xiàn)提供了以下選擇:專門使用sinc濾波器,或使用sinc濾波器后跟FIR濾波器的組合(圖5)。

圖5:ADS1235 24位Δ? ADC可以專門使用sinc濾波器,或使用sinc濾波器后跟FIR濾波器的組合。(圖片來(lái)源:TexasInstruments)

在圖5中,sinc(表示“Sinc”)濾波器是低通數(shù)字濾波器。sinc 濾波器的輸出 (w(n)) 可使用公式3計(jì)算:

公式3

z域傳遞函數(shù)為:

公式4

頻率響應(yīng)為:

公式5

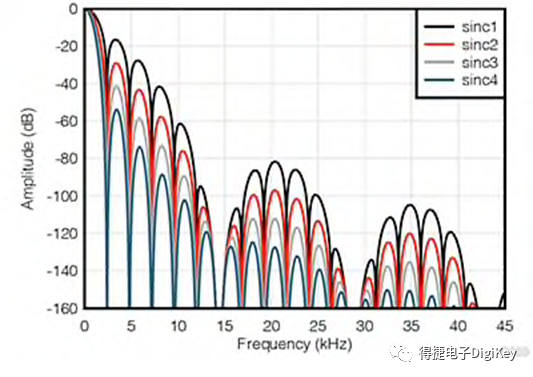

在圖5中,SincN等同于串聯(lián)N個(gè)相同的sinc濾波器。sinc濾波器的幅度與頻率響應(yīng)圖形具有梳狀外觀(圖6)。

圖6:在每秒2400次采樣 (SPS) 的ADS1262/63中,多個(gè)sinc數(shù)字濾波器產(chǎn)生了梳狀頻率響應(yīng);其中sinc2等效于串聯(lián)兩個(gè)相同的sinc濾波器,sinc3等效于串聯(lián)三個(gè)相同的sinc濾波器,依此類推。(圖片來(lái)源:Texas Instruments)

在圖6中,峰值和零點(diǎn)是sinc濾波器響應(yīng)的特征。頻率響應(yīng)零點(diǎn)出現(xiàn)在f(Hz) = N ·FD,其中N = 1, 2, 3, 。..。在零頻率處,濾波器的增益為零。

sinc濾波器(串聯(lián))會(huì)增加衰減,導(dǎo)致延時(shí)增加。例如,如果在外部時(shí)鐘速率為7.3728MHz的特定sinc濾波器計(jì)算中,產(chǎn)生的輸出數(shù)據(jù)速率為14400SPS,則第二個(gè)sinc濾波器的輸出數(shù)據(jù)速率為7200SPS。

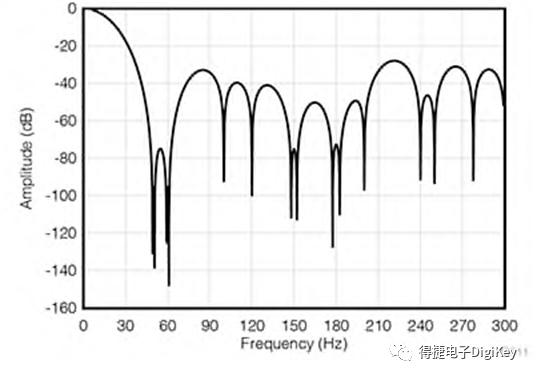

低通FIR濾波器是基于系數(shù)的濾波器。該濾波器具有50Hz和60Hz的同時(shí)衰減功能,以及2.5SPS至20SPS數(shù)據(jù)速率下的諧波功能。FIR濾波器數(shù)據(jù)速率的轉(zhuǎn)換延時(shí)相當(dāng)于一個(gè)周期。FIR濾波器從sinc濾波器接收經(jīng)過(guò)預(yù)濾波的數(shù)據(jù),并對(duì)數(shù)據(jù)進(jìn)行抽取,以產(chǎn)生10SPS的輸出數(shù)據(jù)速率(圖7)。

圖7:在ADS1262/63中,F(xiàn)IR濾波器可衰減50Hz和60Hz信號(hào)以降低線路頻率干擾,并提供一系列靠近這些頻率的響應(yīng)零點(diǎn)。零點(diǎn)在50Hz和60Hz諧波處重復(fù)出現(xiàn)。(圖片來(lái)源:Texas Instruments)

FIR濾波器會(huì)衰減50Hz和60Hz信號(hào)以降低線路頻率干擾,并提供一系列靠近這些頻率的響應(yīng)零點(diǎn)。響應(yīng)零點(diǎn)在50Hz和60Hz諧波處重復(fù)出現(xiàn)。

精密的低噪聲Δ? ADC

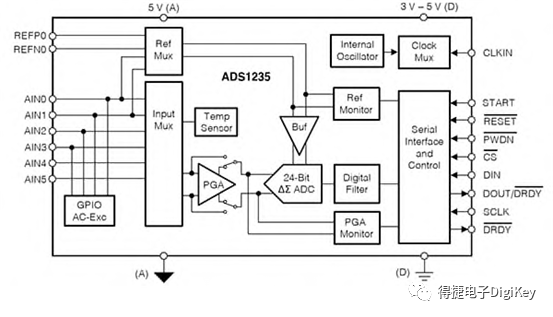

先前提到的Texas Instruments的ADS1235差分輸入24位轉(zhuǎn)換器是低噪聲Δ? ADC的極好例子。

ADS1235是一款精密的7200SPS Δ? ADC,具有三個(gè)差分或五個(gè)單端輸入,以及一個(gè)集成式可編程增益放大器 (PGA),其增益包括1、64和128。該器件還包括診斷功能,例如PGA超量程和參考監(jiān)視器。該ADC為包括稱重儀、應(yīng)變片和電阻式壓力傳感器在內(nèi)的高精度設(shè)備提供了高精度、零漂移的轉(zhuǎn)換數(shù)據(jù)(圖8)。

圖8:具有六通道模擬輸入和GPIO輸入多路復(fù)用器的ADS123524位Δ? ADC方框圖。(圖片來(lái)源:Texas Instruments)

對(duì)于ADS1235,影響噪聲性能的重要因素包括數(shù)據(jù)速率、PGA增益和斬波模式。數(shù)據(jù)速率較慢會(huì)在數(shù)字濾波器中引入轉(zhuǎn)折頻率,從而降低噪聲。此外,由于在斬波模式下執(zhí)行的兩點(diǎn)數(shù)據(jù)平均化,與正常操作相比,噪聲降低了√2倍。

在低頻、2.5SPS數(shù)據(jù)速率和1V/V PGA增益條件下,5V系統(tǒng)中的sinc3數(shù)字輸出的轉(zhuǎn)換器噪聲為0.15mVRMS(0.3mV峰峰值 (PP)),有效分辨率為24位,無(wú)噪聲分辨率為24位。該器件的理論和實(shí)際SNR均為146dB。事實(shí)上,在這些條件下,穩(wěn)定的四階調(diào)制器和sinc1至sinc4濾波器均可產(chǎn)生24位有效分辨率,以及24位無(wú)噪聲分辨率。

ADS1235已針對(duì)2.5SPS數(shù)據(jù)速率實(shí)現(xiàn)了近乎完美的24位轉(zhuǎn)換。此系列中的下一代Δ? ADC是TexasInstruments的ADS1262/63。這些器件之間的主要區(qū)別在于ADS1262/63改善了低噪聲電路,并提供了擴(kuò)展的32位輸出數(shù)據(jù)寄存器。

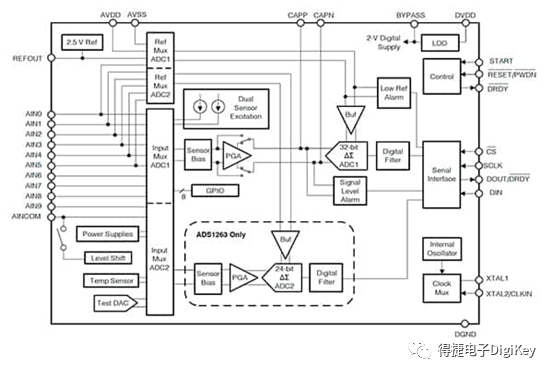

ADS1262/63具有改進(jìn)的低噪聲CMOS PGA,其增益包括1、2、4、8、16和32。模擬前端(AFE) 非常靈活,包含兩個(gè)傳感器激勵(lì)電流源,非常適合直接RTD測(cè)量(圖9)。

圖9:具有十通道模擬輸入多路復(fù)用器的ADS1262和ADS126332位Δ? ADC方框圖。ADS1263具有第二個(gè)片上24位Δ? ADC。(圖片來(lái)源:Texas Instruments)

與ADS1235一樣,PGA增益、數(shù)據(jù)速率、數(shù)字濾波器模式和斬波模式是影響ADS1262/63噪聲性能的重要因素。ADS1262/63具有32位分辨率,真正展現(xiàn)了低噪聲深度功能。

首先,穩(wěn)定的四階調(diào)制器和sinc1至sinc4濾波器都能實(shí)現(xiàn)32位有效分辨率以及24位無(wú)噪聲分辨率。通過(guò)配置低頻率、2.5SPS數(shù)據(jù)速率和1V/V PGA增益(已旁通),5V系統(tǒng)中的sinc3數(shù)字輸出的轉(zhuǎn)換器噪聲僅為0.08mVRMS(0.307mVPP)。該器件以26.9位超越了有效分辨率,以及25位無(wú)噪聲分辨率。對(duì)于此32位系統(tǒng),理論SNR為387dB,實(shí)際SNR等于164dB。

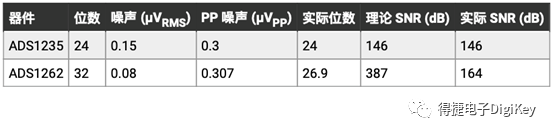

24位和32位轉(zhuǎn)換器的噪聲之間區(qū)別非常明顯,其中32位Δ? ADC的低噪聲性能優(yōu)于24位 Δ? ADC(表2)。

* 備注:SNR =6.02N + 1.76,其中N是位數(shù)

表2:滿量程輸入電壓5V的ADC RMS噪聲、峰值噪聲和SNR的比較結(jié)果。(數(shù)據(jù)來(lái)源:Digi-Key Electronics)

總結(jié)

Δ? ADC仍在不斷增加功能,持續(xù)提升低噪聲極限。本文介紹了如何將這種近乎數(shù)字化的低噪聲ADC直接對(duì)應(yīng)到溫度、壓力和測(cè)壓元件應(yīng)用中。在討論精密型24位Δ? ADC和32位Δ? ADC的具體細(xì)節(jié)的同時(shí),概括了實(shí)現(xiàn)超精密特性的途徑。

責(zé)任編輯:haq

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8962瀏覽量

150785 -

adc

+關(guān)注

關(guān)注

99文章

6641瀏覽量

548311

原文標(biāo)題:話說(shuō)ADC之四 | 突破Δ? ADC低噪聲性能極限,應(yīng)該怎么做?

文章出處:【微信號(hào):得捷電子DigiKey,微信公眾號(hào):得捷電子DigiKey】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

一篇文章教你使用運(yùn)放實(shí)現(xiàn)三角波、方波(詳細(xì)電路分析)+multisim仿真

馬達(dá)控制上必要的知識(shí) 三角函數(shù)

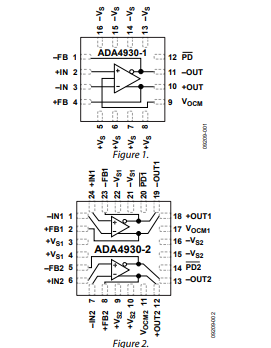

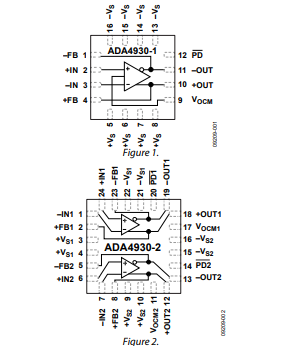

ADA4930-2超低噪聲驅(qū)動(dòng)器,適用于低壓ADC技術(shù)手冊(cè)

ADA4930-1超低噪聲驅(qū)動(dòng)器,適用于低壓ADC技術(shù)手冊(cè)

用DAC8562輸出一個(gè)三角波測(cè)試,用示波器發(fā)現(xiàn)輸出的三角波有毛刺,怎么解決?

LHA7532B:76.8kHz集成PGA超低噪聲32位ΣΔADC

揭秘使用20位DAC生成超低噪聲、高保真波形的設(shè)計(jì)挑戰(zhàn)

AMC1204-Q1針對(duì)電流分流測(cè)量的20MHz,二階,隔離型三角積分調(diào)制器數(shù)據(jù)表

三角波發(fā)生器的組成和應(yīng)用

求助,求推薦超低噪聲跨阻放大器

ADC354x 14位10MSPS至65MSPS低噪聲、超低功耗ADC數(shù)據(jù)表

三相負(fù)載與三角聯(lián)結(jié)的關(guān)系

ADC3564 14位、125MSPS、低噪聲、超低功耗ADC數(shù)據(jù)表

ADC358x 18位0.5MSPS至65MSPS低噪聲、超低功耗ADC數(shù)據(jù)表

三角積分ADC如何能夠生成超低噪聲結(jié)果

三角積分ADC如何能夠生成超低噪聲結(jié)果

評(píng)論