芯東西12月30日消息,英特爾在本周的IEEE國際電子設備會議上展示了一項新的研究,或為續(xù)命摩爾定律提供下一步可行方向。

此項研究是英特爾一直熱衷的堆疊納米片晶體管技術,通過將PMOS和NMOS兩種晶體管堆疊起來,可以將CMOS電路的面積減少一半,這意味著未來集成電路晶體管密度可能會翻番。

一、用最簡單CMOS器件做實驗,尺寸大小減一半

幾乎每一臺電子設備都離不開NMOS和PMOS兩種晶體管的“協(xié)同合作”。在相同的電壓下,兩個晶體管只有一個會打開,把它們放在一起意味著只要有其中之一發(fā)生改變,電流才會流動,這大大地降低了能耗。

幾十年以來,NMOS和PMOS晶體管在CMOS電路中一直并排放置,如果我們想讓CMOS電路的尺寸更小,那兩個晶體管的位置就應該更加貼近。

英特爾選擇的方式,就是讓它們堆疊起來。

▲堆疊的NMOS和PMOS晶體管(圖源:英特爾)

有了堆疊晶體管這一巧思,英特爾使用了被稱為下一代晶體管結構的納米片晶體管技術。不同于以往晶體管主要由垂直硅鰭片構成,納米片(nanosheet)的溝道區(qū)由多層、水平的、納米級薄的片層堆疊而成。

▲CMOS器件由平面發(fā)展至FinFET、納米薄片,進一步縮小電路尺寸。(圖源:英特爾)

基于以上的思路,英特爾的工程師們設計了最簡單的CMOS邏輯電路,即反相器,它只包含兩個晶體管、兩個電源連接、一個輸出和一個輸入互連接口。

二、“進擊”的堆疊工藝:同時構建PMOS和NMOS晶體管

英特爾制造堆疊納米片的方案被稱為自對準過程,因為它在一步中就可以構建出兩個已經堆疊起來的晶體管,而不需要后期再將兩塊獨立的晶體管再粘合在一起。

本質上,該堆疊工藝的改變是對納米片晶體管制造步驟的修改。

首先,硅和硅鍺的重復層將會被雕刻成狹長的窄鰭形狀,然后,硅鍺層會被蝕刻,只留下一組懸浮的硅納米薄片。

通常來說,一組納米片最后會形成一個晶體管。

但在新工藝中,為了形成NMOS晶體管,頂部的兩個納米片被連接到磷摻雜的硅上;為了形成PMOS晶體管,底部的兩個納米片被連接到硼摻雜的硅鍺上。

▲由堆疊晶體管組成的反相器(圖源:英特爾)

英特爾高級研究員兼組件研究總監(jiān)Robert Chau表示,整套制作工藝當然會更加復雜,但是英特爾研究人員正努力使它盡可能簡單。

他說:“復雜的制造流程會影響到制造堆疊CMOS芯片的實用性。一旦解決了制造工藝實用性的問題,下一步就是要追求更好的性能。”

這可能將會涉及改進PMOS晶體管,因為目前他們導電效率遠低于NMOS晶體管。Robert Chau表示,如果要改進導電效率,他們會考慮通過壓縮應變或拉伸應變的方式改變晶體管溝道,使硅晶體變形,讓載流子更快通過。

結語:納米片領域,求新求變

不只是英特爾,其他許多研究機構也在尋求堆疊納米片領域的創(chuàng)新設計。

比利時研究機構Imec率先提出了CFET(納米薄片場效應晶體管)的概念,并在去年IEEE VLSI(超大規(guī)模集成電路大會)會議上報告了這一進程,但Imec的這一成果并非完全由納米片晶體管制成,它的底層是FinFET,頂層是單一納米片。臺灣研究人員也曾發(fā)表一個用于PMOS、NMOS晶體管制造的CFET結構。

英特爾的堆疊納米片晶體管技藝,會帶我們走向摩爾定律的下一步嗎?我們拭目以待。

責任編輯:PSY

-

英特爾

+關注

關注

61文章

10169瀏覽量

173957 -

摩爾定律

+關注

關注

4文章

638瀏覽量

79694 -

晶體管

+關注

關注

77文章

9979瀏覽量

140694

發(fā)布評論請先 登錄

TMD或將取代Si,下一代半導體材料來襲

鰭式場效應晶體管的原理和優(yōu)勢

低功耗熱發(fā)射極晶體管的工作原理與制備方法

電力電子中的“摩爾定律”(1)

玻璃基板在芯片封裝中的應用

AI正在對硬件互連提出“過分”要求 | Samtec于Keysight開放日深度分享

混合鍵合中的銅連接:或成摩爾定律救星

石墨烯互連技術:延續(xù)摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

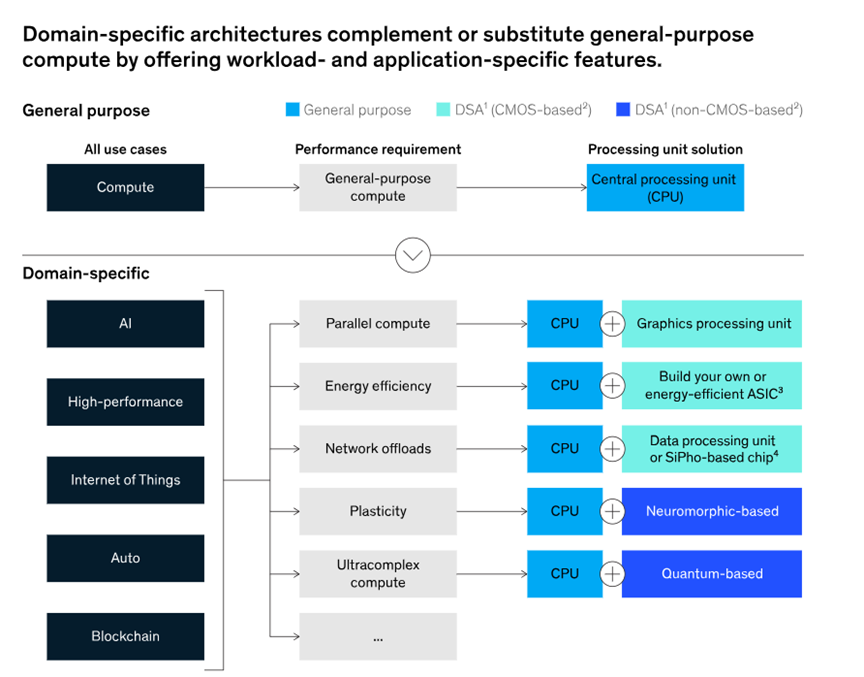

后摩爾定律時代,提升集成芯片系統(tǒng)化能力的有效途徑有哪些?

奇異摩爾專用DSA加速解決方案重塑人工智能與高性能計算

續(xù)命摩爾定律!英特爾提出晶體管密度翻倍新工藝

續(xù)命摩爾定律!英特爾提出晶體管密度翻倍新工藝

評論