比利時的獨立半導體高科技研究機構——imec每年都會在東京舉辦“imec Technology Forum(ITF) Japan”,并介紹他們的年度研發成果,今年考慮到新冠肺炎的蔓延,于11月18日在線舉行。

首先,imec的CEO兼總裁Luc Van den hove先生做了主題演講并介紹了imec的整體研究內容,并強調指出,imec通過與ASML通力合作研發并實現新一代高解析度EUV曝光技術(高NA EUV Lithography),促使摩爾定律繼續發揮作用,且即使工藝微縮化達到1納米后,摩爾定律也會繼續存在。

不僅是日本半導體企業,其他很多半導體企業也都認為“摩爾定律已經終結”、“成本高、收益低”,因此相繼放棄研發工藝的微縮化,imec始終提倡為摩爾定律續命,因此是當下全球最尖端的微縮化研究機構。

日本的曝光設備廠家也在研發階段放棄了EUV曝光技術(這對實現超微縮化是必須的),而imec和ASML合作拿公司的命運做賭注,時至今日一直在研發 。

Imec公布了1納米以后的邏輯半元件的技術藍圖

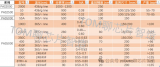

Imec在ITF Japan 2020上公布了3納米、2納米、1.5納米以及1納米及后續的邏輯元件的技術藍圖。

第一行的技術節點(Node)名下面記錄的PP為Poly-silicon排線的中心跨距(Pitch,nm),MP為金屬排線的中心跨距(Pitch,nm)。此處,我們需要注意的是,以往的技術節點指的是最小加工尺寸、柵極(Gate)的長度,如今不再指某個特定場所的物理長度,而是一個符號。

此處的展示的采用了BPR、CFET、2D材料的溝槽(Channel)結構以及材料已經在別處的演講中提及。

EUV的高NA化對于進一步實現微縮化至關重要

TSMC和三星電子從7納米開始在一部分工程中導入了NA=0.33的EUV曝光設備,也逐步在5納米工藝中導入,據說,2納米以后的超微縮工藝需要更高解析度的曝光設備、更高的NA化(NA=0.55)。

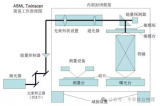

ASML已經完成了高NA EUV曝光設備的基本設計(即NXE:5000系列),預計在2022年前后實現商業化。這款新型設備由于光學方面實現了大型化,因此尺寸較大,據說可達到以往潔凈室(Clean Room)的天花板。

一直以來,ASML都和imec以合作的形式研發光刻技術,為了推進采用了高NA EUV曝光設備的光刻工藝的研發,imec在公司內新設立了“IMEC-ASML HIGH NA EUV LAB”,以共同研發,且計劃和材料廠家共同研發光掩模(Mask)、光刻膠(Resist)等材料。

最后,Van den hove先生表示未來會繼續推進微縮化:“實現邏輯元件工藝微縮化的目的在于俗稱的PPAC,即Power(功耗)的削減、Performance(電氣性能)的提高、Area(空間面積)的縮小、Cost(成本)的削減。當微縮化從3納米、2納米、1.5納米發展到1納米以后,即發展到Sub-1納米的時候,需要考慮的因素不僅是以上四項,還有環境(Environment)因素,希望未來繼續發展適用于可持續發展社會的微縮化工藝。”

責任編輯:tzh

-

半導體

+關注

關注

335文章

28627瀏覽量

232897 -

三星電子

+關注

關注

34文章

15885瀏覽量

182146 -

EUV

+關注

關注

8文章

609瀏覽量

86933

發布評論請先 登錄

電子直寫光刻機駐極體圓筒聚焦電極

成都匯陽投資關于光刻機概念大漲,后市迎來機會

不只依賴光刻機!芯片制造的五大工藝大起底!

什么是光刻機的套刻精度

半導體設備光刻機防震基座如何安裝?

如何提高光刻機的NA值

組成光刻機的各個分系統介紹

用來提高光刻機分辨率的浸潤式光刻技術介紹

光刻機的工作原理和分類

一文看懂光刻機的結構及雙工件臺技術

一文了解光刻機成像系統及光學鍍膜技術

1納米需要什么樣的光刻機?

1納米需要什么樣的光刻機?

評論