功耗是各大設計不可繞過的話題,在各大設計中,我們應當追求低功耗。為增進大家對低功耗的認識,本文將對FPGA低功耗設計予以介紹。如果你對FPGA低功耗相關內容具有興趣,不妨繼續往下閱讀哦。FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低。目前許多終端市場對可編程邏輯器件設計的低功耗要求越來越苛刻。在消費電子領域,OEM希望采用FPGA的設計能夠實現與ASIC相匹敵的低功耗。

盡管基于90nm工藝的FPGA的功耗已低于先前的130nm產品,但它仍然是整個系統功耗的主要載體。此外,如今的終端產品設計大多要求在緊湊的空間內完成,沒有更多的空間留給氣流和大的散熱器,因此熱管理、功率管理繼續成為FPGA設計的一個重要課題。采用FPGA進行低功耗設計并不是一件容易的事,盡管有許多方法可以降低功耗。FPGA的類型、IP核、系統設計、軟件算法、功耗分析工具及個人設計方法都會對產品功耗產生影響。值得注意的是,如果使用不當,有些方法反而會增加功耗,因此必須根據實際情況選擇適當的設計方法。

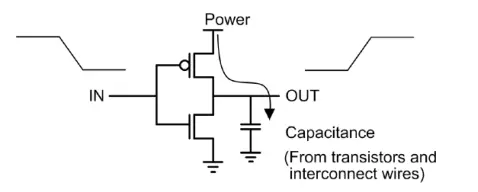

FPGA設計的總功耗包括靜態功耗和動態功耗兩個部分。其中,靜態功耗是指邏輯門沒有開關活動時的功率消耗,主要由泄漏電流造成的,隨溫度和工藝的不同而不同。靜態功耗主要取決于所選的FPGA產品。動態功耗是指邏輯門開關活動時的功率消耗,在這段時間內,電路的輸入輸出電容完成充電和放電,形成瞬間的軌到地的直通通路。與靜態功耗相比,通常有許多方法可降低動態功耗。

采用正確的結構對于設計是非常重要的,最新的FPGA是90nm的1.2 V器件,與先前產品相比可降低靜態和動態功耗,且FPGA制造商采用不同的設計技術進一步降低了功耗,平衡了成本和性能。這些90nm器件都改變了門和擴散長度,優化了所需晶體管的開關速率,采用低K值電介質工藝,不僅提高了性能還降低了寄生電容。結構的改變,如增強的邏輯單元內部互連,可實現更強大的功能,而無需更多的功耗。StraTIx II更大的改變是采用了六輸入查找表(LUT)架構,能夠通過更有效的資源利用,實現更快速、低功耗的設計。

除常規的可重配置邏輯外,FPGA正不斷集成更多的專用電路。最先進的PLD就集成了專門的乘法器、DSP模塊、可變容量RAM模塊以及閃存等,這些專用電路為FPGA提供了更加高效的功能。總體上看,采用這些模塊節約了常規邏輯資源并增加了系統執行的速度,同時可以減少系統功耗。因此更高的邏輯效率也意味著能夠實現更小的器件設計,并進一步降低靜態功耗和系統成本。

不同供應商所提供的IP內核對于低功耗所起的作用各有側重。選擇正確的內核對高效設計至關重要,有的產品將注意力集中在空間、性能和功耗的平衡上。某些供應商提供的IP內核具有多種配置(如Altera的Nios II嵌入式處理器內核采用快速、標準和經濟等三種版本),用戶可根據自己的設計進行選擇。例如,如果一個處理器在同一個存儲分區中進行多個不同調用,則采用帶板載緩存的Nios II/f就比從片外存儲器訪問數據的解決方案節約更多功耗。

如果用戶能夠從多種I/O標準中進行選擇,則低壓和無端接(nON-terminated)標準通常利于降低功耗,任何電壓的降低都會對功耗產生平方的效果。靜態功耗對于接口標準特別重要,當I/O緩沖器驅動一個高電平信號時,該I/O為外部端接電阻提供電壓源;而當其驅動低電平信號時,芯片所消耗的功率則來自外部電壓。差分I/O標準(如典型值為350 mV的低開關電壓LVDS)可提供更低的功耗、更佳的噪聲邊緣、更小的電磁干擾以及更佳的整體性能。

利用FPGA的結構來降低功耗還有賴于所使用的軟件工具。用戶可以從眾多綜合工具經銷商那里進行選擇,那些能夠使用專用模塊電路并智能地設計邏輯功能的綜合工具,將有助于用戶降低動態功耗。此外,根據自己的設計,用戶可以嘗試以面積驅動來替代時序驅動的綜合,以降低邏輯電平。不同綜合工具的選項有所差別,因此應當了解哪個“開關”或“按鈕”是必需的。

同樣重要的還有布局與布線工具,一旦用戶選擇了某種特殊的FPGA,他就必須采用該供應商的布局布線工具。由于互連會潛在地增加功耗,因而仔細進行布局規劃和設計尤為重要。即便設計不需要很快完成,設計者也希望盡可能地加快進度。諸如Altera LogicLock之類的工具所增加的設計功能可使用戶在器件定制區域內進行邏輯分組布局,因而一旦用戶找到一種高效布局,就能很快改編為他用。

為使設計消耗最小的動態功耗,可采用優化的算法來降低多余和無意義的開關活動,例如具有許多不同狀態的狀態機。一個二進制編碼的狀態機將通過觸發器產生多個比特并形成組合邏輯,采用格雷碼或One-hot編碼可降低從一個狀態到另一個狀態的開關次數。同時工程師在實現降低功耗的目標時,需要平衡格雷碼所需的額外組合邏輯,或One-hot編碼所需的附加觸發器。

數據保護和操作數隔離是另一種降低功耗的技術。在這種技術中只要沒有輸出,數據路徑算子的輸入都會保持穩定。輸入的開關行為會波及其它電路,因此即使在忽略輸出的情況下也能消耗功率,例如某個集成了基本算術邏輯單元(ALU)的設計。通過保持輸入的穩定性(停止開關),開關動作的數量就能得到減少。這種方法為每個模塊的輸入端提供了保護邏輯(觸發器和/或門電路),減少了開關動作,從而降低了系統整體的功耗。

在時鐘網絡上減少開關動作也可大幅降低功耗。多數可提供獨立全局時鐘的FPGA是分割為幾部分的,若一個設計間歇地采用部分邏輯,就可關掉其時鐘以節省功耗。最新FPGA中的PLL可禁止時鐘網絡并支持時鐘轉換,因此既可關掉時鐘也可轉換為更低頻率的時鐘。更小的邏輯部分能夠潛在地使用本地/局域時鐘來替代全局時鐘,因此不必使用不相稱的大型時鐘網絡。

對易受干擾的設計而言,減少意外的邏輯干擾可大幅降低動態功耗。意外干擾是在組合邏輯輸出時產生的暫時性邏輯轉換。減少這種效應的一個方法是重新考慮時序設計,以平衡時序關鍵路徑和非關鍵路徑間的延遲。用戶可在軟件工具的幫助下應用這種方法,例如某軟件可通過組合邏輯移動寄存器的位置,以實現平衡時序。另外一種方法是引入流水線結構,以減少組合邏輯深度,流水線還有助于增加速度。第二種方法對無意外干擾設計的效果不明顯,相反還可能增加功耗。

方便快捷的精確功率估算工具,不僅有助于設計工程師對功率進行定量評估,同時也有助于加快產品設計進度。如果在初期功率評估工具和數據表中沒有實際數據,設計工程師就不能在設計階段走得更遠。獲取初期評估數據工具,可使設計人員在設計開始之前就進行功率估算。此外作為設計規劃,工程師可將布局和布線設計加載到更精確的功率評估持續當中,從而得到一個更精準的功耗描述。最好的評估工具可使仿真文件無縫集成到電源工具中,因而能夠獲得開關功率的精確描述;若不能進行仿真,則該工具也能自動給出FPGA設計的評估參數。

fqj

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614026 -

集成電路

+關注

關注

5419文章

11945瀏覽量

367104

發布評論請先 登錄

藍牙低功耗模塊的原理和應用介紹

關于低功耗藍牙連接功耗的評估

超低功耗MCU軟件設計技巧與選型

DA14531-00000FX2 超低功耗藍牙5.1 SOC芯片介紹

低功耗處理器的優勢分析

如何實現EEPROM的低功耗模式

stm32低功耗設計技巧

物聯網系統中TCP低功耗產品長連接狀態下降低功耗功能的實現方案

柵極驅動芯片選型低功耗原因

適用于超低功耗和低功耗應用的獨特高效隔離式DC/DC轉換器

CPU的低功耗與高功耗的區別

國產藍牙模組 | 低功耗藍牙應用

什么是低功耗,對FPGA低功耗設計的介紹

什么是低功耗,對FPGA低功耗設計的介紹

評論