本篇為邏輯電平系列文章中的第一篇,主要介紹邏輯電平相關的一些基本概念。后續將會介紹常見的單端邏輯電平(針對CMOS的閂鎖效應進行詳細介紹)、差分邏輯電平、單端邏輯電平的互連、差分邏輯電平的互連、一些特殊功能的互連、邏輯互連中的電流倒灌問題、以及邏輯電平的轉換等。

1、常見邏輯電平

常見的邏輯電平如下:

- 單端:TTL、CMOS、LVTTL、LVCMOS、GTL、BTL、ETL、GTLP、SSTL2-I、SSTL2-II、SSTL3-I、SSTL3-II、HSTL-I、HSTL-II、HSTL-III、HSTL-IV、HSUL_12、POD12、POD10等;

- 差分:ECL、PECL、LVPECL、LVDS、BLVDS、LP-LVDS、CML、DIFF_HSTL、DIFF_SSTL、DIFF_HSUL、TMDS、PPDS、RSDS等。

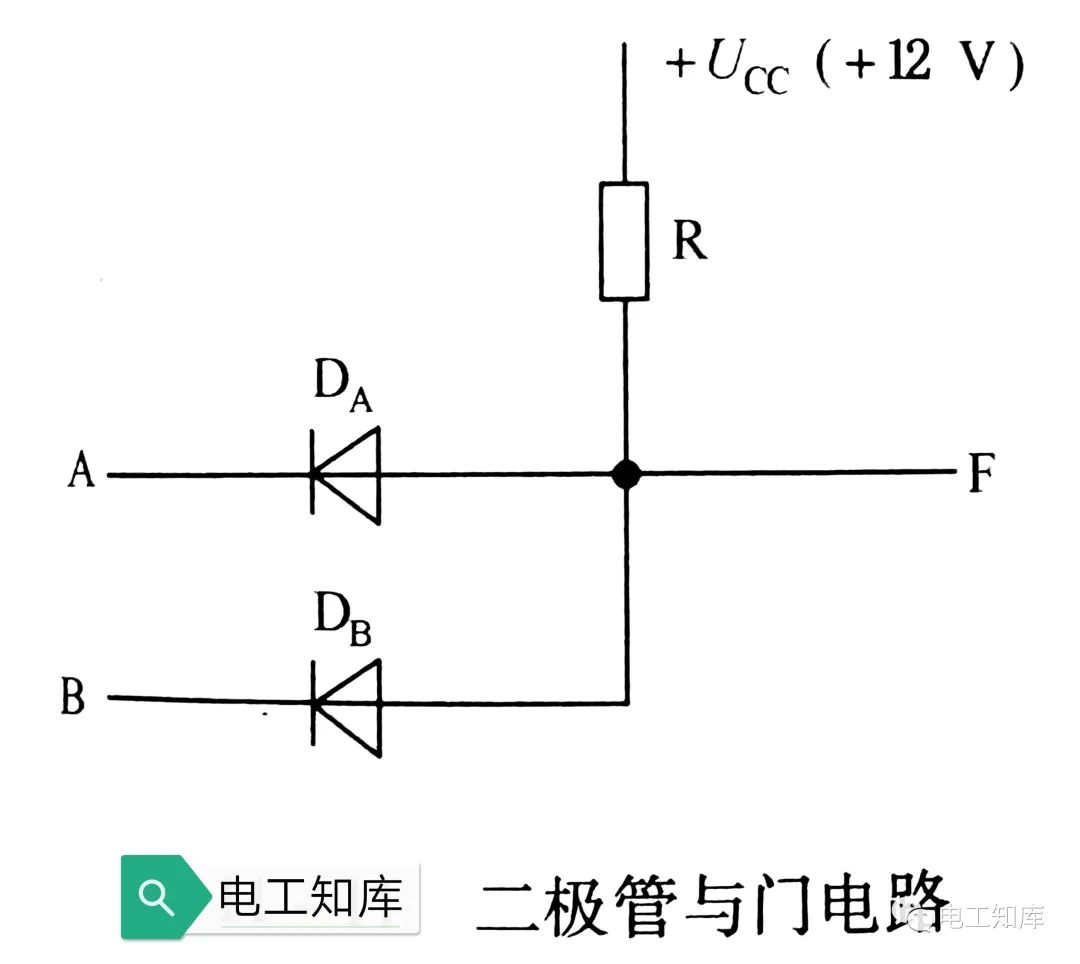

TTL邏輯輸出形式包括集電極開路輸出(OC)、三態門輸出(TSL)、復合管(達林頓管)和圖騰柱輸出。

開路的TTL、CMOS、ECL門分別稱為集電極開路(OC)、漏極開路(OD)、發射極開路(OE),使用時OC、OD門需要接阻值合適的上拉電阻,OE門需要接阻值合適的下拉電阻。

常見邏輯電平的標準如下:

- RS232:ANSI/TIA/EIA-232-F-1997

- RS422:ANSI/TIA/EIA-422-B

- RS485:ANSI/TIA/EIA-485-A

- LVTTL/LVCMOS:JESD8-5,JESD8-B

- SSTL:JESD8-8,JESD8-9B,JESD8-15

- HSTL:JESD8-6

- POD12:JESD8-24

- LVDS:ANSI/TIA/EIA 644

- SCI-LVDS:IEEE 1596.3

- MLVDS:ANSI/TIA/EIA 899-2001

2、邏輯電平的基本概念

- 輸入高電平下限(Vih):保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當輸入電平高于Vih時,則認為輸入電平為高電平。

- 輸入低電平上限(Vil):保證邏輯門的輸入為低電平時所允許的最大輸入低電平,當輸入電平低于Vil時,則認為輸入電平為低電平。

- 輸出高電平下限(Voh):保證邏輯門的輸出為高電平時的輸出電平的最小值(最小輸出高電平),邏輯門的輸出為高電平時的電平值都必須大于此Voh。

- 輸出低電平上限(Vol):保證邏輯門的輸出為低電平時的輸出電平的最大值(最大輸出低電平),邏輯門的輸出為低電平時的電平值都必須小于此Vol。

- 閥值電平(Vt):數字電路芯片都存在一個閾值電平,就是電路剛剛勉強能翻轉動作時的電平。它是一個界于Vil、Vih之間的電壓值,對于CMOS電路的閾值電平,基本上是二分之一的電源電壓值,但要保證穩定的輸出,則必須要求輸入高電平>Vih,輸入低電平<Vil。對于一般的邏輯電平,以上參數的關系如下:Voh>Vih>Vt>Vil>Vol。

- Ioh:邏輯門輸出為高電平時的負載電流(為拉電流)。

- Iol:邏輯門輸出為低電平時的負載電流(為灌電流)。

- Iih:邏輯門輸入為高電平時的電流(為灌電流)。

- Iil:邏輯門輸入為低電平時的電流(為拉電流)。

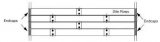

|

VCC |

Voh |

Vih |

Vt |

Vil |

Vol |

GND |

|

|

TTL(4.5~5.5V) |

5 |

2.4 |

2 |

1.5 |

0.8 |

0.4 |

|

|

CMOS(4.5~5.5V) |

5 |

4.44 |

3.5 |

2.5 |

1.5 |

0.5 |

|

|

LVTTL(3~3.6V) |

3.3 |

2.4 |

2 |

1.5 |

0.8 |

0.4 |

|

|

LVCMOS(2.7~3.6V) |

3.3 |

2.4 |

2 |

1.5 |

0.8 |

0.4 |

|

|

LVTTL(2.3~2.7V) |

2.5 |

2 |

1.7 |

1.2 |

0.7 |

0.2 |

|

|

LVCMOS(2.3~2.7V) |

2.5 |

2.3 |

1.7 |

1.2 |

0.7 |

0.2 |

|

|

LVCMOS |

1.8 |

1.35 |

1.17 |

0.9 |

0.63 |

0.2 |

|

|

LVCMOS |

1.5 |

||||||

|

LVCMOS |

1.2 |

||||||

|

LVDS(RS644) |

2.4 |

1.32 |

1.26 |

1.2 |

1.15 |

1.07 |

|

|

ECL |

-5.2 |

||||||

|

PECL |

5 |

4.12 |

3.76 |

3.7 |

3.64 |

3.28 |

|

|

LVPECL |

3.3 |

2.42 |

2.06 |

2 |

1.94 |

1.58 |

|

|

ETL(4.5~5.5V) |

5 |

2.4 |

1.6 |

1.5 |

1.4 |

0.6 |

|

|

BTL/FB |

2.1 |

1.62 |

1.55 |

1.47 |

1.1 |

1 |

|

|

GTL |

5/3.3/2.5 |

1.2 |

0.85 |

0.8 |

0.75 |

0.4 |

|

|

GTL+/GTLP |

1.5 |

1.2 |

1 |

0.8 |

0.6 |

||

|

RS232 |

5 |

3 |

0 |

-3 |

-5 |

0 |

|

|

RS422/485 |

3.3 |

1.9 |

1.8 |

1.7 |

0.3 |

3、電壓驅動和電流驅動

在傳輸線理論分析的時候,總是分析一個電壓波形的傳遞,并未考慮電流能力(驅動電流的大小),而事實上,對于高速信號來說,為了要快速響應,或者長距離傳輸,都是采用電流驅動的。

LVDS/LVPECL/CML等電平,在輸入端都有匹配電阻(50/100歐姆),這些電阻對于輸入門來說承擔的是把電流轉換成電壓的任務。因為對于一個輸入邏輯門來說,它對電流的需求并不大,它需要的是足夠的電壓幅度。既然芯片需要的是電壓幅度,為何輸出端不直接把電壓傳遞過來呢。那是因為電壓傳遞速度比較慢,并且容易受到干擾。而電流驅動反應速度快,抗干擾能力強。

電流驅動型鏈路,在接收端都有一個電流轉成電壓的電路(這個電路同時也承擔著匹配的任務)。

大家可以理解一下TTL/CMOS電路,如果驅動能力比較弱的話,信號的上升沿和下降沿就會很緩,能傳的頻率就會很低。雖然單端信號如TTL/CMOS信號的頻率特性與驅動電流有關,但還是應該稱這類的信號為電壓驅動類型的信號。

4、扇入扇出系數

扇入系數,是指門電路允許的輸入端數目。一般TTL電路的扇入系數Nr為1~5,最多不超過8。若芯片輸入端數多于實際要求的數目,可將芯片多余輸入端接高電平(VCC)或接低電平(GND)。

扇出系數,是指一個門的輸出端所能驅動同類型門的個數,或稱負載能力。Nc=IOLMAX/IILMAX,這是一個通俗的定義,一般用在TTL電路的定義中。其中IOLMAX為最大允許灌電流,IILMAX是一個負載門灌入本級的電流。

TTL電路的扇出系數Nc為8~10。

IOL/IOH是測試芯片的扇出能力,IOL是測試灌電流,IOH是測試拉電流。對于IOH,在外面的負載增加的情況下,肯定會引起VOH降低,所以負載的個數是有限的(因為必須保證輸出電壓大于VOH)。也就是說IOH、IOL測量的是芯片輸出buffer的內阻大小(芯片輸出管腳跟普通的電源一樣,它的內阻大小決定了芯片的驅動能力。內阻越小則IOH越大,外接負載時,負載對輸出高電平的影響越小,驅動能力越大;內阻越大,接入負載后,在負載上的分壓就小,當小于VOH時驅動能力就不能滿足要求了)。器件的扇出能力主要取決于器件的輸出阻抗,及電源電壓和電平規格。

IOL/IOH應該是越大越好,因為越大,該管腳驅動能力就越強,能驅動的管腳數目也越多(扇出系數)。但對于設計來說,IOL/IOH越大,需要輸出級導通電阻做的更小,那就要使管子的寬長比(W/L)足夠大,L制約于工藝的特征尺寸,只能再增加W,這樣會使芯片的面積增大造成成本增加,所以對于IOL/IOH需要的是合適值而非最大值。

編輯:hfy

-

CMOS

+關注

關注

58文章

5991瀏覽量

238074 -

邏輯電平

+關注

關注

0文章

184瀏覽量

14697 -

電流驅動

+關注

關注

1文章

46瀏覽量

11011 -

電壓驅動

+關注

關注

1文章

31瀏覽量

4339

發布評論請先 登錄

邏輯門電路基本概念介紹

線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間的基本概念

邏輯電平詳細介紹

數字后端基本概念介紹

常見邏輯電平介紹和基本概念

常見邏輯電平介紹和基本概念

評論