1. CvP 簡介

CvP(Configuration via Protocol)是一種通過協(xié)議實(shí)現(xiàn) FPGA 配置的方案,Arria? V,Cyclone? V,Stratix? V,Arria? 10,Cyclone? 10 GX,Stratix? 10,Agilex?都支持這個(gè)功能,但支持的模式有所差異。目前所采用的協(xié)議是 PCI Express? (PCIe)。

CvP 配置文件被拆分成兩個(gè),一個(gè)是 periphery image,一個(gè)是 core image。

?Periphery image (*.periph.jic) 包含 GPIOs,I/Oregisters,GCLK、QCLK、RCLK 時(shí)鐘網(wǎng)絡(luò),PLLs,收發(fā)器,存儲(chǔ)器 PHY 接口,以及硬核 IP,例如?PCIe 硬核。這部分不能被更改和更新。Periphery image 存儲(chǔ)在?FPGA 配置芯片內(nèi),上電加載。

?Core image (*.core.rbf) 包含被 configuration RAM (CRAM)配置的邏輯部分,包括 LABs, DSP, 和 embedded memory。FPGA?設(shè)備上電后主機(jī)端再經(jīng)由所用的協(xié)議(此處為 PCIe)將 core image 下載并配置到 FPGA 內(nèi)部。

2. CvP 系統(tǒng)結(jié)構(gòu)

CvP 系統(tǒng)由三部分組成:FPGA,PCIehost,F(xiàn)PGA 的配置器件。如圖 1。

圖 1 CvP 系統(tǒng)結(jié)構(gòu)圖

(1)配置器件與 FPGA 通過傳統(tǒng)配置接口互聯(lián)。對于 V 系列和 Arria10 器件來說,可支持任何配置方式,例如 AS,PS 或 FPP。針對 Stratix10,可采用 Active Serial x4 (fast mode) 或 Avalon Streaming (Avalon-ST) x8。對于 Agilex 系列器件,只可采用 Active Serial x4 (fast mode)。

(2)對于 V 系列、Arria10、Stratix10、Cyclone10GX,只有器件底部左側(cè)的 PCIe?硬核才支持 CvP 功能,其他的 PCIe 硬核可作常規(guī)功能使用。而對于 Agilex 系列,左側(cè)的 PCIe 硬核都支持 CvP 功能。在硬件設(shè)計(jì)階段需要確認(rèn)使用哪個(gè) PCIe 做 CvP,一旦確定,則只有這個(gè) PCIe 硬核作為 Endpoint 可以使能 CvP 功能,其他 PCIe 硬核不能再作此用途,但可作為常規(guī) PCIe 接口用。

(3)其他 PCIe 硬核能作為常規(guī) PCIe 接口使用。

3. CvP 價(jià)值

? 由于只需要存儲(chǔ) periphery logic,F(xiàn)PGA 的配置器件可以選擇小容量器件,降低成本。

? Coreimage 存在主機(jī)端,提高核心邏輯的安全性。

? 對于支持 CvP Update Mode 的器件來說,可支持動(dòng)態(tài)的核心邏輯更新,而不需要系統(tǒng)斷電重啟。

? 主機(jī)側(cè)提供了簡單的軟件配置模型。

4. CvP 模式

CvP 有兩種模式:CvP Initialization mode 和 CvP Update mode。

4.1 CvP Initialization Mode 初始化模式

FPGA 在上電時(shí)加載配置芯片上的 peripheral image,在 100ms 的枚舉時(shí)間內(nèi)成功配置其 PCIe 接口,使主機(jī)能正確枚舉該 PCIe 設(shè)備。主機(jī)啟動(dòng)后再通過 PCIe 鏈路配置 FPGA 核心邏輯。

CvP Initialization Mode 優(yōu)勢:

? 保證 FPGA PCIe 設(shè)備滿足枚舉時(shí)間。

? FPGA 的配置器件可以選擇小容量器件,降低成本。

? 保證主機(jī)側(cè)核心邏輯的安全性。

4.2 CvP Update Mode 更新模式

當(dāng) FPGA 進(jìn)入用戶模式,對除 CvP PCIe 核之外的其他邏輯通過 CvP 進(jìn)行重新配置,此時(shí) CvP PCIe 既可以做常規(guī) PCIe 使用,又可以實(shí)現(xiàn) FPGA 核心邏輯的更新。為使用該模式,需要參考 Partition 的流程對工程進(jìn)行分模塊 Partition 和 Logic Lock 設(shè)計(jì),以重復(fù)利用設(shè)備外設(shè),保證 peripheral image 不變。

當(dāng)有以下幾種需要時(shí),可以考慮使用該模式:

? 需要對核心邏輯進(jìn)行更新。

? 根據(jù)功能發(fā)布情況對設(shè)備進(jìn)行更新。

4.3 不同器件系列支持的模式

前面說到 ArriaV,CycloneV,StratixV,Arria10,Cyclone10GX,Stratix10,Agilex 都支持 CvP,但不同系列器件支持的模式有所差異,具體如表 1,其中 Agilex 只支持 InitializationMode,如表 2。

表 1 不同器件系列支持的模式

表 2 Agilex 系列支持的模式

5. CvP Initialization mode 實(shí)現(xiàn)流程和注意事項(xiàng)

使用 Stratix V 開發(fā)板實(shí)現(xiàn) CvP Initialization mode 的流程及注意事項(xiàng)。

? 板卡:Stratix-VGX Dev Kit (PCIe board),PCIe Gen1x8。

? 主機(jī):64 位 Windows7 操作系統(tǒng)。

? Quartus 版本:QuartusII 64-Bit Version 14.1.0 Build 186

5.1 實(shí)現(xiàn)流程

1. 構(gòu)建含 PCIe IP 的工程,此處采用 S5PCIe 的 Example design。

2. 打開工程內(nèi) PCIe IP 的 GUI,勾選“Enable configuration via the PCIe link”。

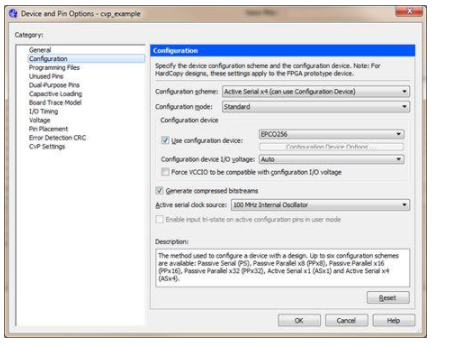

3. 在 Assignments =》 Device =》 Device andPin Options =》 Configuration 中選擇 FPGA 的配置模式為 Active Serial x4(并設(shè)置 MSEL)。

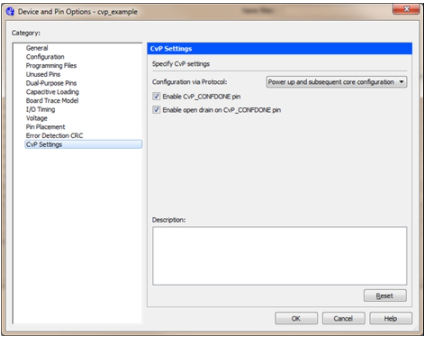

在 Assignments =》 Device =》 Device and Pin Options =》 CvPSettings 選擇 configuration via protocol 為 Core initialization。

4. 根據(jù)開發(fā)板分配管腳并編譯工程,生成 cvp_example.sof。

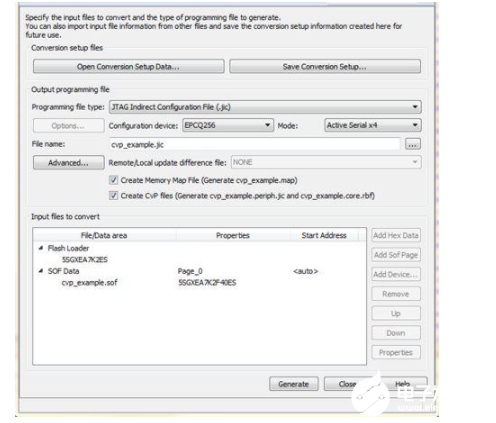

5. 將生成的 cvp_example.sof 進(jìn)行拆分,打開 File =》 Convert Programming Files,設(shè)置 Programmingfile type 為 JTAG Indirect Configuration File (.jic)。添加 cvp_example.sof,勾選 Create Memory Map File 和 Create CvP files。點(diǎn)擊 Generate 之后,cvp_example.sof 就被拆分成兩部分,cvp_example.periph.jic 和 cvp_example.core.rbf。

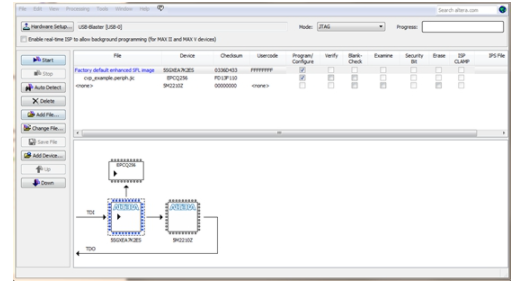

6. 關(guān)閉主機(jī),將 PCIE 板卡連上 JTAG,插在主機(jī) PCIe 插槽里,主機(jī)再上電啟動(dòng)。此時(shí) PCIE 板卡由 PCIE 插槽供電。打開 Quartus II Programmer,點(diǎn)擊 Auto Detect 掃描 JTAG 鏈,選擇 FPGA 點(diǎn)擊 ChangeFile,選擇之前生成的 cvp_example.periph.jic 文件,并燒寫進(jìn) EPCQ256。

7. 重新啟動(dòng)主機(jī),枚舉 PCIe 設(shè)備。此時(shí)已經(jīng)加載了 cvp_example.periph.jic 的 PCIE 板卡將作為 PCIE 設(shè)備被系統(tǒng)識(shí)別。根據(jù) PCIe IP 的設(shè)置,在主機(jī)側(cè)查看 DeviceID 為 E001,Vendor ID 為 1172 的 PCIe 設(shè)備。

此時(shí)可以下載一個(gè)免費(fèi)軟件“RW – Read & Write Utility”。找到 Device ID 為 E001,Vendor ID 為 1172 的 PCIe 設(shè)備。

8. 在主機(jī)上使用 quartus_cvp 對識(shí)別到的 PCIe 板卡(Device ID 為 E001,VendorID 為 1172)加載核心邏輯部分 cvp_example.core.rbf。打開 Windows CMD,更改路徑到 cvp_example.core.rbf 所在的位置。

輸入如下命令并回車:

? quartus_cvp--vid=1172 --did=e001 cvp_example.core.rbf

如果成功執(zhí)行該命令,會(huì)出現(xiàn)如下界面,表示核心邏輯已被成功加載進(jìn) FPGA,此時(shí) FPGA 進(jìn)入 usermode,可以正確工作。

5.2 注意事項(xiàng)

運(yùn)行 quartus_cvp 時(shí)需要安裝 Jungo WinDriver。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1643文章

21956瀏覽量

614016 -

PCIe

+關(guān)注

關(guān)注

16文章

1322瀏覽量

84667

發(fā)布評論請先 登錄

nvme IP開發(fā)之PCIe下

nvme IP開發(fā)之PCIe上

NVMe協(xié)議簡要分析

FPGA芯片的概念和結(jié)構(gòu)

【高清視頻案例分享】CameraLink接口的PCIe采集卡 ,基于FPGA開發(fā)平臺(tái)

PROFINET通訊協(xié)議報(bào)文解析

基于FPGA的GigE Vision相機(jī)圖像采集方案設(shè)計(jì)

AUTOSAR通信協(xié)議解析 如何實(shí)現(xiàn)AUTOSAR通信

PCIe數(shù)據(jù)傳輸協(xié)議詳解

如何選擇適合的PCIe配置

固化FPGA配置芯片的方式

請問有DS26334芯片的中文資料,和相關(guān)配置的源代碼嗎?以及相關(guān)的傳輸協(xié)議解析。

plc協(xié)議解析網(wǎng)關(guān)是什么

FPGA的SRIO接口使用應(yīng)注意的事項(xiàng)

Modbus協(xié)議轉(zhuǎn)Profinet協(xié)議網(wǎng)關(guān)與氣體監(jiān)測系統(tǒng)配置案例

CvP系統(tǒng)結(jié)構(gòu)解析 PCIE協(xié)議實(shí)現(xiàn)FPGA 配置案例

CvP系統(tǒng)結(jié)構(gòu)解析 PCIE協(xié)議實(shí)現(xiàn)FPGA 配置案例

評論