文章來源:老虎說芯

原文作者:老虎說芯

本文介紹了現(xiàn)場可編程門陣列的基本結(jié)構(gòu)、優(yōu)勢和在工程應(yīng)用上的意義。

一、FPGA芯片概念

FPGA(Field Programmable Gate Array,現(xiàn)場可編程門陣列),是一種可在出廠后由用戶根據(jù)實際需求進行編程配置的集成電路。與專用集成電路(如ASIC)不同,F(xiàn)PGA在硬件層面具備高度的可重構(gòu)性,能夠靈活實現(xiàn)各類數(shù)字邏輯電路和復(fù)雜系統(tǒng)方案。

二、FPGA的基本結(jié)構(gòu)

1、可編程邏輯單元(CLB/ALM/SLICE等)

這是實現(xiàn)邏輯功能的核心模塊,每個單元由查找表(LUT)、觸發(fā)器等組成,用于構(gòu)建基本的邏輯門、加法器、寄存器等。

2、可編程互連網(wǎng)絡(luò)

負責(zé)將各邏輯單元、存儲器、I/O等資源自由連接,支持高速、復(fù)雜的數(shù)據(jù)流動,靈活實現(xiàn)多種連線拓撲。

3、存儲資源(如Block RAM、SRAM等)

提供片上緩存、FIFO、圖像行緩沖等,滿足數(shù)據(jù)暫存與快速訪問需求。

4、時鐘管理與分布資源(PLL、CLK網(wǎng)等)

實現(xiàn)系統(tǒng)多頻率、多相位的時鐘生成與分發(fā),保證系統(tǒng)同步和時序可靠。

5、專用硬核單元(例如乘法器、DSP、嵌入式CPU、收發(fā)器等)

用以加速數(shù)值運算、信號處理、數(shù)據(jù)通信等高性能或?qū)S脠鼍啊?/p>

6、豐富的I/O接口資源

支持多種電平標準及差分/單端通信協(xié)議,實現(xiàn)與外部世界的數(shù)據(jù)交換。

三、FPGA的典型工作流程

1、硬件描述與設(shè)計(如VHDL/Verilog建模)

2、仿真驗證功能與時序

3、邏輯綜合和布局布線

4、生成比特流文件并配置到FPGA內(nèi)

5、上電/下載完成后,F(xiàn)PGA即按照用戶編寫的電路邏輯工作

這種完全由用戶定義硬件功能的方式,使FPGA成為電子設(shè)計中的“定制平臺”。

四、FPGA與其它集成電路的對比優(yōu)勢

1、與CPU/DSP(通用處理器)相比,F(xiàn)PGA并行數(shù)據(jù)處理能力更強,適合實現(xiàn)高吞吐、低時延任務(wù)。

2、與ASIC相比,F(xiàn)PGA可反復(fù)重構(gòu),實現(xiàn)靈活試錯和快速迭代,顯著降低前期開發(fā)風(fēng)險和成本。

3、可作為特殊算法加速引擎、通信協(xié)議處理器、片上系統(tǒng)(SoC)等高性能定制場合的可靠硬件基礎(chǔ)。

五、FPGA的工程意義

1、快速驗證與原型開發(fā)

提高新技術(shù)研發(fā)效率,縮短產(chǎn)品上市周期,是硬件設(shè)計的“實驗田”。

2、高度并行與多樣化功能實現(xiàn)

滿足圖像信號處理、通信、人工智能、工業(yè)控制等高性能復(fù)雜場景的多元需求。

3、可持續(xù)升級與維護

支持遠程在線升級,適配系統(tǒng)功能變化,為產(chǎn)品生命周期管理提供便利。

4、系統(tǒng)集成度高

具備內(nèi)嵌處理器、專用IP核等資源,可實現(xiàn)單芯片多功能系統(tǒng),推動電子設(shè)備的小型化與高集成。

六、總結(jié)

FPGA芯片是現(xiàn)代電子系統(tǒng)中極具戰(zhàn)略意義的可編程硬件平臺,兼具靈活性、并行性和高可定制化,廣泛應(yīng)用于前沿科研、工業(yè)控制、嵌入式系統(tǒng)、人工智能和通信等領(lǐng)域。其與晶圓工藝、封裝技術(shù)一起,共同推動集成電路行業(yè)的快速創(chuàng)新發(fā)展。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21966瀏覽量

614151 -

芯片

+關(guān)注

關(guān)注

459文章

52192瀏覽量

436260 -

集成電路

+關(guān)注

關(guān)注

5420文章

11954瀏覽量

367175

原文標題:FPGA芯片的概念、基本結(jié)構(gòu)和優(yōu)勢

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

從發(fā)明到 AI 加速:慶祝 FPGA 創(chuàng)新 40 周年

FPGA的定義和基本結(jié)構(gòu)

fpga和cpu的區(qū)別 芯片是gpu還是CPU

FPGA驅(qū)動AD芯片之實現(xiàn)與芯片通信

采用AFE0064和ADS8363加fpga結(jié)構(gòu),如何進行控制?

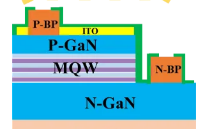

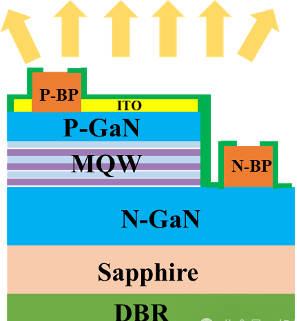

LED芯片:三種核心結(jié)構(gòu)解析

詳解FPGA的基本結(jié)構(gòu)

固化FPGA配置芯片的方式

FPGA無芯片怎么進行HDMI信號輸入

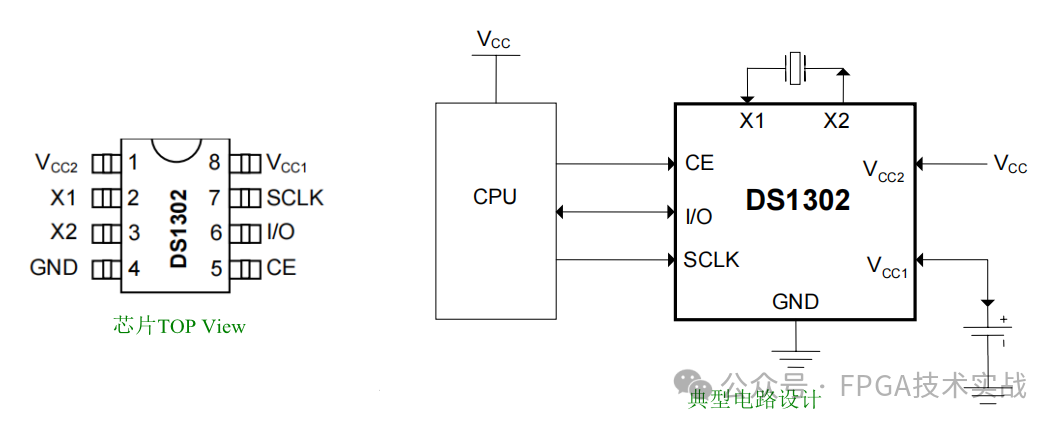

DS1302芯片與FPGA之間SPI通信原理

LDO芯片的拓撲結(jié)構(gòu)

LED芯片的三種封裝結(jié)構(gòu)

一文了解FPGA技術(shù)知識

FPGA芯片的概念和結(jié)構(gòu)

FPGA芯片的概念和結(jié)構(gòu)

評論