.coe格式的數(shù)據(jù)文件簡(jiǎn)介

在Vivado中,對(duì)rom進(jìn)行初始化的文件是.coe文件.它的格式如下:

memory_initialization_radix=10; memory_initialization_vector = 65534, 65533, ..., 60211;

其中,memory_initialization_radix=10; 表示文件存儲(chǔ)數(shù)據(jù)的進(jìn)制,10即為10進(jìn)制,memory_initialization_vector是數(shù)據(jù)向量,等號(hào)后面的數(shù)字就是數(shù)據(jù)向量,使用逗號(hào)隔開(kāi)數(shù)據(jù),分毫表示結(jié)束。

小結(jié):

① .coe文件的前兩行的開(kāi)頭格式是固定的,不能改變的

② 所存儲(chǔ)的數(shù)據(jù)數(shù)量與大小是與設(shè)計(jì)rom的位寬和深度相對(duì)應(yīng)的

使用matlab生成.coe文件

以下面的程序?yàn)槔菔玖松晌粚挒?6bit,深度為1024的rom生成初始化文件:

width=16; %rom的位寬 depth=1024; %rom的深度 x=linspace(0,2*pi,depth); %在一個(gè)周期內(nèi)產(chǎn)生1024個(gè)采樣點(diǎn) y_cos=cos(x); %生成余弦數(shù)據(jù) y_cos=round(y_cos*(2^(width-1)-1))+2^(width-1)-1; %將余弦數(shù)據(jù)全部轉(zhuǎn)換為整數(shù) fid=fopen('C:/Users/Administrator/Desktop/cos_coe.coe','w'); %創(chuàng)建.coe文件 fprintf(fid,'%d,/n',y_cos); %向.coe文件中寫(xiě)入數(shù)據(jù) fclose(fid); %關(guān)閉.coe文件

注意,windows中換行符可能是/r/n

再編輯.coe文件,推薦使用notepad++打開(kāi),并:

① 在前兩行添加:

memory_initialization_radix=10; memory_initialization_vector =

② 將最后一行的逗號(hào)改為分號(hào).

Vivado中ROM IP核的使用

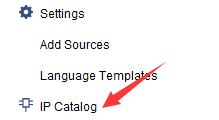

① 在project manager選擇IP Catalog:

② 找到Block Memory Generator,并雙擊:

③ 在下面的界面中進(jìn)行ROM的設(shè)置,在Other Options欄中設(shè)置剛剛設(shè)置好的.coe文件的位置,推薦將該文件放在工程目錄下面。并點(diǎn)擊OK,即可完成ROM的設(shè)置,成功會(huì)的結(jié)果如下所示:

④ 完成上面的操作之后可以在工程文件中調(diào)用該ROM IP核,調(diào)用的方式是在IP Source中打開(kāi)所生成的ROM IP核,再打開(kāi)*.v文件,如下圖所示:

復(fù)制該文件中的調(diào)用語(yǔ)句:

module rom_data_i(clka, addra, douta) /* synthesis syn_black_box black_box_pad_pin="clka,addra[16:0],douta[15:0]" */; input clka; input [16:0]addra; output [15:0]douta; endmodule

模仿該格式就可以調(diào)用IP核。

編輯:hfy

-

ROM

+關(guān)注

關(guān)注

4文章

578瀏覽量

86976 -

存儲(chǔ)數(shù)據(jù)

+關(guān)注

關(guān)注

0文章

89瀏覽量

14280 -

Vivado

+關(guān)注

關(guān)注

19文章

828瀏覽量

68186

發(fā)布評(píng)論請(qǐng)先 登錄

vivado IP核cordic中sin和cos的計(jì)算

在Vivado調(diào)用MIG產(chǎn)生DDR3的問(wèn)題解析

一文詳解Video In to AXI4-Stream IP核

Vivado FIR IP核實(shí)現(xiàn)

基于FPGA的圖像邊緣檢測(cè)設(shè)計(jì)

XADC IP核介紹

ALINX發(fā)布100G以太網(wǎng)UDP/IP協(xié)議棧IP核

AMD Vivado Design Suite 2024.2全新推出

vivado導(dǎo)入舊版本的項(xiàng)目,IP核心被鎖。

芯驛電子 ALINX 推出全新 IP 核產(chǎn)品線,覆蓋 TCP/UDP/NVMe AXI IP 核

芯驛電子ALINX推出全新IP核產(chǎn)品線

Xilinx DDS IP核的使用和參數(shù)配置

如何申請(qǐng)xilinx IP核的license

Vivado 如何調(diào)用ROM IP核

Vivado 如何調(diào)用ROM IP核

評(píng)論