IP核概述

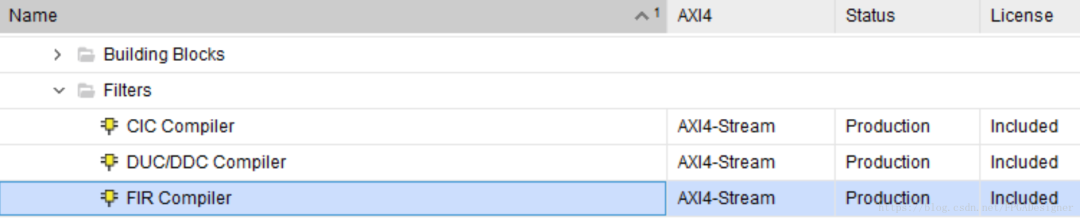

Xilinx的FIR IP核屬于收費(fèi)IP,但是不需要像 Quartus那樣通過(guò)修改license文件來(lái)破解。如果是個(gè)人學(xué)習(xí),現(xiàn)在網(wǎng)絡(luò)上流傳的license破解文件在破解Vivado的同時(shí)也破解了絕大多數(shù)可以破解的IP核。只要在IP Catalog界面中FIR Compiler的License狀態(tài)為“Included”即可正常使用。

IP核參數(shù)設(shè)置

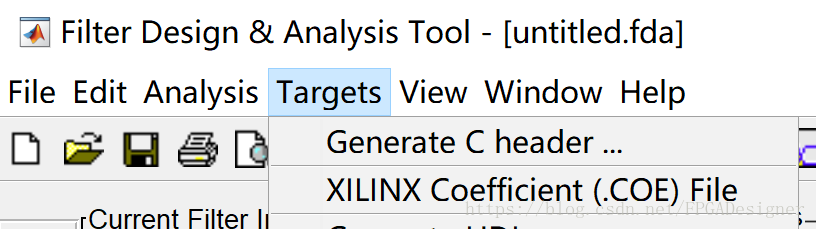

和Quartus不一樣,Vivado的FIR Compiler沒(méi)有提供設(shè)計(jì)FIR濾波器和生成濾波器系數(shù)的功能,因此需要使用MATLAB等其它工具設(shè)計(jì)好濾波器再將系數(shù)導(dǎo)入到IP核中。MATLAB的FDATOOL工具在設(shè)計(jì)好濾波器后,可以直接生成IP核需要的coe文件,如下圖所示:

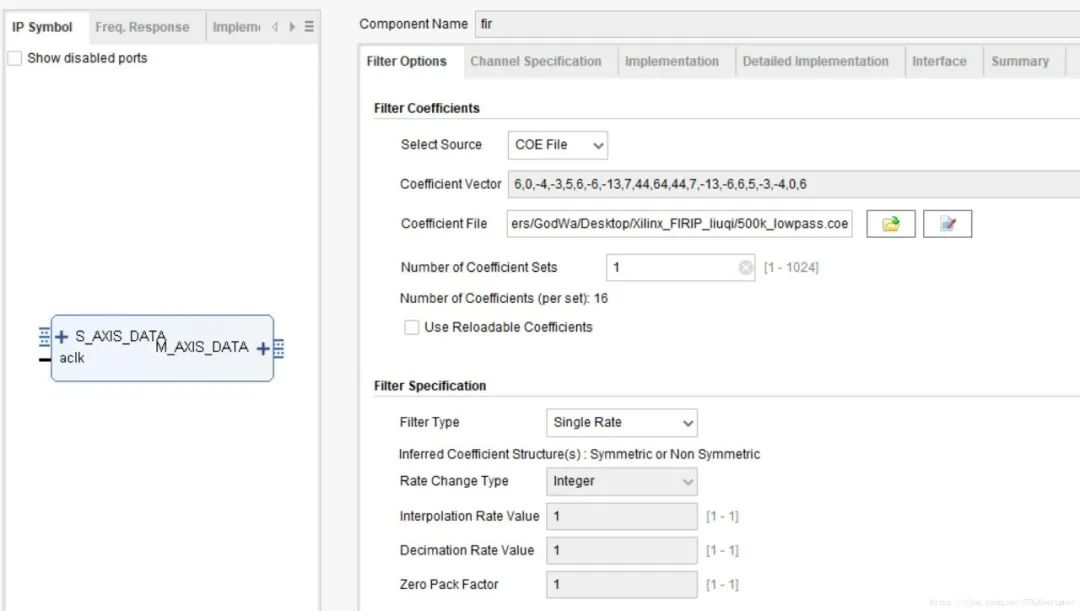

在IP Catalog中打開(kāi)FIR Compiler,主界面如下:

左邊的Tab可以切換看到FIR的模塊圖(管腳信息)、頻率響應(yīng)等信息。右邊的Tab是對(duì)FIR濾波器進(jìn)行設(shè)計(jì)。

IP核支持兩種FIR系數(shù)輸入方式,以“Vector”的形式直接寫(xiě)入;或者以“COE File”的形式導(dǎo)入coe文件。Xilinx的FIR IP核支持多種濾波器結(jié)構(gòu),可以在“Filter Type”中設(shè)置,本文選擇傳統(tǒng)的“Single Rate”結(jié)構(gòu)。該IP核同樣也支持系數(shù)重載。

除了單速率(Single Rate,即數(shù)據(jù)輸出與輸入速率相同)外,F(xiàn)IR Compiler還支持抽取(Decimation)和插值(Interpolation)應(yīng)用于多速率信號(hào)處理系統(tǒng)。此外還支持希爾伯特變換(Hilbert)模式,可以在“Filter Type”中設(shè)置。

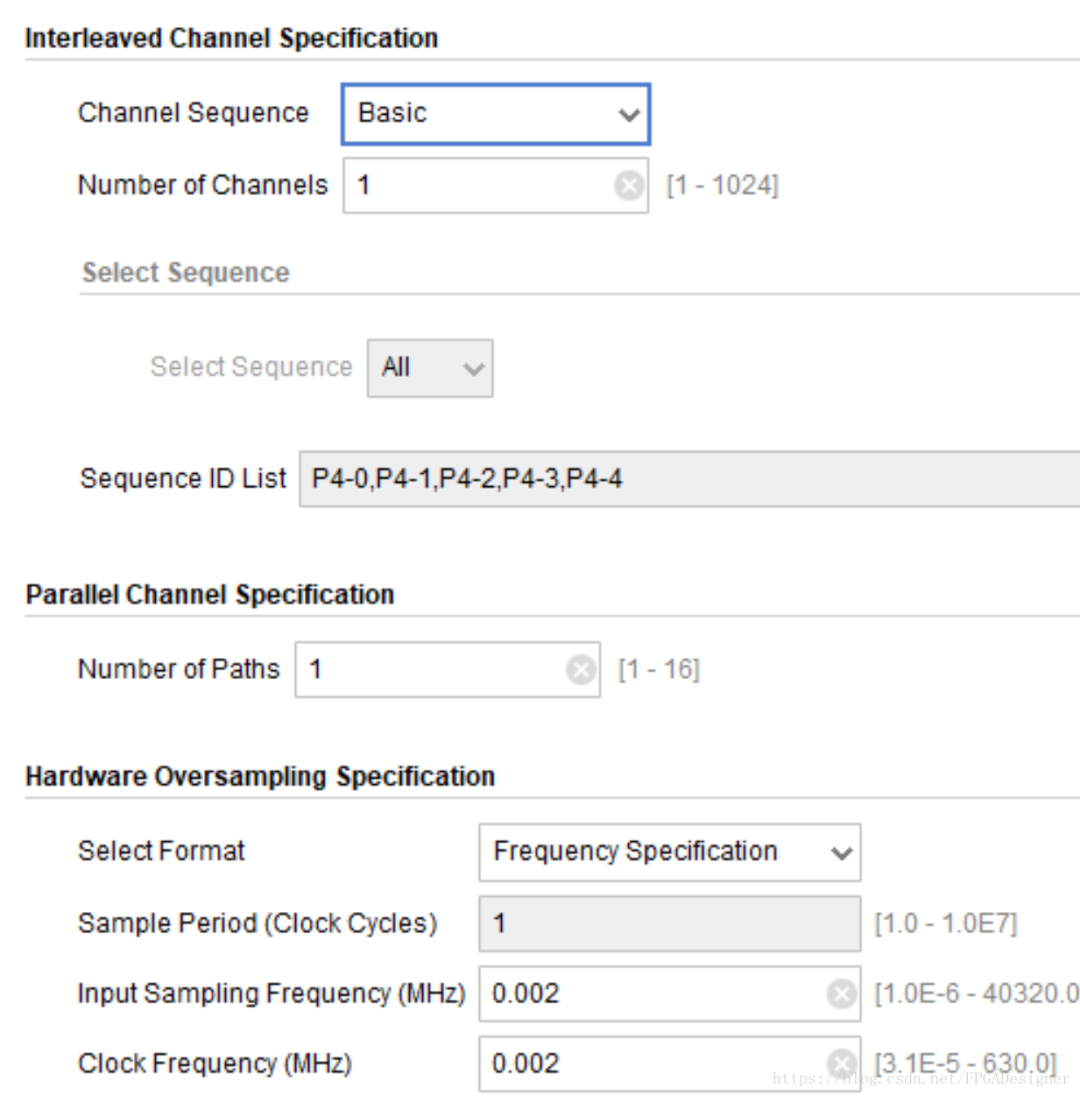

IP核支持多通道數(shù)據(jù)輸入,可以在Channel Specification這個(gè)Tab中設(shè)置輸入數(shù)據(jù)的通道數(shù)。還可以在Hardware Oversampling Specification中設(shè)置過(guò)采樣模式,即輸入數(shù)據(jù)的頻率可以高出FIR系統(tǒng)時(shí)鐘的頻率。

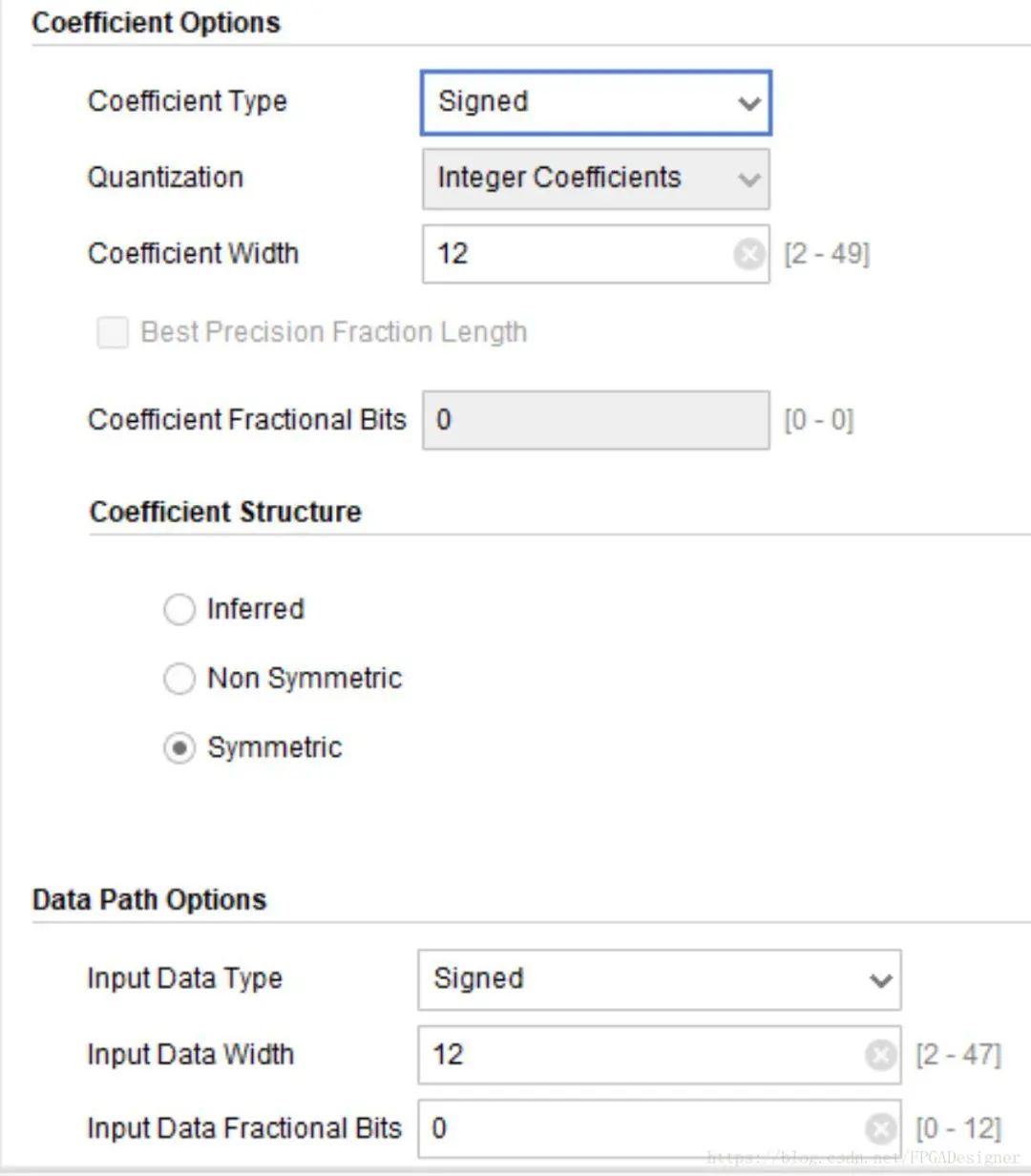

Implementation這個(gè)Tab中可以設(shè)置FIR系數(shù)的類(lèi)型、量化方式、量化位寬(此值應(yīng)該與MATLAB中的設(shè)置一致,否則頻率響應(yīng)是錯(cuò)的)和結(jié)構(gòu)。本文由于是設(shè)計(jì)線性相位FIR,濾波器系數(shù)是對(duì)稱(chēng)的,因此選擇為“Symmetric”,也可以選擇為“Inferred”,軟件會(huì)自動(dòng)判斷系數(shù)的結(jié)構(gòu)。

Detailed Implementation這個(gè)Tab中可以設(shè)置優(yōu)化方式、存儲(chǔ)的類(lèi)型、是否使用DSP單元等與綜合、實(shí)現(xiàn)有關(guān)的信息。Interface這個(gè)Tab中可以設(shè)置與IP核接口相關(guān)的信息。

IP核接口說(shuō)明

Vivado的很多IP核采用的是AXI4接口,主要有數(shù)據(jù)(tdata)、準(zhǔn)備好(tready)、有效(tvalid)幾種信號(hào),還有主機(jī)(m)和從機(jī)(s)之分。另外在Interface這個(gè)Tab還可以配置使用更多輔助的AXI4接口信號(hào)。

接下來(lái)介紹幾個(gè)主要的接口:

在設(shè)置為多通道、可變系數(shù)模式時(shí),還會(huì)用到其它的接口。上表中的接口已經(jīng)足夠完成一次單通道、固定系數(shù)的FIR濾波器設(shè)計(jì)。其它接口在后文的設(shè)計(jì)中使用到FIR濾波器的其它模式時(shí),再做介紹。

需要注意,同DDS Compiler一樣(https://blog.csdn.net/fpgadesigner/article/details/80512067),AXI4接口的tdata位寬是以字節(jié)為單位,即只會(huì)是8的倍數(shù),因此需要結(jié)合設(shè)計(jì)的實(shí)際位寬做相應(yīng)處理。

FPGA設(shè)計(jì)

IP核的接口在Verilog HDL中進(jìn)行設(shè)計(jì)時(shí),一定要參考官方文檔中給出的時(shí)序圖。在IP核的配置界面點(diǎn)擊“documentation”,可以找到IP核的user guide。也可以在Xilinx官網(wǎng)或DocNav工具中搜索pg149,查閱FIR Compiler的說(shuō)明。

單通道、固定系數(shù)的FIR Compiler接口時(shí)序非常簡(jiǎn)單,Verilog HDL示例代碼如下所示:

`timescale 1ns / 1ps

module Xilinx_FIRIP_liuqi

(

input clk, //FPGA系統(tǒng)時(shí)鐘/數(shù)據(jù)速率:2kHz

inputsigned [11:0] Xin, //數(shù)據(jù)輸入頻率為2kHZ

outputm_tvalid, //FIR輸出數(shù)據(jù)有效信號(hào)

outputsigned [24:0] Yout //濾波后的輸出數(shù)據(jù)

);

wire s_tready;

wire signed [31:0] m_tdata;

fir fir_lowpass_500kHz

(

.aclk (clk),

.s_axis_data_tvalid (1'b1),

.s_axis_data_tready (s_tready),

.s_axis_data_tdata ({{4{Xin[11]}},Xin}),

.m_axis_data_tvalid (m_tvalid),

.m_axis_data_tdata (m_tdata)

);

assign Yout = m_tdata[24:0];

endmodule

程序中認(rèn)為輸入的采樣數(shù)據(jù)始終有效,因此將s_axis_data_tvalid永遠(yuǎn)置1。由于s_axis_data_tdata為16bit位寬,但輸入信號(hào)數(shù)據(jù)為12bit位寬,因此用拼接運(yùn)算符{}在高位填充補(bǔ)碼的符號(hào)位;由于m_axis_data_tdata為32bit位寬,但輸出信號(hào)數(shù)據(jù)有效位僅有25bit位寬,因此僅需取低25bit作為FIR濾波器輸出。當(dāng)然不這么操作,直接將信號(hào)賦值到實(shí)例化接口,結(jié)果也是正確的,這樣做只是為了更嚴(yán)謹(jǐn)。

仿真與工程下載

使用MATLAB生成一個(gè)200khz+800kHz的混合頻率信號(hào),寫(xiě)入txt文件,。編寫(xiě)Testbench讀取txt文件對(duì)信號(hào)濾波,文件操作方法參考“Testbench編寫(xiě)指南(一)文件的讀寫(xiě)操作”https://blog.csdn.net/fpgadesigner/article/details/80470972。

在Vivado中進(jìn)行仿真,對(duì)正弦信號(hào)的濾波如下圖所示:

新建一個(gè)虛擬總線,僅保留一個(gè)符號(hào)位。明顯看到經(jīng)過(guò)500Hz低通濾波器濾波后,輸入的200+800Hz信號(hào)只剩下200Hz的單頻信號(hào)。且當(dāng)FIR濾波器輸出有效時(shí),m_tvalid信號(hào)置高。

原文鏈接:https://blog.csdn.net/fpgadesigner/article/details/80621411

-

matlab

+關(guān)注

關(guān)注

188文章

2992瀏覽量

232989 -

濾波器

+關(guān)注

關(guān)注

162文章

8038瀏覽量

180688 -

Xilinx

+關(guān)注

關(guān)注

73文章

2181瀏覽量

124089 -

IP核

+關(guān)注

關(guān)注

4文章

337瀏覽量

50352 -

Vivado

+關(guān)注

關(guān)注

19文章

827瀏覽量

68050

原文標(biāo)題:Vivado FIR IP核實(shí)現(xiàn)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Vivado 使用Simulink設(shè)計(jì)FIR濾波器

采用xilinx EDK的GPIO IP核實(shí)現(xiàn)中斷的功能(里面很詳細(xì)的)

Verilog中用*實(shí)現(xiàn)乘法和用乘法器ip核實(shí)現(xiàn)乘法的區(qū)別?

基于FPGA的FIR濾波器IP仿真實(shí)例

請(qǐng)問(wèn)如何使用單FIR編譯器v7.2核實(shí)現(xiàn)多頻帶帶通濾波器?

并行FIR濾波器Verilog設(shè)計(jì)

FIR IP用戶(hù)手冊(cè)

在測(cè)控系統(tǒng)中用IP 核實(shí)現(xiàn)D/A 轉(zhuǎn)換

在測(cè)控系統(tǒng)中用IP核實(shí)現(xiàn)D/A轉(zhuǎn)換

在測(cè)控系統(tǒng)中用IP核實(shí)現(xiàn)D/A轉(zhuǎn)換

基于vivado的fir ip核的重采樣設(shè)計(jì)與實(shí)現(xiàn)

FIR濾波器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

FPGA實(shí)現(xiàn)基于Vivado的BRAM IP核的使用

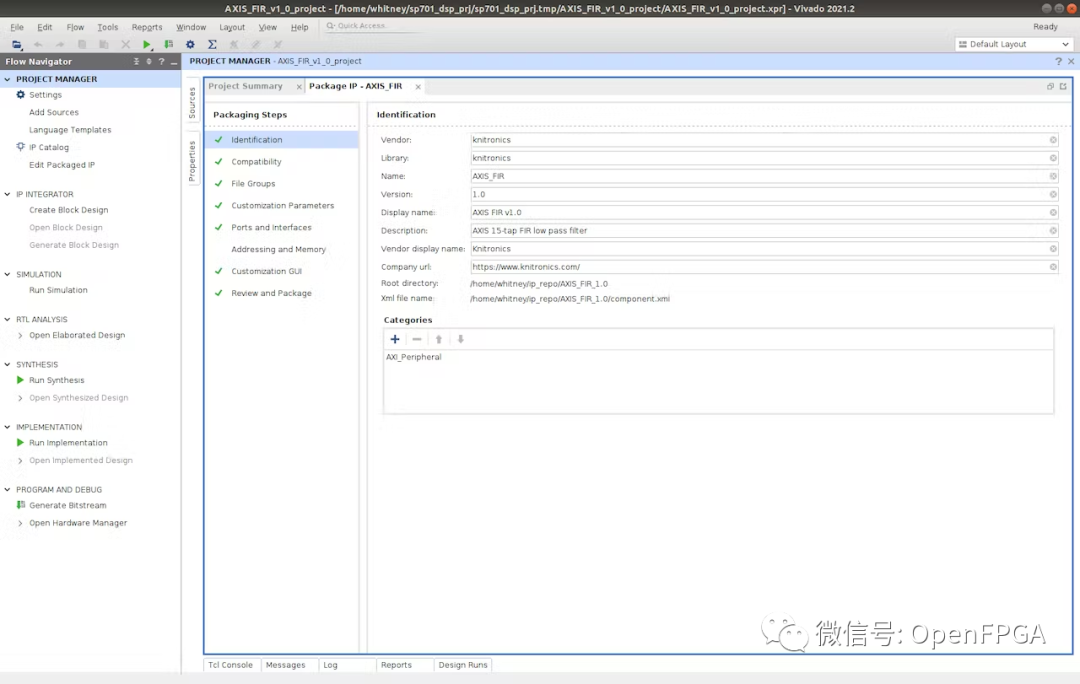

在Vivado中構(gòu)建自定義AXI4-Stream FIR濾波器IP 3

Vivado FIR IP核實(shí)現(xiàn)

Vivado FIR IP核實(shí)現(xiàn)

評(píng)論