一、JESD204 配置方式:

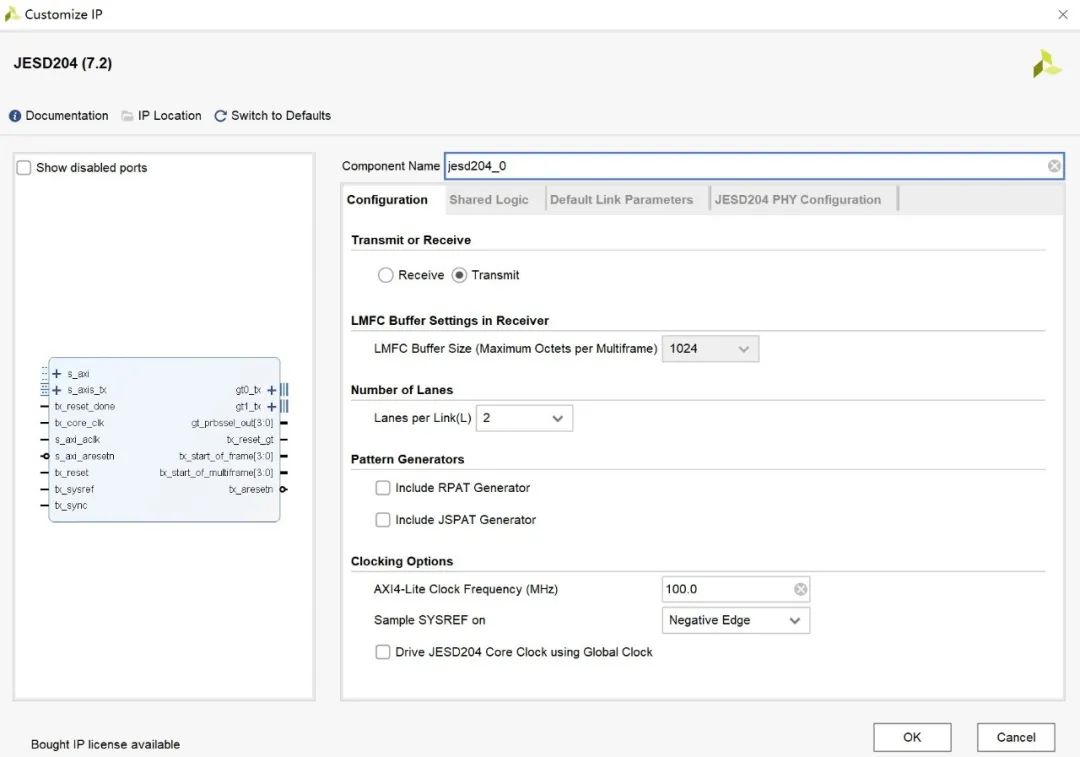

Configuration

1、Transmit or Receive: 選擇是作為接收機還是發(fā)射機

2、LFMC : 默認(rèn)值

3、Number of lanes : 傳輸?shù)耐ǖ罃?shù),根據(jù)實際需求選擇

4、pattern:模式的選擇,正常情況下兩個都不選

5、clocking options: AXI_lite總線配置IP核的時鐘頻率、以及觸發(fā)位置(下降沿觸發(fā)效果比較好)

6、Drive JESD204 core cloking using global clock:

時鐘的分配,如果收發(fā)器的時鐘頻率與核時鐘相同,二者可用同一個時鐘源。

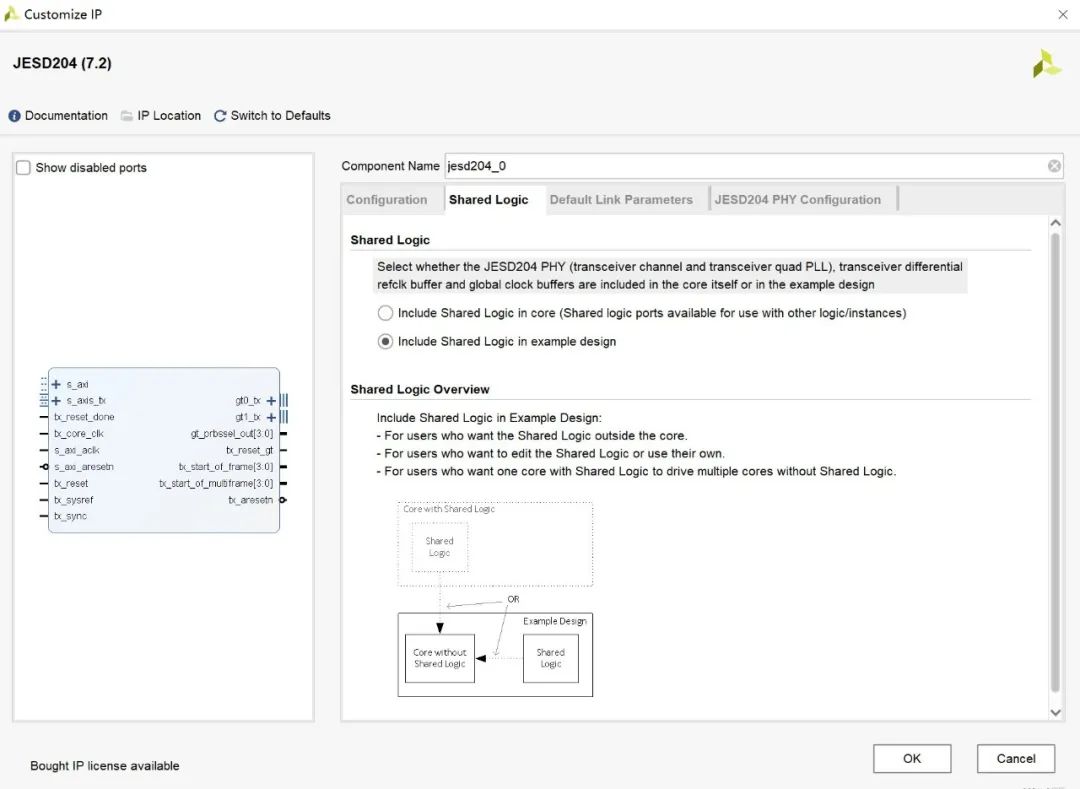

Shared logic

物理層的位置,一種是物理層在JESD204 IP里;另外一種是物理層在JESD204 IP外部,需要再配置JESD204 phy IP核進(jìn)行使用。

Include shared in core 比較簡單,容易配置。

Include shared logic in example design 配置起來比較復(fù)雜,但是這樣接收機和發(fā)射機可以共用一個收發(fā)器。

如果只使用接收機和發(fā)射機,推薦配置為Include shared in core,如果同時接收和發(fā)射,推薦配置為Include shared logic in example design

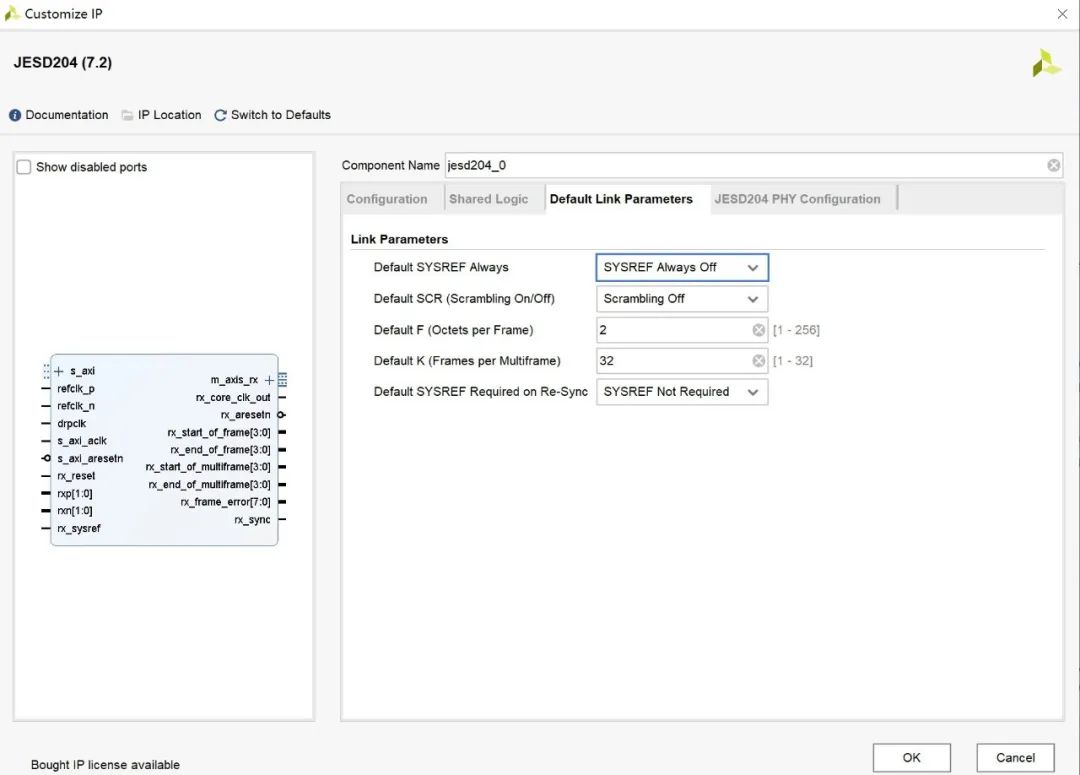

Default SCR : 是否添加擾碼

F: 每幀數(shù)據(jù)包含的字節(jié)數(shù)

K: K個幀組成一個復(fù)幀,要滿足ceil(17/F)<=K

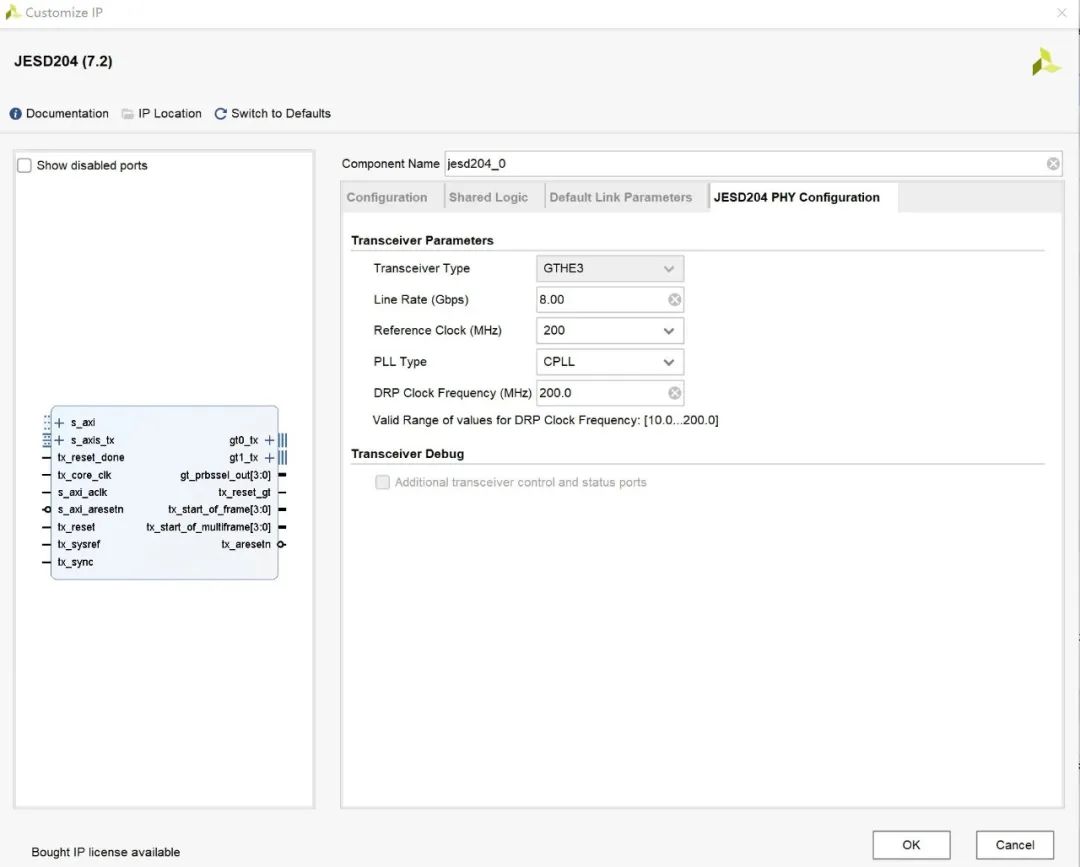

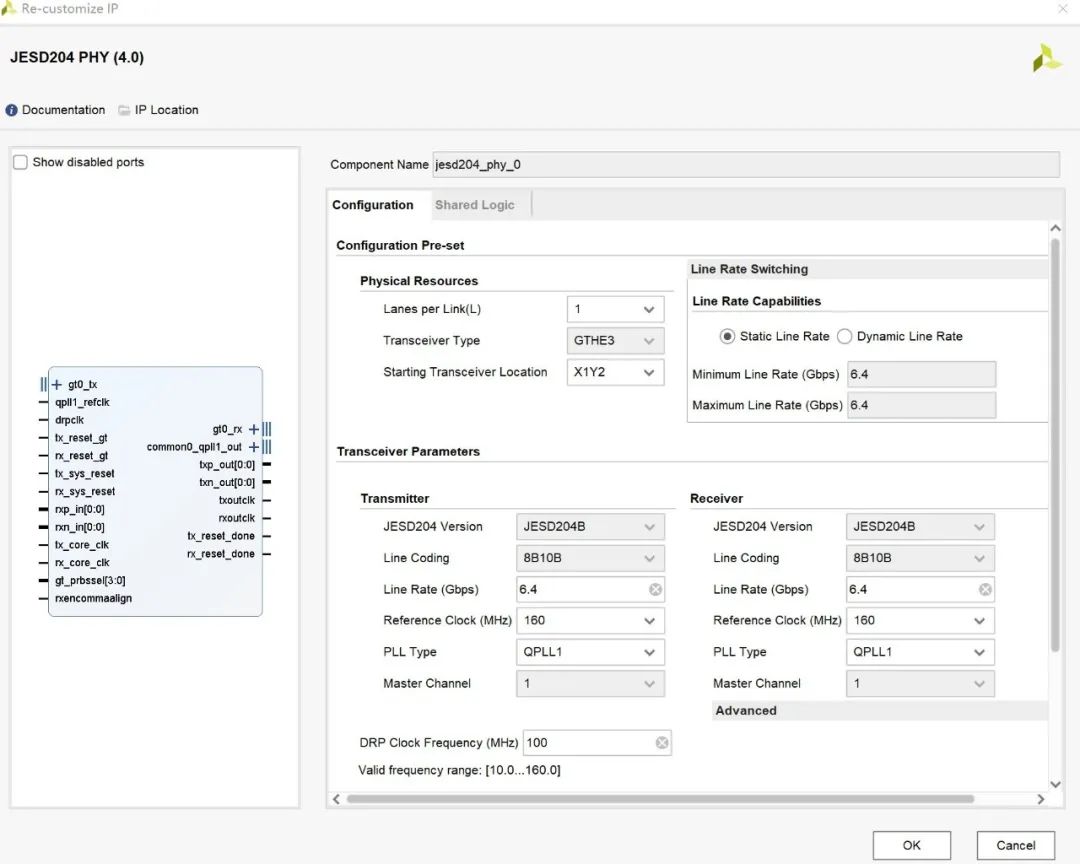

JESD204 PHYconfiguration

物理層的配置,選擇(Include shared logic in example design)沒有該配置界面。

1、type:收發(fā)器的類型,根據(jù)器件自動選擇。

2、lane rate :收發(fā)器的速率

3、reference clock:收發(fā)器的時鐘

4、PLL type: 收發(fā)器的類型,QPLL性能更好,適合高速率 的傳輸。

5、DPR clock:動態(tài)配置IP核的時鐘,GTH需要該時鐘。

二、JESD204 PHY配置方式(ultrascale系列的FPGA)

選擇(Include shared logic in example design)需要配置該IP核

configuration:

1、pre_set :這里包括通道數(shù)和收發(fā)器的位置。ultrascale需要選擇收發(fā)器的位置,具體選擇看對應(yīng)的原理圖

2、parameters: 這里和JESD204的配置一樣。

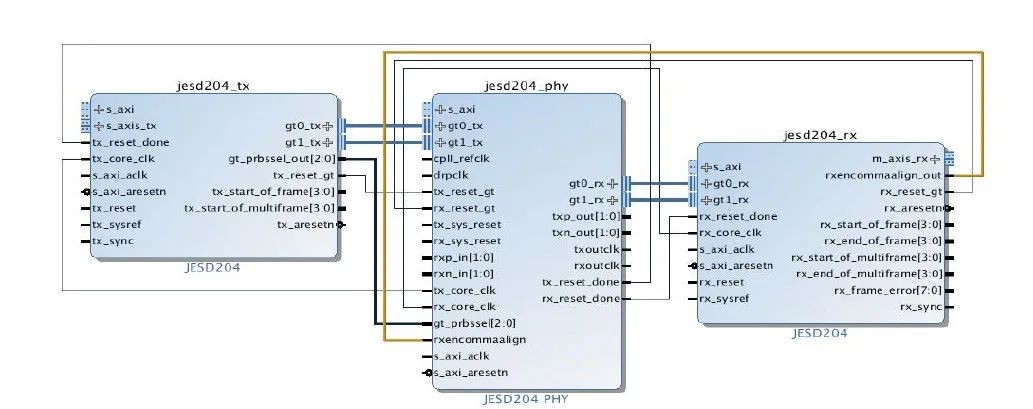

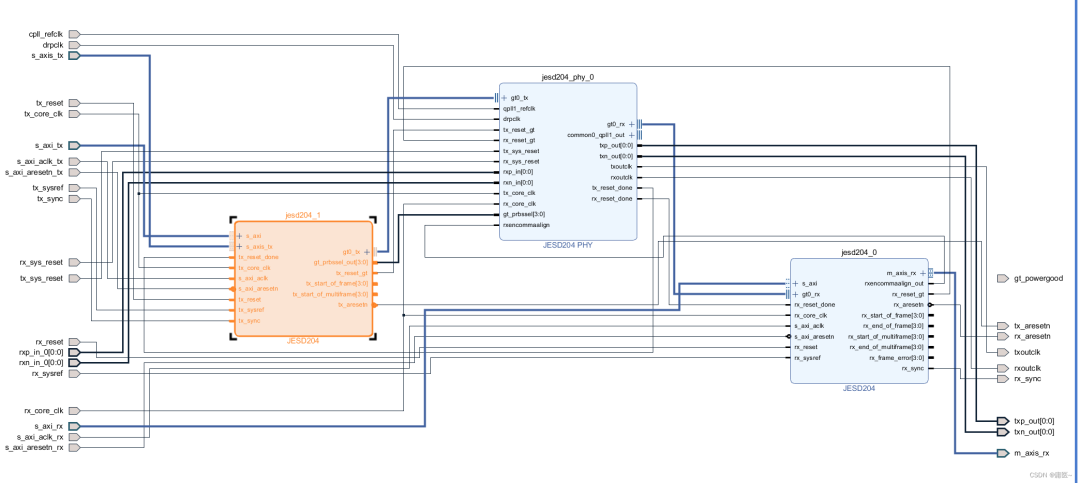

三、 IP核的使用

以Include shared logic in example design方式為例

首先兩個 IP核間的互聯(lián)。這些連接是鏈路層建立通道進(jìn)行的通信鏈路。

引出輸入輸出的接口。

IP核工作前需要用AXI_lite總線進(jìn)行配置,具體的寄存器和數(shù)值可以看官方文檔查看,也可以直接用JESD204生成一個官方的例程,參考其寄存器配置。

AXI總線配置完成后 IP就可以正常工作。

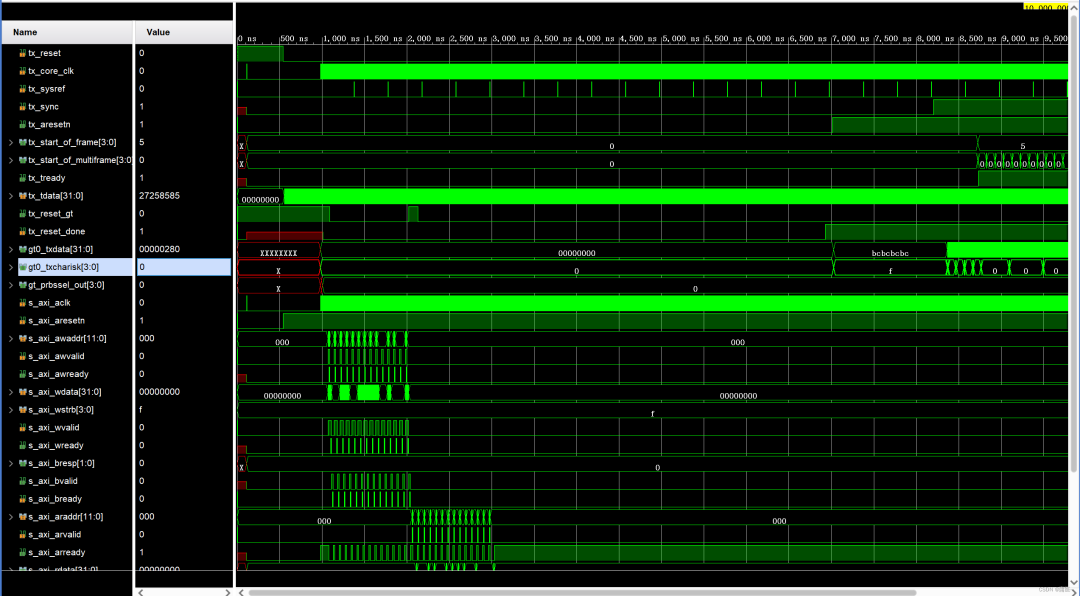

四、JESD204 的回環(huán)仿真

可以接收機與發(fā)射機互聯(lián)仿真查看是否有代碼錯誤

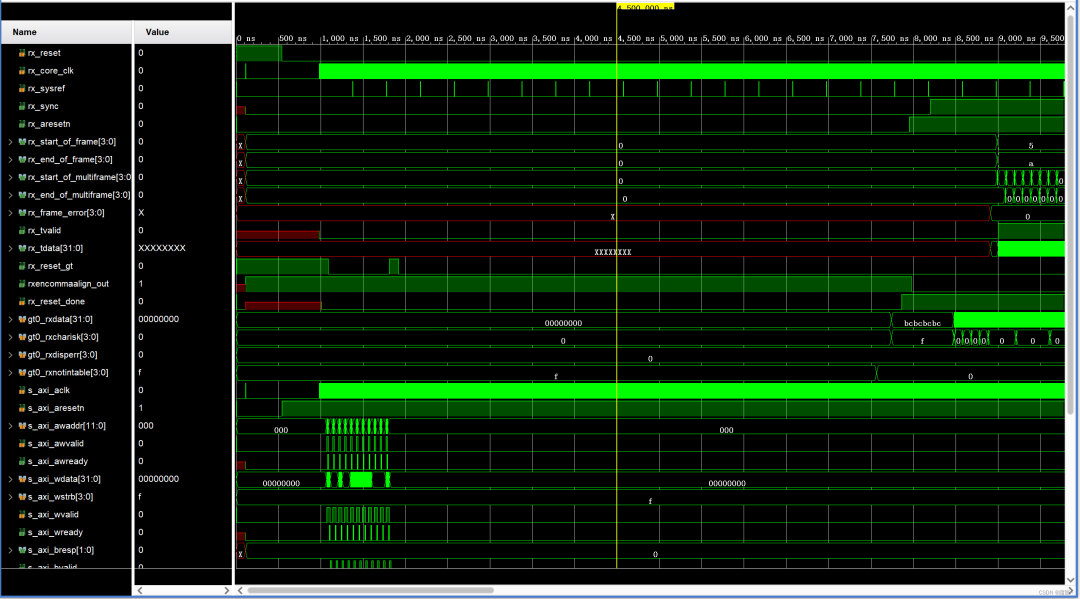

發(fā)射機的建立鏈路前后的狀態(tài):

內(nèi)核復(fù)位Tx_reset與AXI總線復(fù)位s_axi_aresetn結(jié)束,AXI總線開始配置JESD204 IP核,配置完成后,tx_reset_gt拉高一個時鐘,這個信號送到phy IP核,phy IP核接收到這個信號 后,內(nèi)部復(fù)位,復(fù)位結(jié)束后,傳回給tx_reset_done,該信號拉高代表物理層復(fù)位結(jié)束,可以向收發(fā)器傳輸數(shù)據(jù),此時TX發(fā)射機開始發(fā)K碼,接收機RX連續(xù)接到4個K碼后,sync拉高進(jìn)進(jìn)行碼組同步階段(CGS)。CGS結(jié)束后開始傳輸數(shù)據(jù)。

接收機的建立鏈路前后的狀態(tài):

與接收機的數(shù)據(jù)鏈路相似,內(nèi)核復(fù)位Tx_reset與AXI總線復(fù)位s_axi_aresetn結(jié)束,AXI總線開始配置JESD204 IP核,配置完成后,tx_reset_gt拉高一個時鐘,這個信號送到phy IP核,phy IP核接收到這個信號 后,內(nèi)部復(fù)位,復(fù)位結(jié)束后,傳回給tx_reset_done,該信號拉高代表物理層復(fù)位結(jié)束,可以向收發(fā)器傳輸數(shù)據(jù),此時RX接收機開始接收K碼,接收機RX連續(xù)接到4個K碼后,sync拉高進(jìn)進(jìn)行碼組同步階段(CGS)。CGS結(jié)束后開始傳輸數(shù)據(jù)。

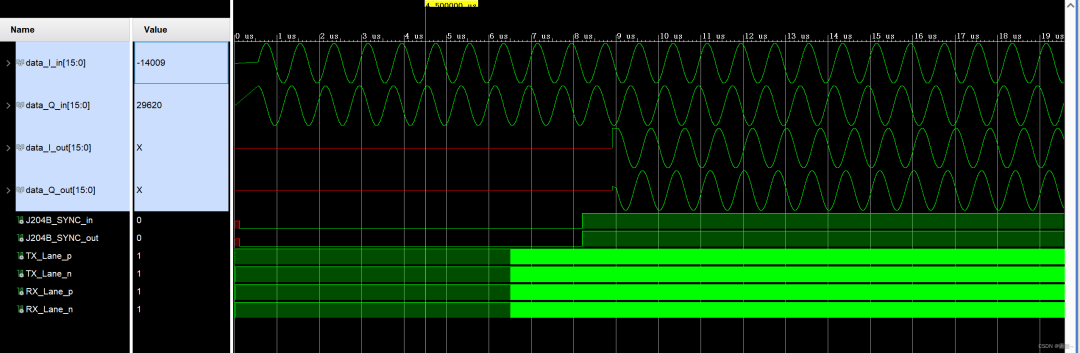

整體傳輸仿真

經(jīng)過一系列的復(fù)位后,lane上開始傳輸K碼,接收機接收到四個K碼后,sync拉高進(jìn)進(jìn)行碼組同步階段,CGS結(jié)束后開始傳輸數(shù)據(jù),此時接收機傳回的數(shù)據(jù)不在是高阻態(tài),為發(fā)射機傳輸?shù)臄?shù)據(jù)。

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3672瀏覽量

107950 -

寄存器

+關(guān)注

關(guān)注

31文章

5434瀏覽量

124474 -

IP核

+關(guān)注

關(guān)注

4文章

338瀏覽量

50807 -

JESD204B

+關(guān)注

關(guān)注

6文章

82瀏覽量

19589

原文標(biāo)題:JESD204B IP核的配置與使用

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

ad9680 JESD204B接口同步信號RX_SYNC失鎖 請問怎么解決?

在Xilinx FPGA上快速實現(xiàn)JESD204B

JESD204B串行接口時鐘的優(yōu)勢

jesd204b ip核支持的線速率

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

如何去實現(xiàn)JESD204B時鐘?

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對應(yīng)相連?

JESD204B SystemC module 設(shè)計簡介(一)

JESD204B標(biāo)準(zhǔn)及演進(jìn)歷程

Validating ADI Converters Inter-operability with Xilinx FPGA and JESD204B/C IP

Altera JESD204B IP核和TI DAC37J84硬件檢查報告

JESD204B IP核的配置與使用

JESD204B IP核的配置與使用

評論