前言

1、為什么做chiplet

2、Chiplet 的歷史與現(xiàn)狀

2.1 AMD

2.1.1 EPYC (Naples)

2.1.2 EPYC (Rome)

2.1.3 Ryzen (Matisse)

2.2 Intel

2.2.2 Lakefield SoC

2.2.3 Barefoot the Tofino 2 chip 7nm plus chiplet switch ASIC

2.3 Xlinix

2.4 Marvell Mochi

2.5 Hisilicon

2.6 HBM

3、Chiplet 的技術(shù)挑戰(zhàn)

3.1 Interconnect interface 的標準化

3.1.1 DARPA Chips 項目

3.1.2 OCP ODSA

3.1.3 OIF,JEDEC,CCIX 和其它

3.2 封裝技術(shù)

3.2.1 MCM - Multi Chip Module

3.2.2 Interposer

3.2.3 TSV

3.2.4 TSMC CoWoS

3.2.5 Fan-Out Wafer-level packaging

3.2.6 InFo WLP and fan-in WLP

3.2.7 Samsung FOPLP

3.2.8 Intel EMIB

3.2.9 Intel Foveros

3.2.10 價格與性能的折衷

3.2.11 高價值小批量的芯片

3.2.12 大規(guī)模生產(chǎn)類型的芯片

3.3 KGD&測試

3.4 EDA 工具

3.5 多供應商的電源,功耗管理問題

4 Chiplet 的商業(yè)模式挑戰(zhàn)

1、為什么做chiplet

這一輪chiplet 的風潮,是AMD 引領(lǐng)的。但是絕對不僅僅影響AMD,而是沖擊了整個半導體行業(yè)。

其實chiplet 不算是新概念,早在Marvell 在2016 年公布Mochi 架構(gòu)之前 ,2014 年海思與TSMC 的CoWoS 合作產(chǎn)品就上了新聞。

為什么要做chiplet,站在不同的位置,動機肯定不同。但是有一點有意思的地方,這是一個以fab 的角度,解決摩爾定律失效問題的方案,雖然TSMC 并沒有把chiplet 當作一個新技術(shù)突破,而是把interposer 當作新技術(shù)突破,但半導體業(yè)界的其它公司的立場各不一致。Marvell 最初說的是Mask 太貴,Xilinix 是突破die size 上限(可怕的FPGA 公司),AMD 說良率問題,Intel 上來就是mix-and-match,而Darpa,F(xiàn)acebook,要的是第三方

chiplet 的開放繁榮市場。

站在Fab 的位置,高良率的收益顯著,即使算上封裝的開銷,其次可以不同工藝節(jié)點的die 混封,有利于最新工藝的銷售。而且如果把memory 與logic 單元封裝在一起,無論是性能,功耗,還是尺寸大小方面的收益,其實還有管腳(pin)的收益,都是巨大,當然,這種情況下,價格就小貴了。

因此單純從生產(chǎn)角度看,大型最先進工藝的芯片,或者對性能,功耗和尺寸有超高要求,而價值比較高的芯片,適合做chiplet 的設(shè)計。

Chiplet 是針對超貴芯片的一種相對省錢設(shè)計,在初期。

站在2014 年左右開始chiplet 計劃的fabless 的芯片設(shè)計公司角度看,如果公司內(nèi)部的產(chǎn)品線復雜,例如海思,Marvell,而每一個產(chǎn)品的數(shù)目不巨大(Marvell 的VP,公開抱怨過蘋果與三星,這種公司殺入半導體設(shè)計產(chǎn)業(yè),造成出貨量驟減,新工藝又貴),chiplet 的重用性的好處巨大。

在2016 年,Darpa 啟動的Chips 項目,把這種chiplet Reuse 的想法,推到了整個產(chǎn)業(yè)界面前。

但是AMD 的EYPC 系列的成功,才真正讓chiplet 進入主流業(yè)界視線。

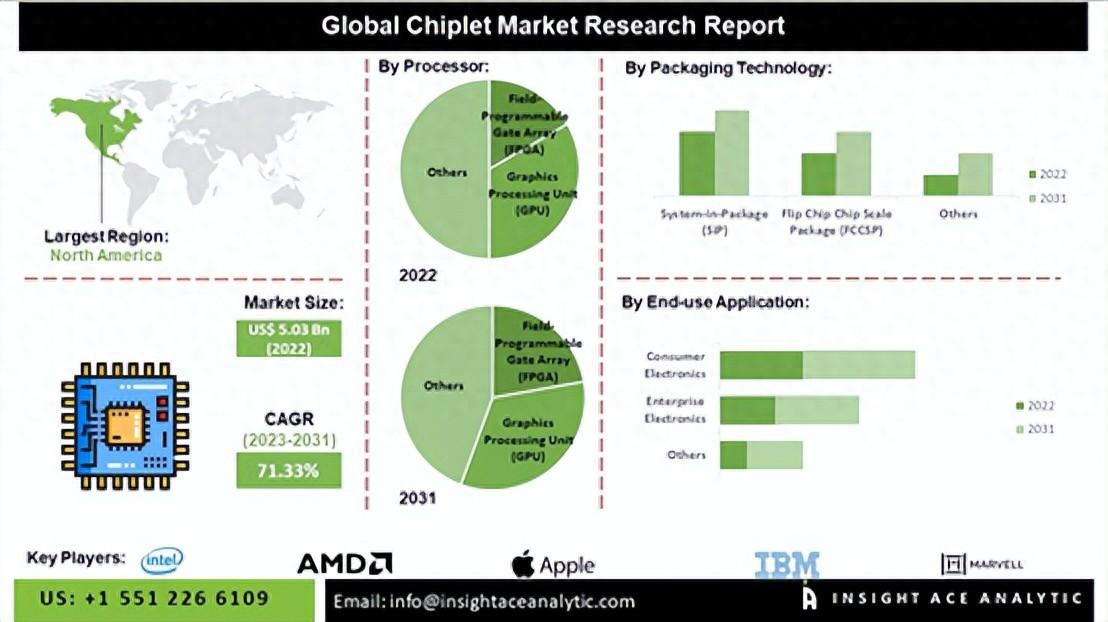

更多的玩家進入,更多的設(shè)計樣本,推動成本的下降,成本的下降推動chiplet 生態(tài)發(fā)展。chiplet 的發(fā)展前景如何,特別是獨立第三chiplet 供應商的商業(yè)模式是否成立,誰會從中獲益,誰會被產(chǎn)業(yè)鏈優(yōu)化出局,現(xiàn)在尚未可知。

特別是互聯(lián)網(wǎng)公司的介入,讓這個本身就具有顛覆行業(yè)能力的技術(shù),更為特出的重要。

2、Chiplet 的歷史與現(xiàn)狀

本來應該按時間順序?qū)懀俏蚁胂耄凑展緛韺懀鋵崊⒖夹愿摺R粋€公司的發(fā)展路徑,是一個公司和它的上下游合作伙伴的智慧結(jié)晶。半導體行業(yè)的架構(gòu)師,多數(shù)拿著超過市場平均價的高薪,規(guī)劃著5 年,甚至10 年的路標,真是集智慧,對行業(yè)理解,和對行業(yè)影響力為一身的強者工作。

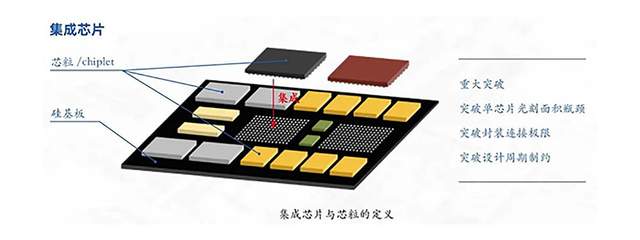

而chiplet 起初是fab 為了解決fab 中的一些問題而提出來的方案,而且技術(shù)突破的難點都在fab 側(cè)。因此我把fab 的技術(shù)發(fā)展列為技術(shù)挑戰(zhàn),而不是歷史。

2.1 AMD

2.1.1 EPYC (Naples)

EPYC 是AMD 在服務(wù)器CPU 市場上的翻身帳開始,在發(fā)布會上,AMD 明晃晃的提出打破摩爾定律的限制,這個來自fab 的說法。

每個EPYC 處理包括4 個Zeppelin die,使用的還是2D 的 MCM (Multi-chip module)封裝。

AMD 的革命性 the Infinity Fabric,不僅僅是die-to-die 的互聯(lián)總線,還是

processor-to-processor 的互聯(lián)總線。從這里也可以看出來,cache coherent 互聯(lián)總線設(shè)計,和CPU 的設(shè)計關(guān)系緊密,凡是 cache coherent 互聯(lián)總線的標準背后都有家CPU的設(shè)計公司。

AMD EPYC 1st Gen

Zeppelin die 包含2 個core complex-CCX。一個Zeppelin die 做桌面產(chǎn)品,2個Zeppelin die 做高端桌面產(chǎn)品, 4 個Zeppelin die 就是服務(wù)器產(chǎn)品。

Zeppelin Die

單獨看, 每個Zeppelin die 都包括單獨的memory, IO complex,infinity

Fabric 的控制與接口,下圖更清晰一點。每個Zeppelin die 是213mm^2,4 個die 就是852mm^2。AMD 給了如果用一個single chip 設(shè)計的話,die 的大小大約就是777mm^2,也就是說有10%的面積損耗,但是777mm^2 非常接近reticle limit size 了。

名詞解釋 reticle limit size, 這是光刻機能夠處理的最多的尺寸。對于193i

immersion steppers 這個限制就是33*26, 856mm2, TSMC 的12nm 工藝,估計TSMC 會設(shè)置成815 這類數(shù)字。

對于單一產(chǎn)品的生產(chǎn)測試,良率,最后的價格,我相信,AMD 的工程師與架構(gòu)師一定反復核算過。Intel 的工程師與架構(gòu)師采取冗余設(shè)計來保護single chip 設(shè)計,這也是同一個die,有不同的核數(shù)的原因。這兩種方式都是在提高良率,降低制造成本,以損失性能的代價。

但是如果從公司層面看,對于研發(fā)成本,一個Zeppelin die 可以覆蓋服務(wù)器和桌面兩個市場,這個收益明顯。想想AMD $6.48 billion 的收入,與Intel 的$70.848billion, 合情合理。[TSMC 臺積電的2018 收入是US$32.47 billion]

其實從Intel 的lakefield 上看,10nm CPU/GPU die 加 22nm 的I/O die,尺寸上的收益明顯,重用22nm 的I/Odie,對于開放成本,時間,相比收益也是不錯的。

EPYC(Naples)的架構(gòu)

最后放一張chiplet 的代價。

EPYC(Naples) 內(nèi)部帶寬

2.1.2 EPYC (Rome)

Rome 的設(shè)計,甚至比Naples 還難做決定。要提高IPC,要雙倍性能。

而且不能再一個die,同時兼顧服務(wù)器和PC 市場。AMD 試圖在一個chiplet 上加倍核數(shù)(就是說要設(shè)計一個400+mm^2),然后保持4 個die 的設(shè)計,然而向現(xiàn)實妥協(xié)的結(jié)果是9個die 的設(shè)計。

而且從一個chiplet 上包含內(nèi)存控制器,I/O 和Infinity 互聯(lián)的接口, 轉(zhuǎn)變?yōu)橛幸粋€中央集中式I/O 和內(nèi)存控制器die,而且這個集中IOD 仍然有14nm 工藝,CCD 仍然保持8 個核的設(shè)計。8 個CCD die, 一個IOD,最高核數(shù)為64 個。

每個CCD 上的核數(shù),可以根據(jù)良率變化,每個SKU 上的chiplet 數(shù)目也可以選擇,因此真正最終產(chǎn)品的核數(shù),有多種組合。

好消息是Rome 的下一代Milan 仍然是9die 的設(shè)計,有點tock 的意思。而且I/Odie 看起來變化不大,不知道是不是重用舊設(shè)計,僅僅升級工藝,但是Milan 的CCD 的設(shè)計有增強。這也是chiplet 設(shè)計的好處,不同的die 可以分離演進。服務(wù)器的IOD 和Client 的IOD 也演進為兩個設(shè)計。

Rome 的CCD 的面積是74mm2,包括了3.9B 的transistors。對比Zepplin 的CCX面積大約是88mm2,2.8B 的transistors,感覺改進還是巨大的,7nm 的工藝進步也是顯著的。

Rome 的IOD 有125mm2,

EPYC(Naples)與 EPYC (Rome)

EPYC (Rome)

AMD Chiplet 設(shè)計路標

2.1.3 Ryzen (Matisse)

我這里并不想過多的分析Ryzen,只是想指出,Ryzen 產(chǎn)品線重用了 EYPC Rome 的CCD。只是單獨配了一個Client IOD。

對于產(chǎn)品線復雜的公司,chiplet 設(shè)計,極好的降低了總研發(fā)費用。

Ryzen (Matisse) 架構(gòu)

Ryzen (Matisse)

2.2 Intel

Intel 真是一個復雜的公司,首先,它可不是fabless,它是唯一一家有fab 的半導體設(shè)計公司。真心想知道,它的這種超強商業(yè)模式,在這輪chiplet 浪潮中,會不會受影響呢。

前面有說, chiplet 是fab 主導開始的,解決最新工藝貴,且良率低,或者超大芯片到達物理極限的問題的。Intel 在fab 技術(shù)和制定業(yè)界標準上都強,EMIB, HBM 的3D 封裝, AIB 的總線, Foveros,CXL 這些都是Intel 的出品。

2.2.1 Altera Stratix 10 FPGA

Stratix 10 是Intel 第一款使用EMIB 的設(shè)計,中心是FPGA die,周圍是6 個

chiplet。4 個高速transceiver chiplet 和2 個高帶寬memory chiplet。這6 個chiplet,是來自三個不同fab 的6 個不同工藝chiplet,用來證明不同fab 之間的強大互操作性。

Stratix 10

2.2.2 Lakefield SoC

Stratix 10 是用的EMIB,所謂的2.5D 封裝技術(shù), Lakefield 親孩子,就是用上了3D 封裝,當然Intel 重新給它了一個名字Foveros。

Lakefield 架構(gòu)

Lakefield 有兩個技術(shù)有趣點,一是不同核的big.little 混合架構(gòu),二是

chiplet 設(shè)計,一個compute die,一個base die。Base die,主要是I/O 功能,性能不敏感,因此可以用22nm 工藝,而混合了大小CPU 核,IPU,GPU 的compute die,會持續(xù)演進,用7nm,5nm 工藝。

3D Foveros 封裝技術(shù),從名字上可以感覺一二,我們留到技術(shù)挑戰(zhàn)那章再講。

2.2.3 Barefoot the Tofino 2 chip 7nm plus chiplet switch ASIC

這是Ethernet Switch(以太網(wǎng)交換機)市場的第一款分離為chiplet 的設(shè)計,broadcom 的7nm Trident 4倒是還是單片設(shè)計。

Switch ASIC 長期以來都是把模擬和邏輯部分放在一起設(shè)計的,模擬部分,其實和邏輯部分,演進的時間表完全不同。如果是單芯片設(shè)計,模擬部分也不得不隨著邏輯部分的工藝演進前進。如果采用chiplet 分離設(shè)計,例如Barefoot 的模擬部分,采用老一點的工藝,Barefoot 沒有透露,因此大家從28nm,16nm,12nm 都有猜, 邏輯部分則是最新的7nm 工藝。

Chiplet 不僅僅帶來了模擬部分的工藝節(jié)省,而且還可以通過不同的chiplet 配置,來提供不同的SKU。對比傳統(tǒng)的單片設(shè)計,干脆disable 一部分芯片的方式,這種chiplet 就經(jīng)濟實惠多了。

Barefoot 的Tofino2

想想Barefoot 的startup 出身,猜有chiplet 的設(shè)計,也算是順理成章。

2.3 Xlinix

講chiplet FPGA 公司必須有名字。FPGA 公司因其屬性和高利潤性,一直是各種先進工藝的率先使用者。而FPGA 一開始采用Chiplet 方案,就是為了打破fab 的物理限制,做超大芯片。

講真,其實所有AISC 的新應用領(lǐng)域,都是從FPGA 的設(shè)計開始的。

2011 Virtex-7 2000T 就是4 個die 的chiplet 設(shè)計。文獻20 中的Xilinx 的白皮書,是比較好的對于chiplet 技術(shù)的一個探討。Chiplet 并不是一個新技術(shù),只是在新工藝節(jié)點越來越貴,競爭越來越激烈的半導體市場上,又重新被廣泛應用了而已。

Xilinx 號稱提供業(yè)界唯一的同構(gòu)和異構(gòu)的3D IC。

virtex-7 系列

2.4 Marvell Mochi

Marvell 提出Mochi 概念,最大的驅(qū)動力是降低成本,模塊化芯片設(shè)計,像LEGO 那樣,提高模塊的重用性。借助基本模塊的重用,還能在保持靈活性的同時,加快新產(chǎn)品的上市時間。

Mochi 應用的案例 智能手機

2015 年當時的Marvell CEO Sehat Sutardja 估計到2018 年開一個Mask 的價格是$10million (我也不知道這個價格,是不是對,知道的同志們,可以吱一聲),因此要有25M 的出貨量的產(chǎn)品,ROI 才合算。不知道大家對25M 這個數(shù)字是否有感覺,但是基本上,服務(wù)器(約12M),4G 基站(約7M),汽車(86M)這種市場就不用考慮最新工藝了。

芯片研發(fā)成本

Marvell 采用了Kandou Glasswing IP 作為die-to-die 的接口, 而Kandou 依然非常活躍在chiplet 的互聯(lián)標準組織中。但是這個chiplet 互聯(lián)標準,是一個新生態(tài)的核心標準,競爭者眾多。

2.5 Hisilicon

海思的第一片公開的chiplet 設(shè)計,就是2014 年TSMC 16nm FinFet 網(wǎng)絡(luò)芯片。這個時間,這個工藝,這個CoWoS,都是閃閃亮的頂配。

圖2.16 CoSoW

海思因為其屬性,公開消息并不多。往往是因為合作伙伴,需要展示自己的技術(shù)突破,海思才被迫營業(yè),站臺示眾。這個海思1616 就是這樣掛在TSMC 的網(wǎng)站上的。

晟騰910 的8 個chiplet 設(shè)計,融合了HBM die,邏輯部分與I/O 部分分離,兩個dummydie,超大總die size 等特點。也算是業(yè)界標桿性設(shè)計。

17 Ascend910

2.6 HBM

HBM 從設(shè)計開始就是3D 封裝的,因此有些討論chiplet 的文章,并不包括HBM。但是在我看來,凡是采取多die 封裝的,都算是chiplet 的范疇。Memory die 也是chiplet,而且memory 公司賣Known good die 的歷史蠻長。

2016 年 AMD Radeon R9 Fury X 是第一個采用HBM 的芯片。Nvidia 緊隨其后。

Fujitsu 的PostK supercomputer 設(shè)計,也采用了CPU die 與HBM 一起封裝的設(shè)計,因此A64FX 芯片的管腳,要比一般的芯片精簡不少。

3、Chiplet 的技術(shù)挑戰(zhàn)

先坦白的說,出來接口標準這一節(jié)以外,這一章,我也是外行。而且說起標準這事,我也只熟悉幾個。

我給大家把資料備齊,大家鑒別著,當參考材料讀一下吧。

3.1 Interconnect interface 的標準化

互聯(lián)接口標準化重要么?僅僅在需要對接來自不同廠家的chiplet 的時候,才重要。一個公司內(nèi)部,他們自己心里有數(shù)就好。

現(xiàn)有接口能解決這個問題么?其實能的,如果不追求高帶寬,低延遲,這類性能指標。回想一下前面的案例, 邏輯die 和IO die 之間,需要什么接口?

3.1.1 DARPA Chips 項目

DARPA 先講了一個與商業(yè)芯片公司不同的動機,就是如何降低高研發(fā)成本,特別是對于量不大的應用。DARPA 用的芯片,估計量也大不到哪里去,卻不得不用啊,商業(yè)市場的那套“走量”的生意模式,這里肯定是不行的。

可以如logo 一樣拼接組合的chiplet,肯定是一條出路。

CHIPS 項目的一個重大成果就是Intel 的AIB( Advanced Interface Bus),這是一個royalty free 的chiplet-to-chiplet (or die-to-die) 的物理層接口標準。Intel Stratix 10 FPGA 用的就是AIB 接口。

(在github 上找得到代碼的項目,才是真。開源項目)

但是有意思的是2018 年開始的ERI 電子復興計劃第二期中的3DSoC Three Dimensional Monolithic System-on-chip 3D 單芯片系統(tǒng)。

DARPA ERI

3.1.2 OCP ODSA

相對于DARPA 糾結(jié)的哪些閃光的logo 們,OCP 的ODSA 工作組相對平民化很多,當然, Global Foundries 在鎮(zhèn)場子。ODSA 把die-to-die 的層次。而且ODSA 把chiplet marketplace 的口號提了出來。

這個和DARPA 解決量小芯片項目的目的是不同的。

Chiplet 市場這件事,如果做得好,可以改變產(chǎn)業(yè)界的分工合作關(guān)系。所謂的優(yōu)化供應鏈,就是新的一輪洗牌。

ODSA 的接口標準, 分層概念提的很清晰,CCIX+PCIe 也是看熟悉。但是如果試圖包括一切,標準的統(tǒng)一性就不會好,用來對接的標準不

OCP ODSA

3.1.3 OIF,JEDEC,CCIX 和其它

OIF 有一些關(guān)于die-to-die 的討論(看了看,不算明白)。JEDEC 一直出memory 接口標準的。歷史上一個好標準,被借用在其它地方的事情也時有發(fā)生。Memory 業(yè)界一直出好標準。

還有一些公司,就不搞什么標準,直接上產(chǎn)品,例如Cadence Ultralink D2D PHY IP ,Synopsys 新出的 DesignWare die to die PHY IP 簡單,高效,我喜歡。

物理層,把chiplet 對接在一起。而在物理層之上,有兩種類型傾向的語以接口,I/O 類型的和memory 類型的。保持一致性,以硬件復雜換取軟件簡單?還是不保持一種性追求高效。ARM,AMD 一開始支持的CCIX,與Intel 主導的CXL,哪個能成為chipet-tochiplet的主流標準?目前尚未有結(jié)論。

3.2 封裝技術(shù)

如果可以,我想寫略。

標準,我多少還是知道的。封裝技術(shù),就實打?qū)嵉牟恍辛恕?/p>

我把能用來索引的關(guān)鍵字留下來。你們自己努力吧。

3.2.1 MCM - Multi Chip Module

3.2.2 Interposer

3.2.3 TSV

3.2.4 TSMC CoWoS

3.2.5 Fan-Out Wafer-level packaging

3.2.6 InFo WLP and fan-in WLP

3.2.7 Samsung FOPLP

3.2.8 Intel EMIB

3.2.9 Intel Foveros

3.2.10 價格與性能的折衷

3.2.11 高價值小批量的芯片

3.2.12 大規(guī)模生產(chǎn)類型的芯片

3.3 KGD&測試

工業(yè)標準測試非常重要。通常,我們只做整個芯片的測試,但是現(xiàn)在我們需要在封裝前,測試出“known good die”。業(yè)界需要一個KGD 策略和一個測試策略,目前還是空缺的。測試裸die,可比測試整個芯片麻煩多了,也難多了。

而且要獨立測試chiplet,對于功能并不獨立的某些chiplet,也很復雜。

3.4 EDA工具

EDA 工具對chiplet 的支持,仿真,都是需要慢慢補齊的。

3.5 多供應商的電源,功耗管理問題

多個chiplet 的多供應商的電源,功耗管理,都是問題。需要標準,也需要業(yè)界統(tǒng)一。

4、Chiplet 的商業(yè)模式挑戰(zhàn)

如果上章的技術(shù)問題,都能完美的解決。讓我們重新考慮一下chiplet 這個技術(shù)方案的商業(yè)動機。

最初chiplet 是為了打破芯片面積的物理上限,而近期是為了解決最新工藝節(jié)點的高昂IC設(shè)計費。

例如,28nm 需要$51.3 million, 7nm 芯片需要$297.8 million (International Business Strategies (IBS))

人間理想,一個開放的數(shù)量巨大的chiplet 市場, 客戶可以自由的mix-and-match, 不同的邏輯使用不同的工藝節(jié)點,IP 可以重用,研發(fā)費用在多個設(shè)計之間平攤, 創(chuàng)新度劇增。

誰受益,誰有可能受損?

工廠和封裝廠肯定是受益方。

IP 公司會是受益方么?賣IP RTL 風險小,把自己手中的IP 升級為chiplet 利潤高。

Chiplet 降低了半導體設(shè)計的門檻,對于新進入的公司,是一個好消息,但是這chiplet 的這種模塊化設(shè)計,其實拆分了半導體公司的方案,消弱了整體競爭能力。

對于最終的買家來說,降成本的chiplet 無疑是受歡迎的。

Darpa 的預言

放一張Darpa 的chips 產(chǎn)業(yè)最終狀態(tài)和傳統(tǒng)供應鏈的對比,那些設(shè)計,驗證的fabless 芯片公司不見了。

如果只是小startup 公司與IP 公司,參與Chiplet 的生態(tài)建設(shè),對于半導體這個投資巨大的產(chǎn)業(yè)來說,只是促進產(chǎn)業(yè)創(chuàng)新,不會有大風浪。

如果大型hyperscale 公司,例如AWS,Google,也加入到這場新生態(tài)的建設(shè)之中,那么現(xiàn)存的大魚們,就要有危機意識了。

有端到端設(shè)計能力的超大型hyperscale,可以站在上帝視角,優(yōu)化產(chǎn)業(yè)鏈。這是可怕之處。

責任編輯:pj

-

IP

+關(guān)注

關(guān)注

5文章

1805瀏覽量

152585 -

芯片公司

+關(guān)注

關(guān)注

3文章

18瀏覽量

8886 -

chiplet

+關(guān)注

關(guān)注

6文章

459瀏覽量

12997

發(fā)布評論請先 登錄

Chiplet與先進封裝設(shè)計中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進封裝

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

Chiplet:芯片良率與可靠性的新保障!

2.5D集成電路的Chiplet布局設(shè)計

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

Cadence推出基于Arm的系統(tǒng)Chiplet

Chiplet技術(shù)有哪些優(yōu)勢

2035年Chiplet市場規(guī)模將超4110億美元

IMEC組建汽車Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺

2031年全球Chiplet市場預測

國產(chǎn)半導體新希望:Chiplet技術(shù)助力“彎道超車”!

Chiplet 的歷史與現(xiàn)狀

Chiplet 的歷史與現(xiàn)狀

評論