日前,在斯坦福大學舉行的IEEE Hot Chips研討會上,創業公司Cerebras推出了有史以來最大的芯片。按照他們的說法,這個大致是硅晶片尺寸的系統旨在將AI訓練時間從幾個月縮短到幾分鐘。

這是自二十世紀八十年代Trilogy Systems任務失敗以來,業界再一次出現對晶圓級處理器的商業嘗試。

下面,我們來談一下有關這個芯片,你必須知道的六點::

數據

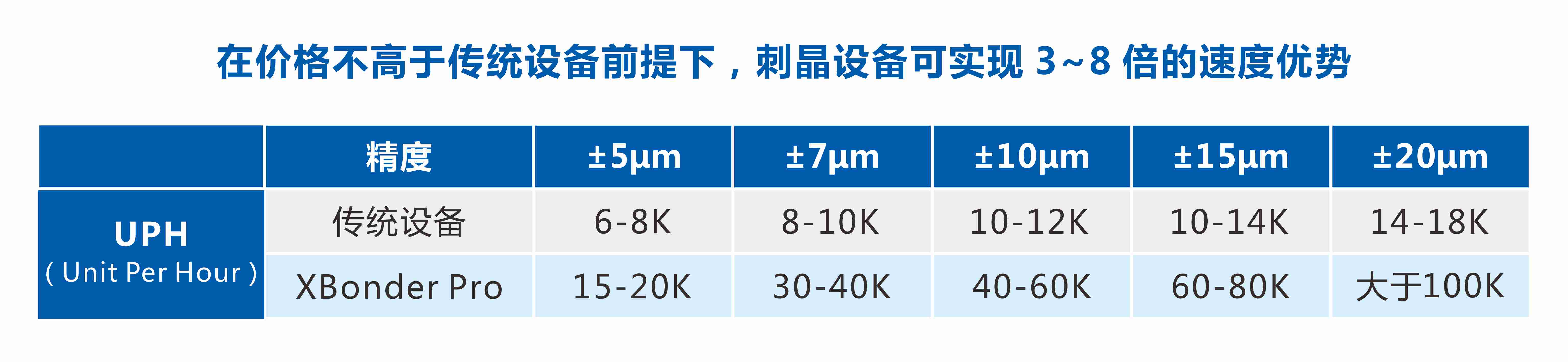

作為有史以來最大的芯片,Cerebras的Wafer Scale Engine(WSE)自然帶有一堆最高級的。這是當中的一部分:

尺寸:46,225平方毫米。這大約是一張信紙大小的紙張的75%,但卻是最大GPU的56倍。

晶體管:1.2萬億。Nvidia的GV100 Volta僅為21億。

處理器核心:400,000。而GV100只有5,660。

內存:18千兆字節的片上SRAM,大約是GV100的3000倍。

內存帶寬:每秒9 PB。據Cerebras稱,這是我們最喜歡的GPU的10,000倍。

你為什么需要這個怪物?

Cerebras在其白皮書中提出了一個非常好的案例,為什么這么大的芯片有意義。

基本上,該公司認為,訓練深度學習系統和其他人工智能系統的需求已經失控。該公司表示,訓練將出現一種新模式——創建一個這樣的系統,那就是一旦經過訓練,就可以識別人或贏得Go游戲。但這在過去需要花費數周或數月的時間,并耗費數十萬美元的計算時間。這個成本意味著實驗的空間很小,這會扼殺新的想法和創新。

這家公司的答案是,全世界需要更多,更便宜的訓練計算資源。而訓練也需要幾分鐘而不是幾個月,為此,您需要更多內核,更多靠近這些內核的內存,以及內核之間的低延遲,高帶寬連接。

這些目標將對AI行業中的每個人造成影響。但是Cerebras也承認,這個想法推向了它的邏輯極端。一塊大芯片為處理器內核和需要依賴它的內存提供了更多的硅片面積。只有當數據永遠不必離開芯片上的短而密集的互連時,才能實現高帶寬,低延遲的連接。因此這也是他們打造這樣一個大芯片的原因。

在這400,000個內核中有什么?

根據該公司的說法,WSE的內核專門用于人工智能,但仍然具有可編程性,那就意味著該芯片并不會僅僅被限定在AI當中。這就是他們所謂的稀疏線性代數(Sparse Linear Algebra:SLA)核心。這些處理單元專門用于“人工智能”工作的“張量”操作,但它們還包括一項減少工作的功能,特別是對于深度學習網絡。據該公司稱,深度學習訓練集中所有數據的50%至98%為zero。因此,非零數據“Sparse ”。

SLA核心通過簡單地不將任何東西乘以零來減少工作量。內核具有內置的數據流元素,可以根據數據觸發計算操作,因此當數據遇到零時,不會浪費時間。

他們是怎么做到的?

Cerebras龐大的單芯片背后的基本理念已經存在了幾十年,但它也是不切實際的。

早在20世紀80年代,并行計算的先驅 Gene Amdahl就制定了加速大型機計算的計劃——硅片大小的處理器。換句話說,就是將大部分數據保留在處理器本身而不是將其通過電路板推送到存儲器和其他芯片。這樣的計算將更快且更節能。

借助從風險投資家手上拿到的2.3億美金,Amdahl創立了Trilogy Systems,并實現了他的愿望。但我們不得不承認,“晶圓級整合”的第一次商業嘗試是一場災難,據當時報道,它成功地將動詞“to crater”引入金融新聞詞典。

最基本的問題是芯片越大,良率越差。從邏輯上講,這應該意味著晶圓級芯片將無利可圖,因為您的產品總會存在缺陷。Cerebras的解決方案是添加一定量的冗余。據EE Times稱,Swarm通信網絡具有冗余鏈路,讓產品工作時可以繞過受損核心。據透露,當中大約有1%的核心是備用的。

Cerebras還必須解決一些關鍵的制造限制問題。例如,芯片工具設計用于將其特征定義圖案投射到相對較小的矩形上,并在晶圓上完美地反復進行。由于在晶片上的不同位置鑄造不同圖案的成本和難度,僅此一點就會使許多系統不能構建在單個晶片上。

但WSE就像一個典型的晶圓,完全由相同的芯片組成,就像你通常制造的一樣。最大的不同之處在于他們與臺積電合作開發了一種方法,用于在芯片之間的空間建立連接,這個區域稱為scribe lines。而這個空間通常留空,因為芯片沿著那些線切割。

根據Tech Crunch的說法,Cerebras還必須發明一種方法,為芯片提供15千瓦的電源和冷卻系統,并創造新的連接器,以便在加熱時處理它擴展的方式。

這是制作晶圓級計算機的唯一方法嗎?

當然不是。例如,加利福尼亞大學洛杉磯分校和 Illinois Urbana-Champaign的團隊正在研究一種類似的系統,該系統也構建了裸處理器并進行了測試,并將它們安裝在已經圖案化所需的密集互連網絡的硅片上。這種稱為硅互連結構的概念允許這些小芯片緊密相連(相隔100微米),這就使得芯片間通信接近單個芯片的特性。

“這是我們一直在進行驗證的研究”,伊利諾伊大學的 Rakesh Kumar說。

Kumar認為硅互連結構方法與Cerebras的單片晶圓級方案相比具有一些優勢。首先,它允許設計師混合和匹配技術,并為每個技術使用最佳制造工藝。單片方法意味著為最關鍵的子系統邏輯選擇最佳的制程,并將其用于存儲器和其他原件,即使不適合它們。

Kumar建議,在這種方法中,Cerebras可以限制它可以放在處理器上的內存量。“他們在晶圓上有18千兆位的SRAM。也許這對今天的某些型號來說已經足夠了,但明天和后天的型號呢?“

什么時候出來?

據“財富”雜志報道,Cerebras9月份將會向客戶發貨首批系統。據EE Times稱,部分系統已經收到原型。該公司計劃在11月的超級計算大會上公布完整系統的結果。

-

處理器

+關注

關注

68文章

19801瀏覽量

233519 -

芯片

+關注

關注

459文章

52160瀏覽量

436061 -

晶體管

+關注

關注

77文章

9978瀏覽量

140642

原文標題:對于這顆有史以來最大的芯片,這六點你需要知道!

文章出處:【微信號:icbank,微信公眾號:icbank】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

扇出型晶圓級封裝技術的工藝流程

一次消諧裝置與二次消諧裝置區別、一次消諧器與二次消諧器的區別

簽約頂級封裝廠,普萊信巨量轉移技術掀起晶圓級封裝和板級封裝的技術革命

AMC1210對AMC1305進行數字抽取濾波,輸出后的數據是否需要用處理器進行一次平均和移位處理?

盛顯科技:投影融合處理器連接出現超時,該怎么辦?

業界再一次出現對晶圓級處理器的商業嘗試

業界再一次出現對晶圓級處理器的商業嘗試

評論