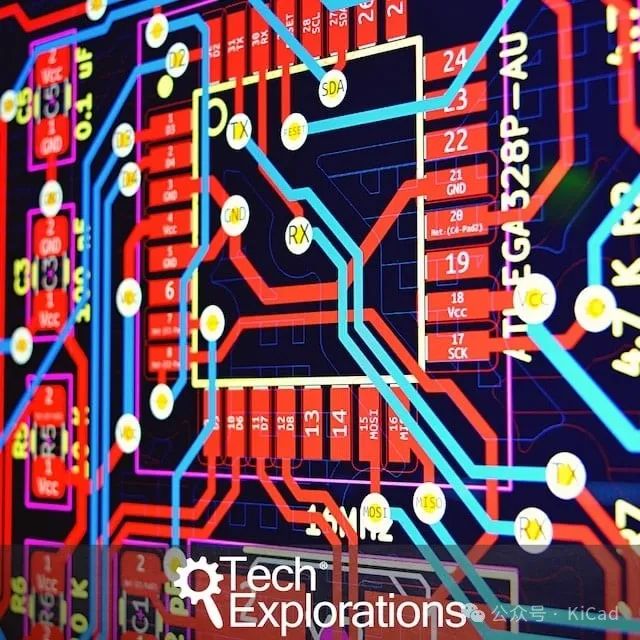

盡管以比并行接口快得多的速度運行,SERDES總線往往更容易實現,因為需要克服一組特定的問題。只要SERDES接口的高級架構是合理的,SERDES總線的成功實現就歸結為“實現細節”。這些細節通常必須通過手動檢查布線板進行驗證,但是自動檢測方法,通過使用設計規則檢查(DRC)促進了這一點,可以使審查SERDES總線的任務變得更加容易。以下是DRC有用的示例:

針對差分阻抗

SERDES總線采用差分走線布線,需要針對特定的差分阻抗。目標阻抗通常為100歐姆差分,但85和90歐姆差分的值也很常見。必須沿著路徑保持這種差分阻抗,以最小化反射并最大化接收器處眼圖中的開口。阻抗不連續性可以以過孔的形式出現(稍后將詳細介紹),芯片分支區域中的縮頸,用于保持長度匹配的調整循環,或者目標跡線寬度和/或間距發生變化的任何位置。

如果目標走線寬度和/或間距發生變化,可能會出現芯片突破區域和調諧環路中的頸縮等阻抗不連續性。

-

PCB打樣

+關注

關注

17文章

2971瀏覽量

22349 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28435 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43734

發布評論請先 登錄

什么是SerDes?SerDes有哪些應用?

SERDES PCB布局的設計怎樣規則的檢查

SERDES PCB布局的設計怎樣規則的檢查

評論