設計規則檢查(Design Rule Check,簡稱DRC)是芯片設計中的一個關鍵步驟,旨在確保電路設計的物理布局符合制造工藝的要求。可以把它類比為建筑設計中的檢查流程,確保建筑圖紙中的所有尺寸和結構符合建筑標準,否則建造出來的建筑可能會有安全隱患或不符合使用要求。類似地,DRC 就是對芯片設計的物理版圖進行檢查,確保其符合生產廠商的工藝規則。

1、DRC的作用:

DRC 的主要作用是驗證芯片版圖中的各種物理設計是否符合制造過程中的工藝限制。芯片制造涉及微小的尺寸和精密的制造工藝,如果設計不符合這些規則,可能會導致芯片在生產過程中無法正確制造,甚至無法正常工作。

2、DRC的工作原理:

DRC 會對芯片設計中的每個物理元素(如線路、元器件、接觸點等)進行檢查,確保它們的尺寸、間距和布局符合以下要求:

線路寬度:芯片上的電線(連線)不能太窄,必須達到制造工藝要求的最小寬度。如果過窄,電流可能會不穩定,甚至導致電路短路。

線路間距:電路中的不同線路之間必須有足夠的間距,以避免它們之間發生短路或干擾。間距過小可能導致信號干擾,影響芯片功能。

過孔和接觸點:在不同層次之間需要通過過孔連接電路,過孔的尺寸和位置也必須符合規則。接觸點(例如電源和地線的接觸點)也必須符合最小尺寸和間距要求。

層間對齊:芯片設計有多個層,每層都要有明確的對齊規則。DRC 會檢查這些層是否正確對齊,確保信號能準確通過每一層。

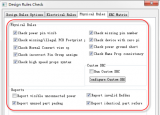

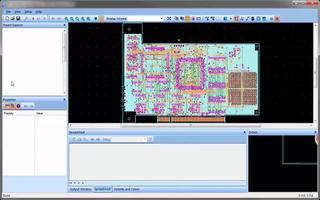

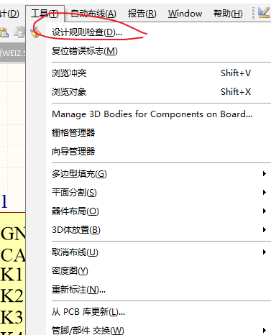

3、DRC檢查的具體步驟:

規則設置:設計工程師需要根據所使用的制造工藝來設置DRC規則。例如,不同的工藝(如14nm、7nm工藝)有不同的規則。

規則應用:DRC 工具會自動將這些規則應用到芯片的版圖設計中,逐一檢查每個物理元素是否符合規定。

檢查報告:如果版圖設計存在違反規則的地方,DRC 工具會生成一個報告,指出哪些地方存在問題,并給出解決方案。這些問題可能是某條線路太細、兩條線路間距太小,或者過孔的位置不正確等。

4、DRC的優化:

通過 DRC 檢查,設計工程師可以發現并修復設計中的問題,確保版圖能夠順利通過制造環節。這不僅能避免生產中的錯誤,還能提高芯片的可靠性和性能。

優化版圖:設計師可以根據 DRC 提供的反饋,調整電路的布局、尺寸、間距等,使設計符合工藝規則。

減少制造失敗:DRC 可以有效避免制造過程中的故障,降低返工率,節省時間和成本。

5、DRC與其他檢查的關系:

除了 DRC,芯片設計中還會進行其他類型的檢查,如:

LVS(Layout Versus Schematics)一致性檢查:檢查版圖設計是否與原理圖一致,確保電路功能沒有錯誤。

STA(Static Timing Analysis)靜態時序分析:分析電路中的信號傳輸延遲,確保時序滿足要求。

后仿驗證:通過仿真驗證電路在實際工作中的表現。

6、DRC的重要性:

DRC 是芯片設計中的必要步驟,它可以有效地保證芯片設計的可靠性和制造可行性。通過 DRC,設計工程師能夠在早期發現問題,避免由于設計錯誤導致的生產失敗,減少生產成本,提高產品質量。沒有 DRC 檢查,芯片設計很可能在生產過程中出現嚴重問題,甚至無法完成制造。

●總結●

DRC(設計規則檢查)是芯片設計中的一項重要步驟,確保設計符合制造工藝的限制,避免因不合規設計而導致生產失敗。通過 DRC 工具,設計師能夠自動檢查版圖中的尺寸、間距、過孔等是否符合要求,確保芯片的穩定性和可靠性。在現代集成電路設計中,DRC 是芯片成功制造和高效生產的關鍵環節之一。

直接轉載來源:老虎說芯。

-

元器件

+關注

關注

113文章

4807瀏覽量

94273 -

芯片設計

+關注

關注

15文章

1062瀏覽量

55449 -

DRC

+關注

關注

2文章

153瀏覽量

36916

原文標題:想在芯片設計領域突圍?先攻克設計規則檢查(DRC)這道難關

文章出處:【微信號:gh_454737165c13,微信公眾號:Torex產品資訊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

altium designer規則檢查問題

編寫PCB設計規則檢查器技巧

編寫屬于自己的PCB設計規則檢查器

【硬件電路】AltiumDesigner18規則檢查含義

PCB設計電氣規則檢查器解決DRC問題

分享PCB布線設計規則檢查?分析

pcb規則檢查怎樣檢查

orcad物理規則檢查的含義是什么

AD學習問題記錄(二):pcb設計規則檢查報錯Silk To Solder Mask Clearance Constraint

芯片設計中的設計規則檢查

芯片設計中的設計規則檢查

評論