最新的電子產品通常需要三個獨立的設計流程 - 芯片,封裝和PCB - 這些產品在單個封裝中使用越來越復雜的片上系統(SoC)和多個芯片。今天,這三個過程通常使用點工具執行,這些點工具需要耗時且容易出錯的手動過程來鏈接這三個過程。但是,通過考慮每個設計決策的系統級影響,集成的3D芯片/封裝/電路板協同設計環境能夠以比過去更大的程度全面優化封裝,電路板和IC設計。設計人員可以通過引腳分配和I/O布局優化可路由性,以最大限度地減少封裝,芯片和電路板之間的層數。新方法可以在更短的時間內將更多功能性,更高性能和更便宜的產品推向市場。

限制傳統的設計方法

傳統的系統設計依賴于在獨立環境中處理IC,封裝和PCB的工具。這些流程缺乏系統級規劃,可視化,設計和分析。規劃中使用的設計數據庫不能與用于審查和分析的數據庫互操作,因此很難保證在規劃期間做出的決策能夠貫穿最終產品。在傳統的2D組件專用設計工具中,協同設計具有挑戰性,因為設計人員通常只能看到自己的組件。用于在這些環境之間交換數據的文件交換格式通常是過時的和缺陷的,缺少有用的設計數據或者是專有的并且沒有廣泛支持。傳統流程中不存在工具來集成系統的所有組件并維護電氣和機械數據庫信息,從而提供可實現的協同設計環境。

過去這種方法是可以接受的,因為大多數復雜的系統都有大的外形(服務器,PC塔,大型機械),封裝和基板成本在整個系統成本中可以忽略不計。隨著功能的增加,成本的限制以及當今產品(便攜式設備,可穿戴設備和汽車)的外形尺寸的減小,組件需要彼此緊密協調,以便針對小尺寸和最小層數基板優化引腳分配。/p>

由于缺乏工具集成,但設計要求不斷增加,公司已恢復使用電子表格和通用辦公生產力工具來執行規劃和可行性研究以及定義工具界面和數據傳輸等變通方法。這些文件通常是內部開發的,必須在內部進行維護并手動操作以與流程中的工具進行交互。由于EDA工具的限制性文件輸入格式,它們受到所提供信息的限制。它們會遇到諸如無法與最終設計輸出數據自動關聯的設計規劃數據以及僅限于簡單信息(如基本網絡和位置信息)的引腳分配數據等問題。由于缺乏中央設計環境以及對系統數據使用手動反饋機制,引腳,I/O,布局布線的元件間優化是不可行的。

PCB產品設計供應商已開始介紹利用傳統數據庫來降低開發成本的工具來應對這些挑戰。然而,由于傳統數據庫結構所施加的不靈活性,這些新工具僅限于2D環境或一個封裝和一個PCB。需要在2D和3D視圖之間來回切換需要在傳統2D設計數據庫和較新的3D查看器數據庫之間進行文件轉換,這會減慢設計過程,增加翻譯準確度的不確定性并限制設計洞察力。

隨著產品外形尺寸的縮小,需要使用機械設計的外殼檢查ECAD設計尺寸,并考慮外殼進行多物理分析。隨著外殼越來越多地從正交移動到更緊湊,更復雜的彎曲形狀,需要3D視圖,因為2D視圖過于嚴格并且不能準確地表示系統。傳統流程將ECAD和MCAD設計分開,幾乎沒有交叉流分析的機會。 MCAD流程中的電子行業特定設計自動化由于其通用性而難以實現。

系統級3D協同設計的出現

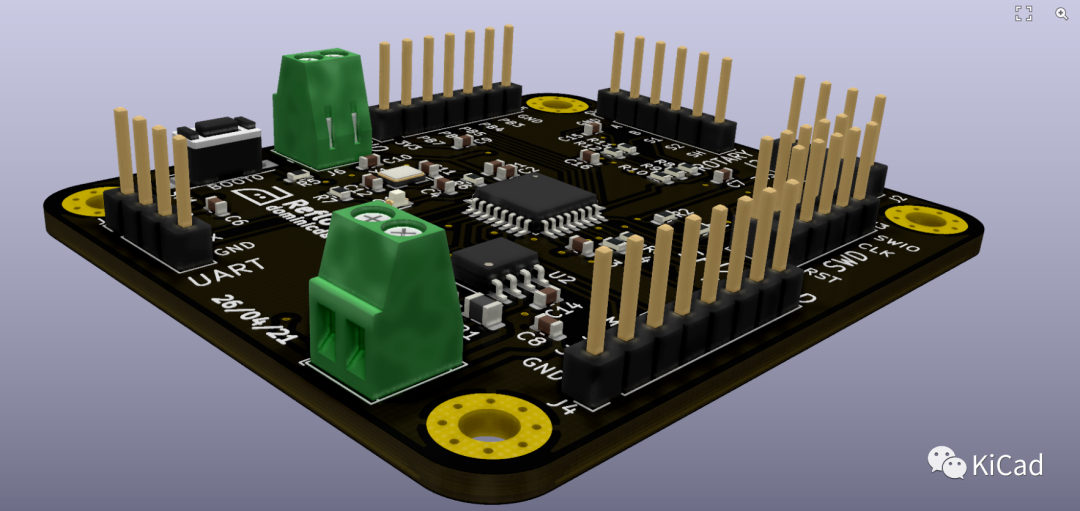

新一代系統級3D協同設計工具通過提供集成的系統設計環境來應對這些挑戰系統級以及PCB,IC和機械外殼的規劃和最終設計。這些數據庫被放在一個視圖中,因此每個參與項目的人都可以在完整產品的上下文中看到他們的謎題。工程師可以在單個用戶界面中進行系統級設計,完整封裝設計,完整PCB設計,插入器設計,并優化ICL設計的RDL(再分布層)布線和裸片放置。可以根據最終的ECAD外形尺寸(PCB,封裝和IC)尺寸檢查機械外殼設計,以確保安裝和間隙。集成的制造設計工具使得可以在布局期間驗證設計到供應商技術特定的制造和裝配制造檢查。可以自動生成文檔以進行簽核和制造。與多物理分析工具集成的按鈕確保設計數據的高效快速傳輸,實現快速周轉。

Co - 使用RDL和封裝扇出逃生路由設計IC和封裝

這種集成的協同設計環境允許在離散或有限的2D工具中無法使用獨特的設計方法。例如,工程師可以在單一設計視圖中考慮IC側的RDL和PCB側的逃逸路徑,對不同數量的封裝層進行可行性研究。能夠對芯片和封裝進行系統級協同設計,可以優化凸點和焊球布局,I/O布局和引腳分配,從而降低芯片,封裝和PCB層數,即使在具有布線復雜性的非傳統結構中也是如此在垂直方向上,如PoP,SiP,芯片級封裝和3DIC/3D封裝。芯片RDL和封裝逃逸的自動布線允許快速尋路可行性,改善完成時間并允許用戶優化裸片放置。其優勢包括減少RDL,插入器/基板和封裝層數量,同時優化信號性能并縮短出帶時間。

PCB設計(頂部)和封裝設計(底部)之間的實時交換,以提高可布線性和性能

查看IC,封裝和PCB同時在一個視圖中幫助工程師優化引腳分配并避免連接錯誤,從而縮短設計時間。如果設計人員需要執行封裝/IC凸點分配,他或她可以在PCB級別查看對鼠巢的影響。或者,如果設計人員必須在電路板級進行自動或交互式引腳交換以提高PCB布線性,他或她可以觀察封裝和IC級別的潛在影響。引腳交換操作在封裝和PCB數據庫之間自動傳遞,無需CSV或其他中性文件來傳達更改。該工具還允許多個工程師在單個基板上工作,同時保護其他工程師的編輯。如果設計人員需要在鎖定的包裝設計中進行引腳交換,他或她可以發送通知,其他工程師可以接受或拒絕作為ECO。

智能PoP和SiP設計

使用該技術,可以將多個IC導入協同設計環境并連接在一起。 3D,多設計環境更智能地管理復雜包(如PoP和SiP)的路由相互依賴性。這種新方法通過實時3D設計為SiP提供重點設計規則檢查,并支持堆疊LSI的復雜鍵合線放置。工程師可以使用共同設計環境來確保鍵合線在任何角度滿足間距要求,并且3D鍵合線輪廓符合制造規范。

使用TSV管理復雜的2.5/3D IC設計

這種新方法極大地改善了基于TSV的設計(如3DIC)的布局規劃和布線堆疊芯片和硅中介層。工程師可以導入現有數據庫(來自OpenAccess,GDS或LEF/DEF文件)或使用設計環境生成TSV。可以使用導入或手動生成的制造和設計規則來執行自動或手動路由。預放置的TSV可以自動布線,而未放置的TSV可以放置和布線。 3D環境支持大型數據集,并允許設計人員查看復雜的轉義和路由結構

通過集成信號和電源完整性分析驗證信號性能

隨著系統任何級別的變化,設計人員可以從信號完整性,電源完整性或散熱角度查看效果。多學科,多物理分析可以使用Keysight Technologies,ANSYS,AWR,CST和Synopsys等解決方案提供商提供的一流解決方案。協同設計環境可在整個系統中實現信號可追溯性。可以檢查和分析信號路徑,因為它們跨越設計和組件邊界,從驅動器到系統互連到接收器。智能和集成的基于原理圖或布局的仿真環境支持多種設計流程。

結論

芯片/封裝/電路板協同設計提供了統一的設計方法,使設計人員能夠考慮每個設計決策的系統級影響,從而降低設計成本,提高性能,減少不確定性并加快進度。設計人員可以同時考慮IC/封裝/PCB問題,以設計具有最佳信號性能的良好集成產品,同時減少RDL,插入器/基板和封裝層數量,從而降低成本和出帶時間。

-

PCB打樣

+關注

關注

17文章

2977瀏覽量

22380 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28464 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43774

發布評論請先 登錄

2.5D/3D封裝技術升級,拉高AI芯片性能天花板

芯片3D堆疊封裝:開啟高性能封裝新時代!

SciChart 3D for WPF圖表庫

3D芯片/封裝/ PCB協同設計優化系統怎樣操作

3D芯片/封裝/ PCB協同設計優化系統怎樣操作

評論