本文主要介紹Matlab如何實現(xiàn)移位寄存器,首先介紹的是移位寄存器的原理及作用,其次介紹了m序列的生成原理及m序列的matlab 仿真實現(xiàn),最后介紹了Matlab如何實現(xiàn)移位寄存器的代碼。

2018-04-26 09:28:05 15788

15788

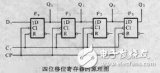

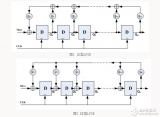

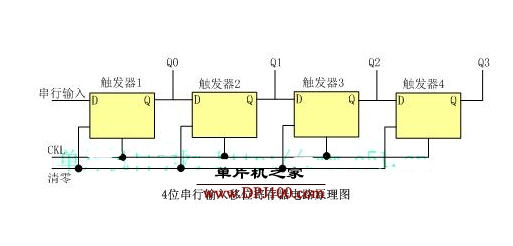

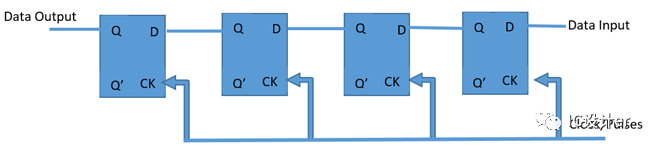

串行輸入,串行輸出移位寄存器每級將數(shù)據(jù)延遲一個時鐘時間。它們將為每個寄存器存儲一點數(shù)據(jù)。串行輸入,串行輸出移位寄存器的長度可能為一到64位,如果級聯(lián)寄存器或封裝,則長度會更長。下面是一個單級

2020-10-08 08:39:07

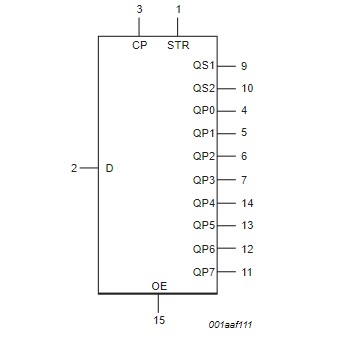

沿輸入到移位寄存器中,在ST_CP(存儲器時鐘輸入)的上升沿輸入到存儲寄存器中去。如果兩個時鐘連在一起,則移位寄存器總是比存儲寄存器早一個脈沖。移位寄存器有一個串行移位輸入(DS),和一個串行輸出(Q7’),和一個異步的低電平復(fù)位,存儲寄存器有一個并行8位的,具備三態(tài)的總線輸出,當使能OE時(

2021-12-07 06:38:53

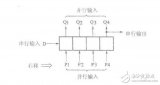

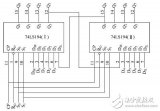

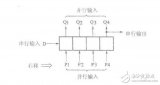

轉(zhuǎn)換電路之后變換成并行輸出。圖7-3是用二片CC40194(74LS194)四位雙向移位寄存器組成的七位串/并行數(shù)據(jù)轉(zhuǎn)換電路。 電路中S0端接高電平1,S1受Q7控制,二片寄存器連接成串行輸入右移工作

2019-06-20 04:20:29

移位寄存器及其應(yīng)用15號實驗臺移位寄存器移位寄存器及其應(yīng)用一、實驗?zāi)康亩?實驗原理實驗器件:三、實驗內(nèi)容四、思考題一、實驗?zāi)康?、進一步掌握時序邏輯電路的設(shè)計步驟和方法;2、熟悉和了解移位寄存器

2021-07-30 06:43:27

輸入數(shù)據(jù)時,先得把CLK腳的電位拉低,輸入一位數(shù)據(jù)后,再把CLK的電位拉高,此時則產(chǎn)生了一個時鐘上升沿,使數(shù)據(jù)被載入,此時用代碼表示為(注意:通過時序圖可知,CS為低電平時串行數(shù)據(jù)才會被載入移位寄存器...

2022-03-02 06:17:11

移位寄存器應(yīng)用案例

2019-03-28 08:23:11

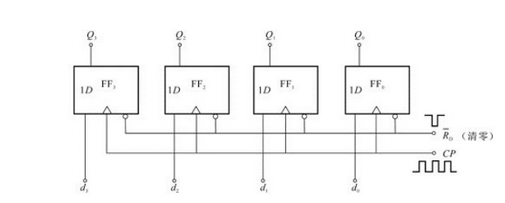

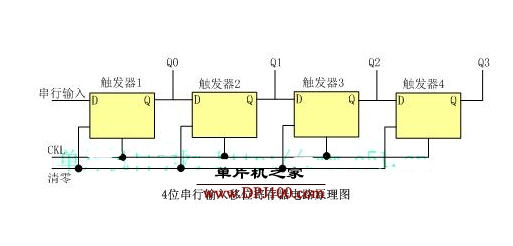

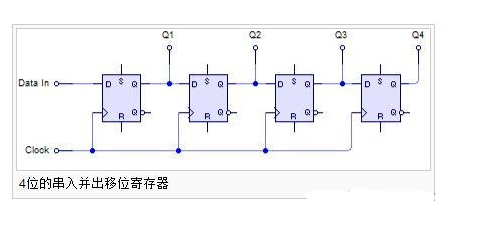

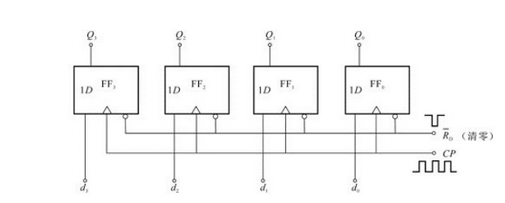

寄存器。這說明存入該寄存器中的數(shù)碼也可以從Q端串行輸出。根據(jù)需要,可用更多的觸發(fā)器組成多位移位寄存器。 除了用邊沿D 觸發(fā)器外,還可用其他類型的觸發(fā)器來組成移位寄存器,例如,用主從JK 觸發(fā)器來組成

2019-06-20 04:20:47

請問labview中移位寄存器如何初始化?看到一個程序,為什么移位寄存器左側(cè)沒有連線,卻被初始化,確定了寄存器中的數(shù)據(jù)結(jié)構(gòu)。

2016-06-15 21:05:55

串行輸入,串行輸出移位寄存器每級將數(shù)據(jù)延遲一個時鐘時間。它們將為每個寄存器存儲一點數(shù)據(jù)。串行輸入,串行輸出移位寄存器的長度可能為一到64位,如果級聯(lián)寄存器或封裝,則長度會更長。下面是一個單級

2020-09-24 09:33:07

`怎么在使用完移位寄存器里面的值以后清空寄存器等待下次累積,因為如果每次使用后不去清空移位寄存器,移位寄存器里面的值就會繼續(xù)不斷的疊加。請大神們指點指點。`

2015-08-12 17:01:23

的移位寄存器可以實現(xiàn)這種功能。在循環(huán)結(jié)構(gòu)框左側(cè)或右側(cè)邊框單擊鼠標右鍵,在彈出的快捷菜單中選擇“添加移位寄存器”,添加移位寄存器,如圖1所示。 圖2和圖3分別顯示為For循環(huán)結(jié)構(gòu)和While循環(huán)結(jié)構(gòu)添加

2011-10-12 16:25:27

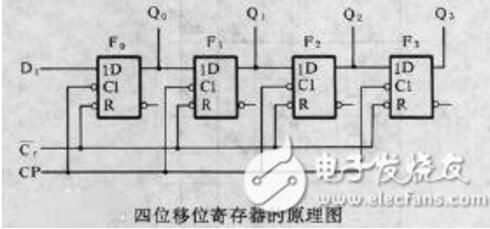

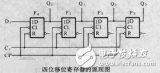

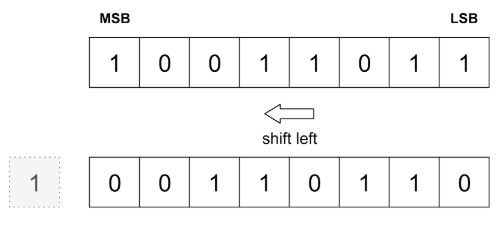

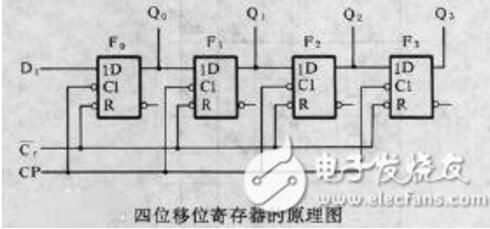

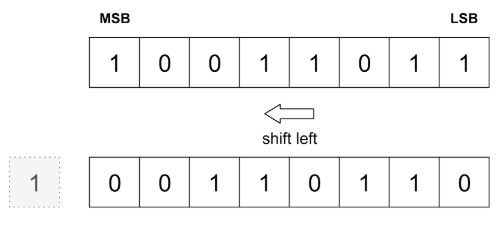

左邊一個觸發(fā)器中原來的數(shù)據(jù)(F0接收的輸入數(shù)據(jù)D1)。寄存器中的數(shù)據(jù)依次右移一位。 2、移位寄存器作用 移位寄存器是一種存儲器,存在里邊的數(shù)據(jù)可以從低位向高位移動或從高位向低位移動。例如一個8位

2019-06-20 04:20:27

題目是用阻塞賦值描述一個4級串行同步移位寄存器,串行輸入數(shù)據(jù)位寬為8bit我想問“4級串行”是什么意思?還有后面,串行輸入可以輸入8位的嗎?

2012-12-03 22:20:47

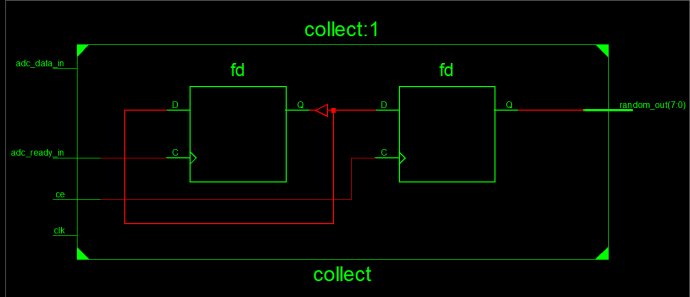

到FPGA片內(nèi)的存儲器資源來實現(xiàn)移位寄存器的功能。使用片內(nèi)存儲器實現(xiàn)移位寄存器的接口如圖12.11所示,其可配置的參數(shù)有:一個位寬為w的移位輸入數(shù)據(jù)和相同位寬的移位輸出數(shù)據(jù),一個輸入時鐘信號(圖中未示意)作為

2017-01-15 17:13:42

我想請教一下怎么用移位寄存器計算最后三次測量的算術(shù)平均值?

2012-10-21 14:03:32

非常實用的基于VHDL的移位寄存器實驗

2023-09-25 08:06:51

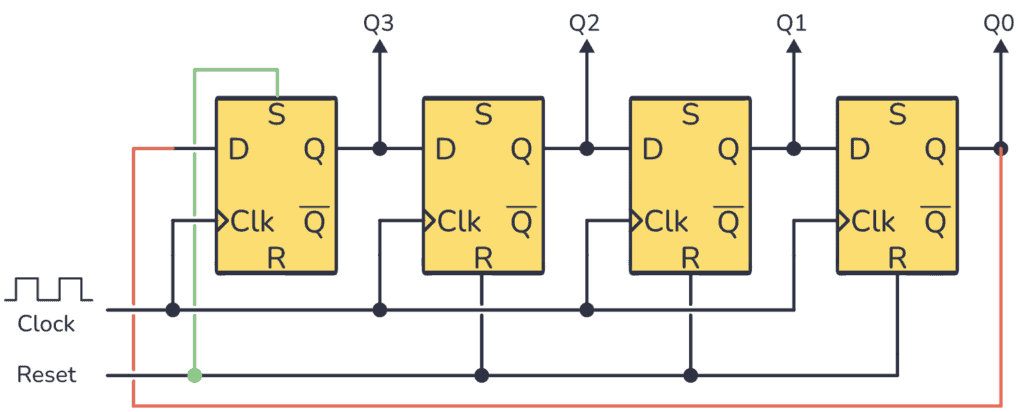

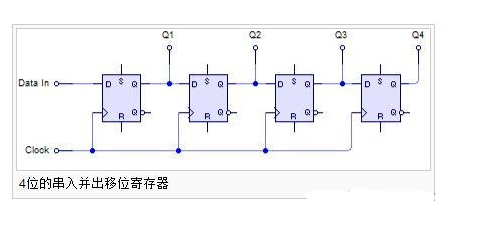

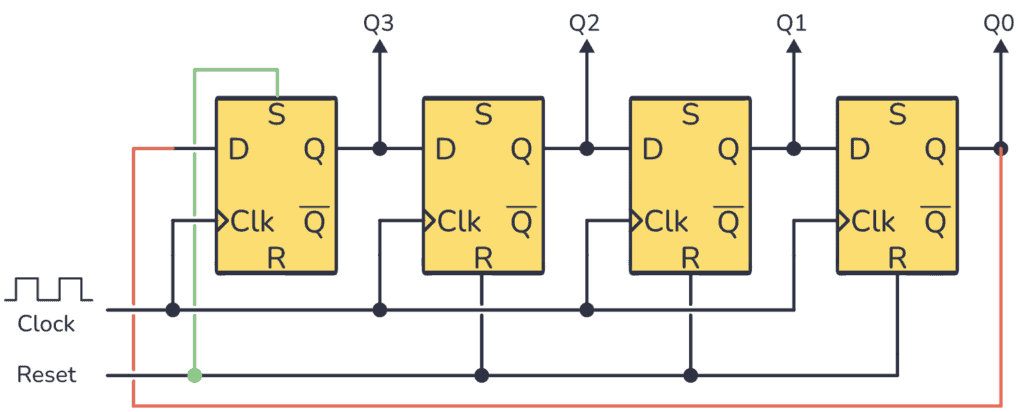

用D觸發(fā)器設(shè)計的四位移位寄存器

2016-06-13 13:05:50

大家好,我試圖用多個移位寄存器(6)來驅(qū)動15個RGB LEDS。如果我使用一個移位寄存器,代碼工作正常,但是使用多個移位寄存器有困難。首先我檢查電路,但是看起來不錯,串行輸出連接到por中的每個

2020-03-26 08:59:22

labview中,移位寄存器的原理以及應(yīng)用的,,,怎么說呢、?就是感覺移位寄存器怎么用的一點頭緒都沒有,,求大神分析分析,,講解講解

2014-12-12 20:44:25

移位寄存器的串行擴展技術(shù) 何立民教授一 80C51 UART 方式0 的歸一化子程序1 80C51 方式0 的工作原理與時序80C51 UART 方式0 的時序如圖1 所示RXD P3.0 為數(shù)據(jù)端TXD P3.0 為同步移位脈

2008-09-22 11:10:47 27

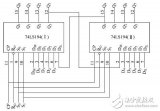

27 實驗七四位雙向移位寄存器一、實驗?zāi)康?. 移位寄存器74LS194 的邏輯功能及使用方法。2. 熟悉4 位移位寄存器的應(yīng)用。二、實驗預(yù)習要求1. 了解74LS194 的邏輯功能。2.

2009-03-16 19:19:12 0

0 實驗七 集成移位寄存器一、 實驗?zāi)康?、 掌握集成雙向移位寄存器74LS95的邏輯功能2、 熟悉集成雙向移位寄存器74LS95的管腳排列二、 實驗器材實驗箱、

2009-03-20 17:54:05 19

19 一、 實訓目的1.掌握移位寄存器74LS194的邏輯功能及其測試方法;2.熟悉移位寄存型的典型應(yīng)用電路。二、實訓內(nèi)容1.移位寄存器74LS194的功能測試;2.74LS194構(gòu)

2009-06-27 09:47:21 72

72 寄存器與移位寄存器

寄存器是用來寄存數(shù)碼的邏輯部件,所以必須具備接收和寄存數(shù)碼的功能。任何一種觸發(fā)器都可以構(gòu)成寄存器,每一個觸發(fā)器存放一位二進

2010-03-12 15:19:40 59

59 描述 TLC6C598-Q1是一款單芯片、中壓、低電流、8位移位寄存器,設(shè)計用于要求相對中等負載功率的系統(tǒng),如led。該器件包含一個8位串行輸入并行輸出移位寄存器,該寄存器為一個8位D型

2023-11-01 16:03:39

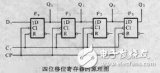

第二十六講 寄存器和移位寄存器7.4.1 寄存器1.定義2.電路舉例 3.邏輯功能分析7.4.2 移位寄存器一、單向移位寄存器㈠ 由4個維持阻塞D觸發(fā)器組成4位右移

2009-03-30 16:30:09 8922

8922

移位寄存器電路圖

2009-04-02 08:56:46 1644

1644

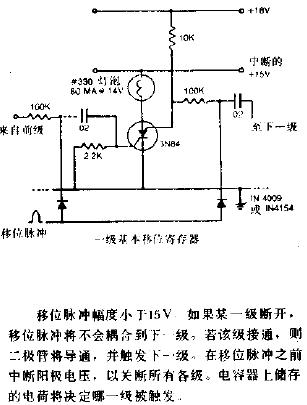

可越位的移位寄存器

2009-04-10 10:24:34 431

431

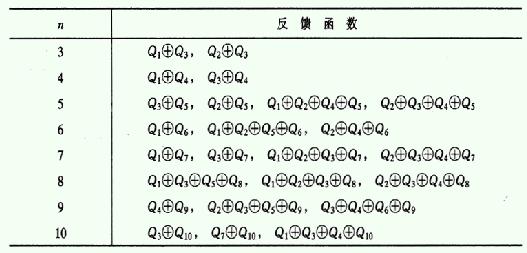

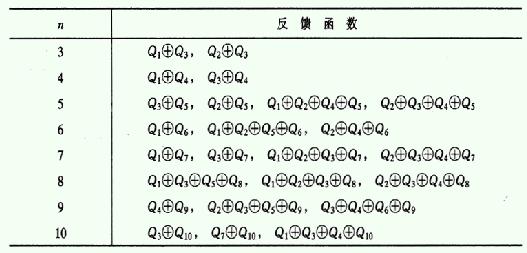

線性移位寄存器

用移位寄存器可以構(gòu)成序列信號發(fā)生器,其電路結(jié)構(gòu)如下圖所示。組合電路從移位寄存器取得信息,產(chǎn)生反饋信號加

2010-01-12 14:14:11 1740

1740

移位寄存器,移位寄存器是什么意思

移位寄存器_

2010-03-08 14:50:31 17083

17083 移位寄存器的工作原理是什么?

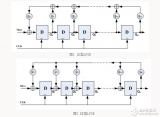

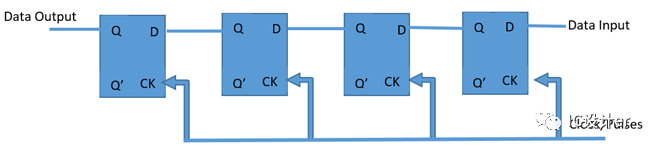

把若干個觸發(fā)器串接起來,就可以構(gòu)成一個移位寄存器。由4個邊沿D 觸發(fā)器構(gòu)成的4位移位寄存器邏輯電路如圖8.8.1所示。數(shù)據(jù)從串行輸入

2010-03-08 14:55:44 1625

1625 移位寄存器的工作原理是什么?

把若干個觸發(fā)器串接起來,就可以構(gòu)成一個移位寄存器。由4個邊沿D 觸發(fā)器構(gòu)成的4位移位寄存器邏輯電路如圖8.8.1所示。數(shù)據(jù)從串行輸入

2010-03-08 14:56:55 44087

44087 一、實驗?zāi)康?1、了解集成移位寄存器的控制功能。 2、掌握集成移位寄存器的應(yīng)用。 二、實驗原理 移位寄存器的功能是當時鐘控制脈沖有效時,寄存器中存儲的數(shù)碼同時順序向高位(

2012-07-16 22:59:58 22

22 寄存器與移位寄存器:介紹寄存器原理和移位寄存器的原理及實現(xiàn)。

2016-05-20 11:47:38 0

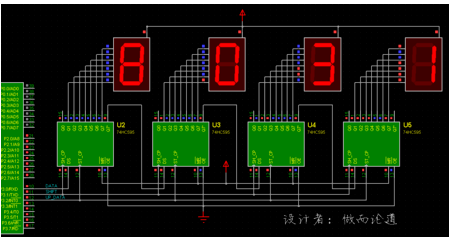

0 74HC595是一顆高速CMOS 8位3態(tài)移位寄存器/輸出鎖存器芯片,采用CMOS硅柵工藝。該器件包含一個8位串行輸入與并行輸出移位寄存器并提供一個8位D型存儲寄存器,該存儲寄存器具有8位3三態(tài)輸出

2016-07-12 11:54:40 14

14 可以定義移位長度的移位寄存器。就是用一個lut可以實現(xiàn)16位的移位寄存器。

2017-02-11 11:24:08 6869

6869

在數(shù)字電路中,移位寄存器(英語:shift register)是一種在若干相同時間脈沖下工作的以觸發(fā)器為基礎(chǔ)的器件,數(shù)據(jù)以并行或串行的方式輸入到該器件中,然后每個時間脈沖依次向左或右移動一個比特,在輸出端進行輸出。這種移位寄存器是一維的,事實上還有多維的移位寄存器。

2017-07-21 17:15:41 162375

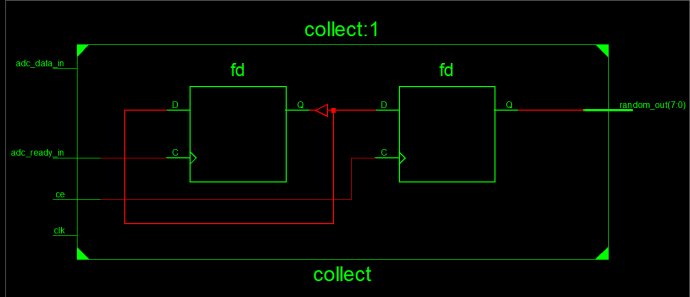

162375 線性反饋移位寄存器(LFSR)是一個產(chǎn)生二進制位序列的機制。這個寄存器由一個初始化矢量設(shè)置的一系列信元組成,最常見的是,密鑰。這個寄存器的行為被一個時鐘調(diào)節(jié)。

2017-12-22 09:37:35 46606

46606

本文以移位寄存器為中心,主要介紹了移位寄存器的特點、移位寄存器原理。以及詳細的說明了移位寄存器實驗報告。

2017-12-22 14:29:05 27206

27206

本文以移位寄存器為中心,主要介紹了移位寄存器原理、移位寄存器特點、移位寄存器分類、移位寄存器作用以及移位寄存器的應(yīng)用。

2017-12-22 14:44:12 82198

82198

目前移位寄存器在電路中已經(jīng)得到普遍使用。本文以移位寄存器為中心。主要介紹了移位寄存器分類、移位寄存器的特點,以及詳細的說明了移位寄存器的工作原理。

2017-12-22 15:20:44 46140

46140

移位寄存器是一個具有移位功能的寄存器,是指寄存器中所存的代碼能夠在移位脈沖的作用下依次左移或右移。本文主要介紹了移位寄存器的用途以及移位寄存器的用法詳解。

2017-12-22 15:49:03 19126

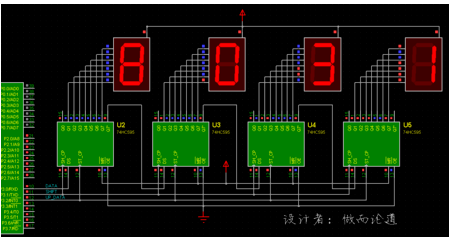

19126 ,常用于數(shù)碼變換、串行一并行碼變換,計數(shù)和數(shù)碼發(fā)生電路等,常應(yīng)用于計算機電路。74LS194是4位雙向移位寄存器,它具有并行輸入、并行輸出、左移和右移。用兩片4位雙向移位寄存器74LS194接成一個8位雙向移位寄存器。

2018-05-09 10:10:16 79693

79693

移位寄存器是基本的同步時序電路,基本的移位寄存器可以實現(xiàn)數(shù)據(jù)的串行/并行或并行/串行的轉(zhuǎn)換、數(shù)值運算以及其他數(shù)據(jù)處理功能。在本設(shè)計中,使用硬件描述語言Verilog,在EDA工具QuartussII

2018-10-24 17:30:40 6033

6033

14腳:DS(SER),串行數(shù)據(jù)輸入引腳 13腳:OE, 輸出使能控制腳,它是低電才使能輸出,所以接GND 12腳:RCK,存儲寄存器時鐘輸入引腳。上升沿時,數(shù)據(jù)從移位寄存器轉(zhuǎn)存帶存儲寄存器。 11

2019-09-27 17:15:00 3

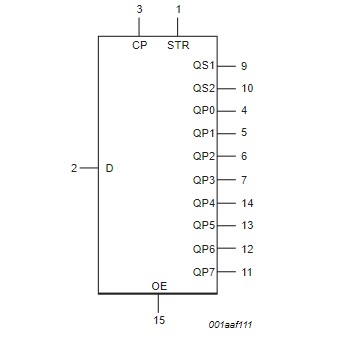

3 HEF4094B是一個8階段的串行移位寄存器。它有一個存儲鎖存器關(guān)聯(lián)的模擬階段,用于將從串行輸入到并行緩沖的3態(tài)輸出QP0到QP 7之間的數(shù)據(jù)排序。

2019-05-13 16:24:45 10761

10761

移位寄存器按照不同的分類方法可以分為不同的類型。 如果按照移位寄存器的移位方向來進行分類, 可以分為左移移位寄存器、移位寄存器和雙向移位寄存器等;如果按照工作方式來分類,可以分為串入/串出移位寄存器、串入/并出移位寄存器和并入/串出移位寄存器等。

2019-07-15 09:38:51 71381

71381

移位寄存器是由相同的寄存單元所組成。一般說來,寄存單元的個數(shù)就是移位寄存器的位數(shù)。為了完成不同的移位功能,每個寄存單元的輸出與其相鄰的下一個寄存單元的輸入之間的連接方式也不同。

2019-07-15 09:52:03 14507

14507

并入串出形式的移位寄存器接法,通過下圖所示D1-D4并行輸入段接收4位外部并行數(shù)據(jù),而Q為串行輸出的引腳。為了將數(shù)據(jù)寫入到寄存器中,寫/移位控制線必須保持低電平。寫入完成,需要移位時,寫/移位控制線則必須處于高電平,而且必須給予時間脈沖,每提供一個時間脈沖,向左(或向右)移動一位。

2019-07-15 10:10:29 30504

30504

移位寄存器有不同的版本,可用于各種各樣的應(yīng)用程序。本文將向您介紹移位寄存器并說明它們的工作原理。此外,它還將解釋如何將它們用于將多條并行數(shù)據(jù)線轉(zhuǎn)換為單個串行連接。

2019-07-30 14:19:05 41305

41305

74HC595;74HCT595是8級串行移位寄存器,具有存儲寄存器和3個狀態(tài)輸出。寄存器有單獨的時鐘。數(shù)據(jù)在移位寄存器時鐘輸入(SHCP)的正向轉(zhuǎn)換上移位在存儲寄存器時鐘輸入(STCP)正向轉(zhuǎn)換

2020-07-16 17:32:27 20

20 移位寄存器有一個串行移位輸入(Ds),和一個串行輸出(Q7’),和一個異步的低電平復(fù)位,存儲寄存器有一個并行8位的,具備三態(tài)的總線輸出,當使能OE時(為低電平),存儲寄存器的數(shù)據(jù)輸出到總線。

2020-09-01 17:20:34 10

10 串行輸入,串行輸出移位寄存器每級將數(shù)據(jù)延遲一個時鐘時間。 它們將為每個寄存器存儲一點數(shù)據(jù)。串行輸入,串行輸出移位寄存器的長度可能為一到64位,如果級聯(lián)寄存器或封裝,則長度會更長。 下面

2020-09-24 15:18:09 28404

28404

,編譯器直接把他綜合進了一個SRL16里面,也就是專用的移位寄存器模塊,只需要一個LUT就可以實現(xiàn)16bit以內(nèi)的移位 ? ? 這是不帶復(fù)位的資源,可以看到觸發(fā)器只用了一個,LUT也只用了一個,并且是作為存儲器用的,而且是作為存儲器里面的移位寄存器使用。 ?

2020-12-30 12:04:11 3314

3314 Labview while中的移位寄存器的創(chuàng)建和使用,移位寄存器就是while循環(huán)的變量

2020-11-11 17:26:22 50448

50448 輸出移位寄存器,它為8位D型存儲寄存器提供數(shù)據(jù)。存儲寄存器有8個3狀態(tài)輸出。移位寄存器和存儲寄存器都有單獨的時鐘。移位寄存器有一個直接覆蓋清除,串行輸入和串行輸出(標準)引腳級聯(lián)。移位寄存器和存儲寄存器都使用正邊緣觸發(fā)時鐘。如果兩個時鐘連接在一起,移位寄存器

2021-01-26 08:00:00 2

2 沿輸入到移位寄存器中,在ST_CP(存儲器時鐘輸入)的上升沿輸入到存儲寄存器中去。如果兩個時鐘連在一起,則移位寄存器總是比存儲寄存器早一個脈沖。移位寄存器有一個串行移位輸入(DS),和一個串行輸出(Q7’),和一個異步的低電平復(fù)位,存儲寄存器有一個并

2021-11-24 10:06:14 22

22 74HC595是一款低噪聲、低功耗、高速的COMS移位寄存器,能夠驅(qū)動15個LS-TTL的負載。

該器件包含一個8位串行輸入,并行輸出的移位寄存器及帶有三態(tài)輸出控制的8位D型存儲器。移位寄存器

2022-03-03 09:39:15 3

3 線性反饋移位寄存器(LFSR):通常由移位寄存器和異或門邏輯組成。其主要應(yīng)用在:偽隨機數(shù),偽噪聲序列,計數(shù)器,BIST,數(shù)據(jù)的加密和CRC校驗等。

2022-07-22 09:37:38 2789

2789 移位寄存器的功能和電路形式較多,按移位方向分有左移、右移、和雙向移位寄存器;按接收數(shù)據(jù)方式分為串行輸入和并行輸入;按輸出方向分為串行輸出和并行輸出。

2022-09-06 11:35:35 2983

2983 電子發(fā)燒友網(wǎng)站提供《使用移位寄存器開源分享.zip》資料免費下載

2022-10-27 14:17:59 6

6 GN595是一款低噪聲、低功耗、高速的COMS移位寄存器,能夠驅(qū)動15 個LS-TTL的負載。 該器件包含-一個8位串行輸入,并行輸出的移位寄存器及帶有三態(tài)輸出控制的8位D型存儲器。 移位寄存器

2022-12-29 16:27:42 0

0 電子發(fā)燒友網(wǎng)站提供《使用移位寄存器的方法.zip》資料免費下載

2023-01-30 16:31:13 2

2 8位并行輸入/串行輸出移位寄存器-74LV165_Q100

2023-02-08 19:20:10 0

0 8位并行輸入/串行輸出移位寄存器-74LV165

2023-02-08 19:20:20 0

0 AiP74HC/HCT595是一個8位串行輸入/串行或并行輸出移位寄存器,具有存儲寄存器和3個狀態(tài)輸出。移位寄存器和存儲寄存器都有單獨的時鐘。該設(shè)備具有串行輸入(DS)和串行輸出(Q7S),以實現(xiàn)

2023-02-13 16:53:16 0

0 8位靜態(tài)移位寄存器-HEF4021B_Q100

2023-02-15 18:44:09 1

1 8位靜態(tài)移位寄存器-HEF4021B

2023-02-15 18:44:38 0

0 雙4位靜態(tài)移位寄存器-HEF4015B

2023-02-15 18:47:33 0

0 8位靜態(tài)移位寄存器-HEF4014B_Q100

2023-02-15 18:48:52 0

0 8位靜態(tài)移位寄存器-HEF4014B

2023-02-15 18:49:03 0

0 8位串行輸入/串行輸出或并行輸出移位寄存器;三態(tài)-74LVC595A

2023-02-15 18:50:48 0

0 8位串行輸入/串行輸出或并行輸出移位寄存器;三態(tài)-74LV595

2023-02-15 19:17:10 1

1 帶輸出鎖存器的 8 位串行輸入、串行或并行輸出移位寄存器;3 - 狀態(tài)-74HC_HCT595

2023-02-15 19:35:46 0

0 8位并行輸入/串行輸出移位寄存器-74HC_HCT165

2023-02-15 19:44:36 1

1 8 位串行輸入、并行輸出移位寄存器-74HC_HCT164

2023-02-15 19:44:52 0

0 8位并行輸入/串行輸出移位寄存器-74HC_HCT166

2023-02-15 19:59:16 1

1 8位并行輸入/串行輸出移位寄存器-74HC_HCT166_Q100

2023-02-15 19:59:29 0

0 8位串行輸入/并行輸出移位寄存器-74LV164_Q100

2023-02-17 19:29:59 0

0 帶輸出鎖存器的 8 位串行輸入/串行輸出或并行輸出移位寄存器-74VHC_VHCT595

2023-02-17 20:02:07 0

0 8 位串行輸入、并行輸出移位寄存器-74HC_HCT164_Q100

2023-02-17 20:06:26 0

0 8位串行輸入/并行輸出移位寄存器-74AHC_AHCT164_Q100

2023-02-17 20:07:12 0

0 8位串行輸入/并行輸出移位寄存器-74AHC_AHCT164

2023-02-17 20:07:27 0

0 帶輸出鎖存器的 8 位串行輸入/串行輸出或并行輸出移位寄存器-74AHC_AHCT595

2023-02-20 18:43:49 0

0 8位并行輸入/串行輸出移位寄存器-74LV165A_Q100

2023-03-03 19:26:14 0

0 8位并行輸入/串行輸出移位寄存器-74LV165A

2023-03-03 19:26:33 4

4 74164和74595功能相仿,都是8位串行輸入轉(zhuǎn)并行輸出移位寄存器。

2023-03-15 17:16:12 0

0 移位寄存器是數(shù)字電子學中的常見構(gòu)建模塊,用于存儲和移動位,例如,從串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù),反之亦然。

2023-06-29 11:21:08 4416

4416

移位寄存器可用于各種電路。例如,如果您稍微修改串行輸入 – 并聯(lián)輸出移位寄存器,則可以創(chuàng)建一個環(huán)形計數(shù)器電路,如下所示:

2023-06-29 11:24:07 757

757

移位寄存器在一條線上接收傳輸?shù)?位和8位信號,并一一發(fā)送出去。反之亦然,它的作用是將海量的數(shù)據(jù)分揀到每一位,進行轉(zhuǎn)換和傳輸數(shù)據(jù),移位寄存器允許高速傳輸大量信號而無需大量布線。在本文中將解釋此類移位寄存器。

2023-07-07 10:50:27 1548

1548 移位寄存器是一種時序邏輯電路,能夠存儲和傳輸數(shù)據(jù)。它們由觸發(fā)器組成,這些觸發(fā)器的連接方式使得一個觸發(fā)器的輸出可以作為另一個觸發(fā)器的輸入,具體取決于所創(chuàng)建的移位寄存器的類型。

2023-09-20 10:44:13 2473

2473

LabVIEW中的移位寄存器(Shift Register)是一種用于存儲和移動數(shù)據(jù)的功能性塊。它類似于傳統(tǒng)計算機中的寄存器,可以用于在循環(huán)中保留變量的狀態(tài)。但與傳統(tǒng)寄存器不同的是,移位寄存器可以

2024-01-05 13:49:33 438

438 移位寄存器是一種用于在數(shù)字電路中實現(xiàn)數(shù)據(jù)移位操作的基本電路元件。它由多個觸發(fā)器以及相關(guān)控制電路組成,具有存儲、接受和移動數(shù)據(jù)的功能。移位寄存器可以分為兩種類型:串行移位寄存器和并行移位寄存器。 串行

2024-01-18 10:52:45 639

639

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

15788

15788

27

27 0

0 19

19 72

72 59

59 8922

8922

1740

1740

1625

1625 44087

44087 22

22 14

14 162375

162375 46606

46606

82198

82198

46140

46140

19126

19126 79693

79693

6033

6033

3

3 10761

10761

71381

71381

14507

14507

30504

30504

41305

41305

20

20 10

10 28404

28404

3314

3314 50448

50448 2

2 22

22 3

3 2789

2789 2983

2983 0

0 0

0 0

0 0

0 0

0 4416

4416

757

757

1548

1548 2473

2473

438

438 639

639

評論