實(shí)現(xiàn)一個(gè)4bit的移位寄存器如下,不帶復(fù)位

module shift_reg(

input clk,

input rst,

input din,

output dout

);

reg [ 3:0] buff;

assign dout = buff[3];

always@(posedge clk) begin buff[3:0]

endmodule

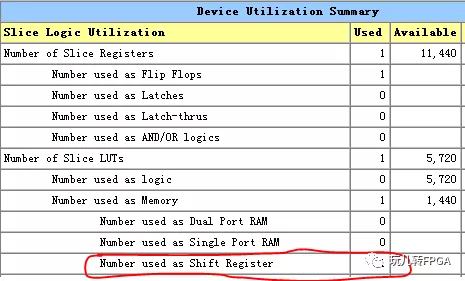

下圖是ISE14.7實(shí)現(xiàn)后的結(jié)果如下圖所示,編譯器直接把他綜合進(jìn)了一個(gè)SRL16里面,也就是專用的移位寄存器模塊,只需要一個(gè)LUT就可以實(shí)現(xiàn)16bit以內(nèi)的移位

這是不帶復(fù)位的資源,可以看到觸發(fā)器只用了一個(gè),LUT也只用了一個(gè),并且是作為存儲(chǔ)器用的,而且是作為存儲(chǔ)器里面的移位寄存器使用。

下面是帶有復(fù)位的移位寄存器代碼

module shift_reg(

input clk,

input rst,

input din,

output dout

);

reg [ 3:0] buff;

assign dout = buff[3];

always@(posedge clk)

begin

if(rst==1) buff

end

endmodule

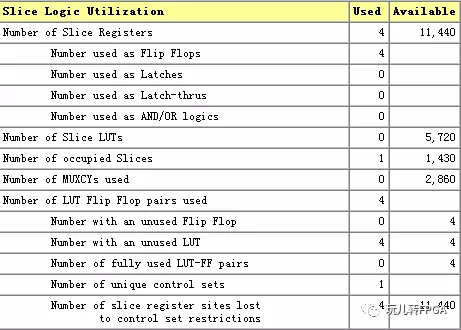

ISE14.7綜合結(jié)果如下:

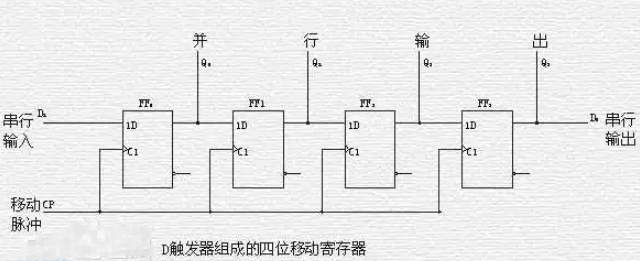

從上圖可以看出,他是用了4個(gè)觸發(fā)器級(jí)聯(lián)構(gòu)成,并且每個(gè)觸發(fā)器的復(fù)位端都是接了rst端的。

下圖是資源消耗,看的出來(lái)用了4個(gè)觸發(fā)器和0個(gè)LUT:

綜上:移位時(shí)間越長(zhǎng)用沒(méi)有復(fù)位的方式越節(jié)約資源。

那么,對(duì)于寄存器初始狀態(tài)沒(méi)有復(fù)位怎么設(shè)置他呢?

verilog2001的標(biāo)準(zhǔn)已經(jīng)解決,ISE14.7和vivado也都支持

比如, reg [ 3:0] buff = 0;就是上電后寄存器buff為全0

而 reg [ 3:0] buff = 8'hff;就是上電后寄存器buff的值為全1

編輯:hfy

-

移位寄存器

+關(guān)注

關(guān)注

3文章

286瀏覽量

22628 -

復(fù)位電路

+關(guān)注

關(guān)注

13文章

325瀏覽量

45082

發(fā)布評(píng)論請(qǐng)先 登錄

74VHC595;74VHCT595移位寄存器規(guī)格書

74HC165;74HCT165移位寄存器規(guī)格書

74HC594;74HCT594移位寄存器規(guī)格書

74LV595移位寄存器規(guī)格書

74HC595;74HCT595移位寄存器規(guī)格書

XILINX FPGA CLB單元之移位寄存器

移位寄存器的工作原理和類型

移位寄存器的工作原理、類型及應(yīng)用

移位寄存器中使用的儲(chǔ)存單元是什么

移位寄存器中Dsr有什么用

移位寄存器右移是怎么移位的

PLC移位寄存器指令的工作過(guò)程

8位移位寄存器工作原理是什么?

SN74HCS16507-Q1移位寄存器數(shù)據(jù)表

4bit的移位寄存器復(fù)位與不復(fù)位的實(shí)現(xiàn)

4bit的移位寄存器復(fù)位與不復(fù)位的實(shí)現(xiàn)

評(píng)論