能夠存儲1位二值信號的基本單元電路統(tǒng)稱為觸發(fā)器(Filp-Flop)

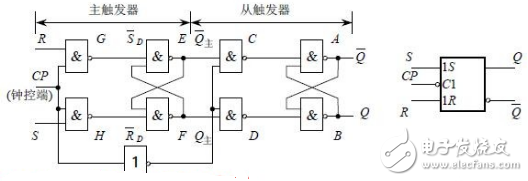

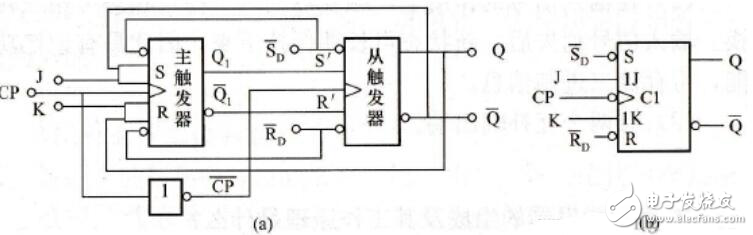

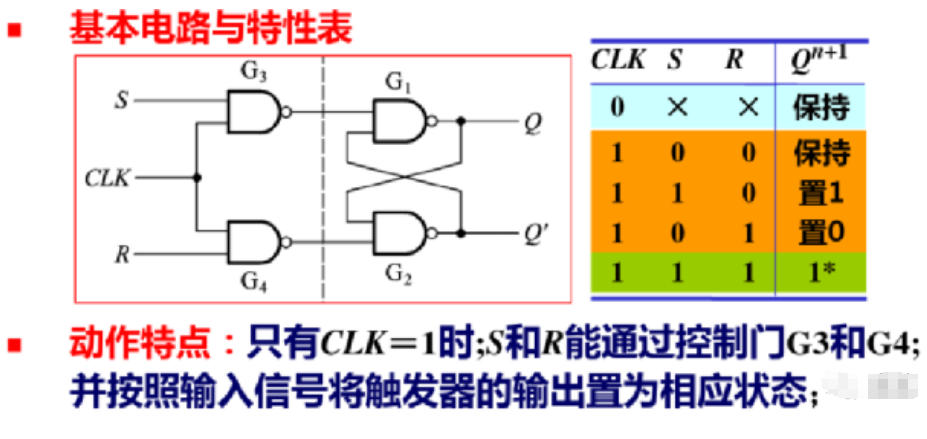

觸發(fā)器是構(gòu)成時序邏輯電路的基本邏輯部件。它有兩個穩(wěn)定狀態(tài):“0”和“1”。在不同的輸入情況下,它可以被置0狀態(tài)或1狀態(tài),當(dāng)輸入信號消失后,所置成的狀態(tài)能夠保持不變。所以觸發(fā)器可以記憶1位二值的信號。根據(jù)邏輯功能的不同,觸發(fā)器可以分為SR觸發(fā)器、D觸發(fā)器、JK觸發(fā)器、T和T‘觸發(fā)器。按照結(jié)構(gòu)形式的不同,又可分基本SR觸發(fā)器、同步觸發(fā)器、主從觸發(fā)器和邊沿觸發(fā)器。

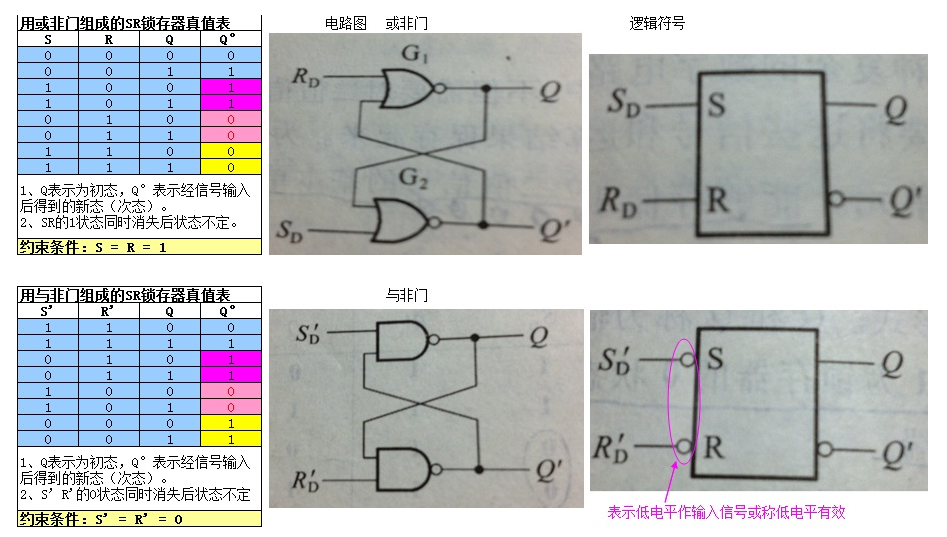

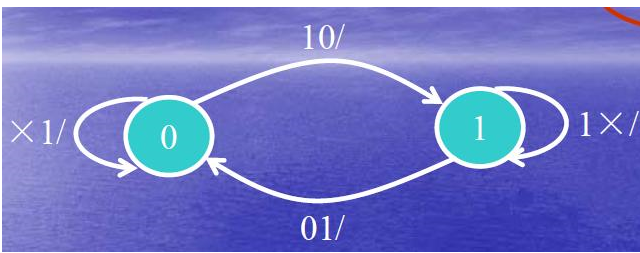

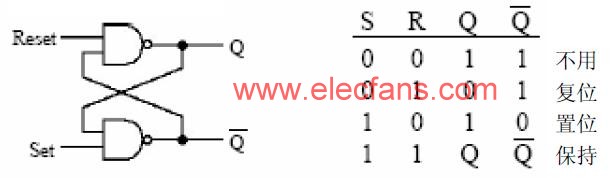

其狀態(tài)圖:

a、當(dāng)觸發(fā)器處在0狀態(tài),即Q = 0,若S’R‘ = 10或11時,觸發(fā)器仍為0狀態(tài)。若S’R‘ = 01,觸發(fā)器翻轉(zhuǎn)成為1狀態(tài)。

b、當(dāng)觸發(fā)器處在1狀態(tài),即Q = 1,若S’R‘ = 01或11時,觸發(fā)器仍為1狀態(tài)。若S’R‘ = 10,觸發(fā)器翻轉(zhuǎn)成為0狀態(tài)。

約束條件是S’R’不能同時為0。

D觸發(fā)器如何轉(zhuǎn)為為SR型,JK型和T型?

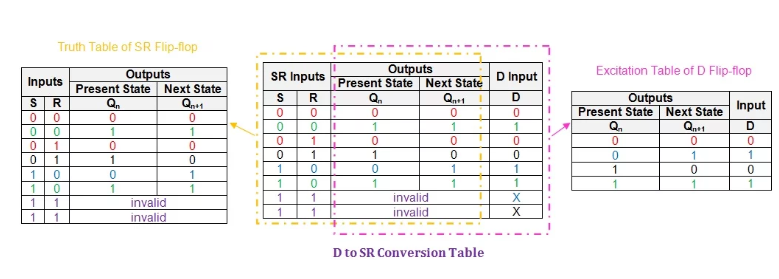

將D轉(zhuǎn)換為SR觸發(fā)器

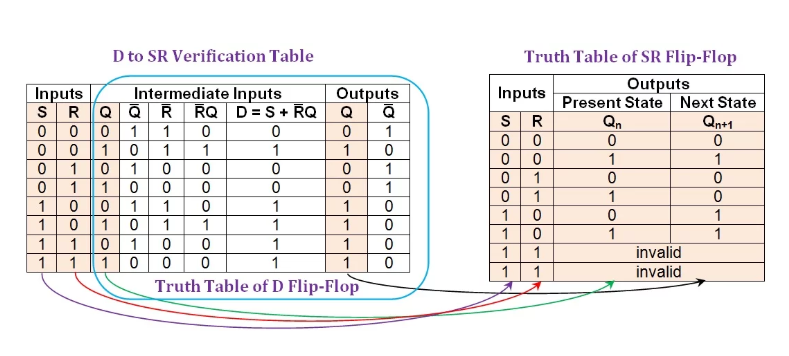

將給定D觸發(fā)器轉(zhuǎn)換為SR型的過程通過獲得表來啟動,該表表示存在于SR觸發(fā)器的真值表中的信息以及由D的激勵表傳達(dá)的信息。拖鞋。這樣的表稱為D-to-SR轉(zhuǎn)換表,如圖1所示。

圖1: D-to-SR轉(zhuǎn)換表。

這里我們注意到轉(zhuǎn)換表的最后兩行在“D Input”列中有X(Do not Cares)。這是因為使用SR觸發(fā)器時,S = R = 1的輸入組合無效(因為輸出將是不可預(yù)測的)。

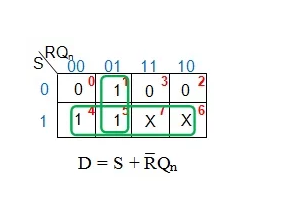

我們的下一步是根據(jù)所需觸發(fā)器S和R的輸入以及當(dāng)前狀態(tài)Q n獲得給定D觸發(fā)器輸入的邏輯表達(dá)式。但是,在這樣做時,我們需要使用合適的簡化技術(shù)(例如K-map ICfans)盡可能地簡化布爾表達(dá)式。這里詳細(xì)介紹了卡諾的方法。

圖2: D輸入的K-map簡化

從圖2中,對于d輸入的簡化的邏輯表達(dá)式被發(fā)現(xiàn)是S + RQ ?。這意味著,為了使給定的D觸發(fā)器表現(xiàn)得像所需的SR觸發(fā)器,我們需要AND Q n否定用戶定義的輸入R然后將結(jié)果與用戶定義的輸入進(jìn)行或運(yùn)算S.

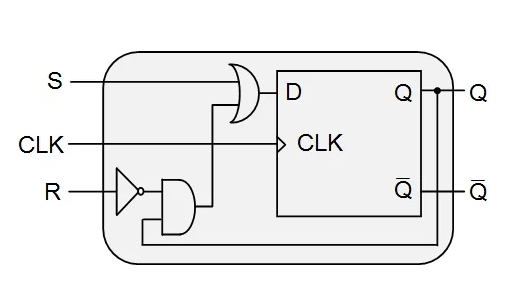

因此,所需的附加組合電路將是一個NOT門,一個AND門和一個OR門。使用這些組件設(shè)計的最終系統(tǒng)如圖3所示。

圖3: D觸發(fā)器表現(xiàn)為SR觸發(fā)器

完成轉(zhuǎn)換過程后,我們需要繼續(xù)進(jìn)行驗證過程。在這里,我們需要為設(shè)計的系統(tǒng)編寫真值表,并將其條目與SR(所需)觸發(fā)器的真值表中的條目進(jìn)行比較。

圖4: D-to-SR驗證表與SR觸發(fā)器的真值表之間的比較。

該圖顯示D-to-SR驗證表的第一,第二,第三和第八列(以米色陰影顯示)中的所有條目與SR觸發(fā)器的真值表中存在的條目一致。最后兩行看起來有所不同,但它們可以被認(rèn)為是等效的,因為SR觸發(fā)器的輸出可能由于無效輸入組合而為高或低。實際上,我們設(shè)計了一個比SR觸發(fā)器更好的系統(tǒng),因為當(dāng)兩個輸入都很高時它具有可預(yù)測的輸出行為。

驗證表表明轉(zhuǎn)換過程是成功的:給定的D觸發(fā)器在功能上等效于所需的SR觸發(fā)器。

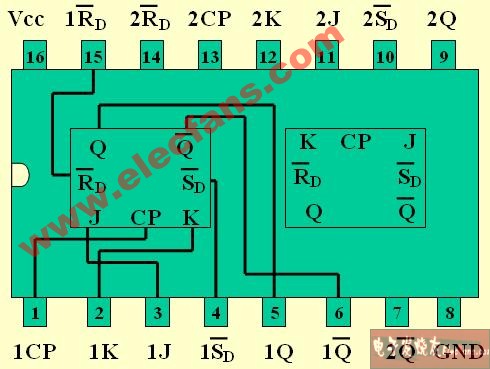

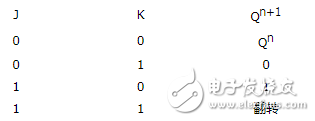

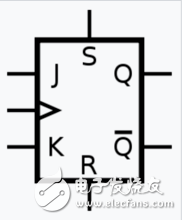

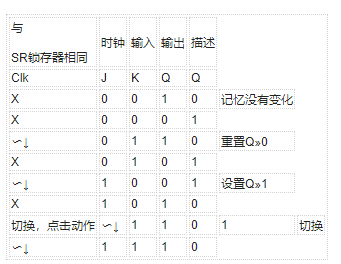

將D轉(zhuǎn)換為JK觸發(fā)器

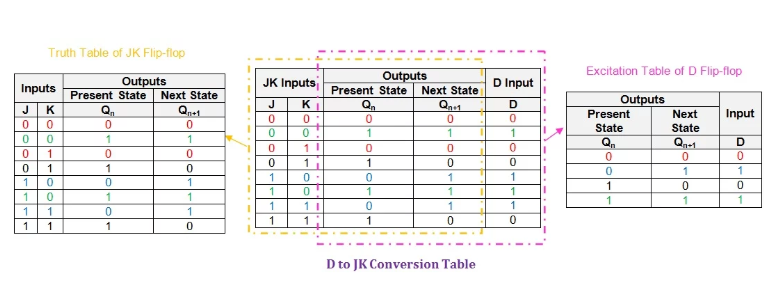

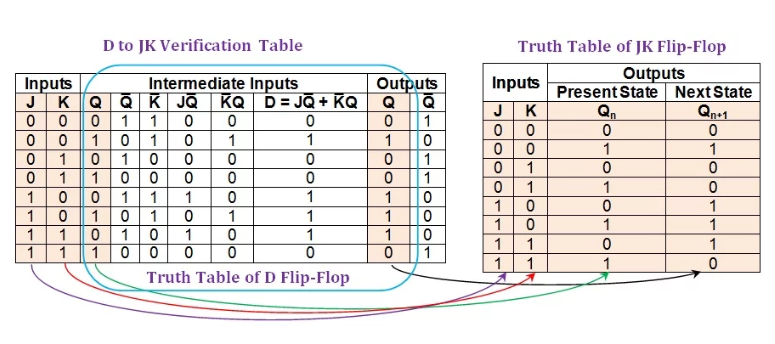

通過使用D-to-JK轉(zhuǎn)換表,可以將給定的D觸發(fā)器轉(zhuǎn)換為JK觸發(fā)器,如圖5所示。該表共同表示JK觸發(fā)器的真值表和D觸發(fā)器的激勵表。

圖5: D-to-JK轉(zhuǎn)換表。

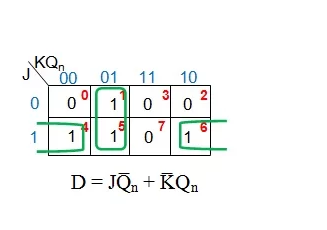

在此之后,我們需要根據(jù)J,K和Q n簡化D輸入的表達(dá)式。我們將再次采用K-map技術(shù)。

圖6:根據(jù)J,K和Q n對D輸入進(jìn)行K-map簡化

圖6顯示,為了將D觸發(fā)器轉(zhuǎn)換為JK觸發(fā)器,其D輸入需要由雙輸入OR門的輸出驅(qū)動,其輸入為

?相與本-狀態(tài)Q的否定?(即Q ?)

K(K?)的否定與當(dāng)前狀態(tài)Q n相關(guān)

這表明我們需要

一個NOT門 - 否定K.

兩個與門,一個獲得JQ ?和其他獲得KQ ?

一個或門,以獲得由JQ給出的d輸入? + KQ ?

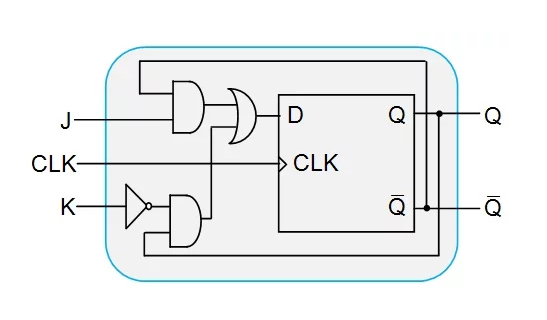

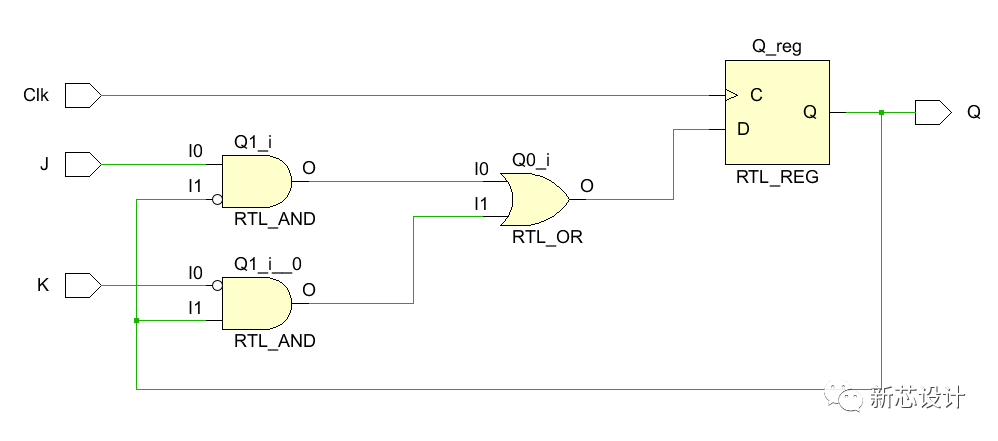

因此,得到的系統(tǒng)如圖7所示。

圖7: 設(shè)計用作JK觸發(fā)器的D觸發(fā)器

最后,讓我們驗證我們設(shè)計的系統(tǒng)是否像我們期望的那樣使用D-to-JK驗證表,如圖8所示。

圖8: D-to-JK驗證表與JK觸發(fā)器的真值表之間的比較。

圖8顯示D-to-JK驗證表的第一,第二,第三和第九列(以米色陰影顯示)具有與JK觸發(fā)器真值表的列中的條目相同的條目。這表明給定的D觸發(fā)器對于每個輸入組合和當(dāng)前狀態(tài)的行為與JK觸發(fā)器完全相同。

因此,我們可以得出結(jié)論,轉(zhuǎn)換過程是成功的。

D轉(zhuǎn)換為T觸發(fā)器

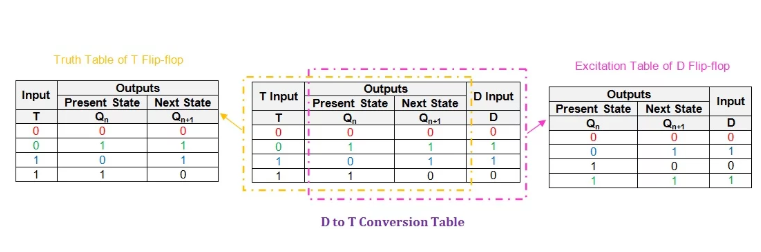

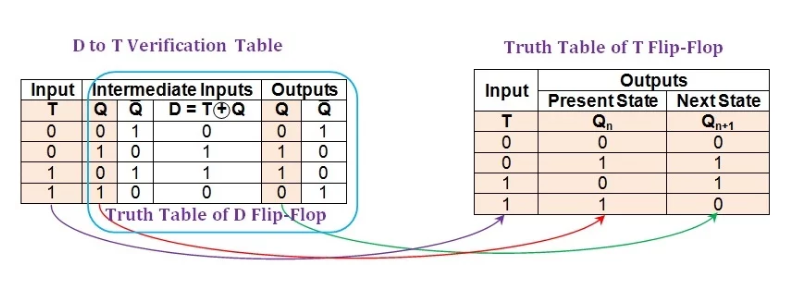

為了將給定的D觸發(fā)器轉(zhuǎn)換為T型,我們需要獲得相應(yīng)的轉(zhuǎn)換表,如圖9所示。這里,D觸發(fā)器的激勵表中的信息作為一部分插入T觸發(fā)器的真值表。

圖9: D-to-T轉(zhuǎn)換表。

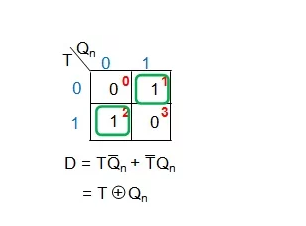

在獲得的轉(zhuǎn)換表,接下來的步驟是表達(dá)輸入,d,在T和Q的術(shù)語?。

圖10: D的K-map簡化,以T和Q n表示

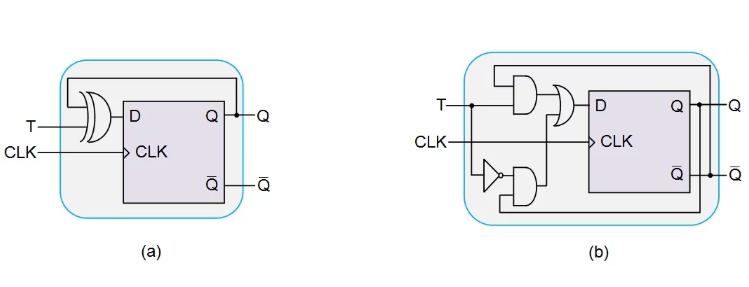

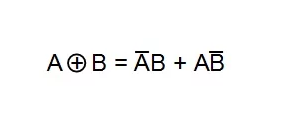

從圖10中可以看出,為了將給定的D觸發(fā)器轉(zhuǎn)換為T型,我們需要通過輸入為T和Q n的XOR門的輸出驅(qū)動其輸入引腳(D)。這將導(dǎo)致新的數(shù)字系統(tǒng)如圖11(a)所示(半導(dǎo)體社區(qū))。

如果我們必須將自己僅限于NOT,OR和AND門,我們將需要遵循以下步驟:

使用AND門來AND用戶定義的輸入T,以及觸發(fā)器當(dāng)前狀態(tài)Q n的否定。

使用另一個AND門來觸發(fā)觸發(fā)器的當(dāng)前狀態(tài),并取消T(作為NOT門的輸出獲得)。

或者使用雙輸入“或”門將兩個AND門的輸出連接在一起。

這導(dǎo)致了圖11(b)所示的數(shù)字系統(tǒng)。

圖11:設(shè)計為使用(a)XOR門和(b)僅NOT,OR和AND門的T觸發(fā)器的D觸發(fā)器。

下一步也是最后一步是使用D-to-T驗證表驗證轉(zhuǎn)換過程,如圖12所示。

圖12: D-to-T驗證表與T觸發(fā)器的真值表之間的比較。

從圖中可以看出,D-to-T驗證表的第一,第二和倒數(shù)第二列(以米色為陰影)與T觸發(fā)器的真值表中的列相同。這表明轉(zhuǎn)換過程成功,即給定的D觸發(fā)器的行為與T觸發(fā)器完全相同。

雖然我們已經(jīng)驗證了圖11(a)中設(shè)計的系統(tǒng),但結(jié)論對于圖11(b)所示的設(shè)計也是有效的,因為

電子發(fā)燒友App

電子發(fā)燒友App

評論