完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺。

這部分,還是和上例中一樣,不同的是額外添加了一個(gè)font_row參數(shù),因?yàn)楸纠惺褂玫淖址际切枰獡Q行的,所以需要添加這個(gè)參數(shù)。...

大部分運(yùn)算可以通過擴(kuò)位和近似的方式轉(zhuǎn)換為定點(diǎn)運(yùn)算。但有些算法在設(shè)計(jì)在設(shè)計(jì)的過程中就涉及大量的浮點(diǎn)運(yùn)算,在轉(zhuǎn)換為定點(diǎn)運(yùn)算時(shí)比較麻煩,會帶來龐大的工作量。...

Vivado的FFT IP核支持多通道輸入(Number of Channels)和實(shí)時(shí)更改FFT的點(diǎn)數(shù)(Run Time Configurable Transform Length)。...

??set_input_delay屬于時(shí)序約束中的IO約束,我之前的時(shí)序約束教程中,有一篇關(guān)于set_input_delay的文章,但里面寫的并不是很詳細(xì),今天我們就來詳細(xì)分析一下,這個(gè)約束應(yīng)該如何使用。...

Optional一欄表示該引腳是否可選擇例化,No表示必須對該引腳進(jìn)行例化,Yes表示該引腳可以選擇不例化。一般進(jìn)行例化時(shí)只對必須要進(jìn)行例化的引腳進(jìn)行操作...

數(shù)據(jù)傳輸態(tài):數(shù)據(jù)傳輸態(tài),又可以分為讀和寫兩個(gè)部分,過程都是一樣的,就合在一起了,都是在SCL為低電平的時(shí)候,SDA將數(shù)據(jù)發(fā)送,在SCL為高電平的時(shí)候,將數(shù)據(jù)接收。...

NBTI是指在較高溫度和負(fù)偏壓下,pMOS界面處的Si-H鍵斷裂產(chǎn)生界面陷阱,柵氧化層陷阱也會俘獲空穴,這些都會引起pMOS閾值電壓漂移,導(dǎo)致電路因時(shí)序無法滿足而出現(xiàn)功能錯(cuò)誤。...

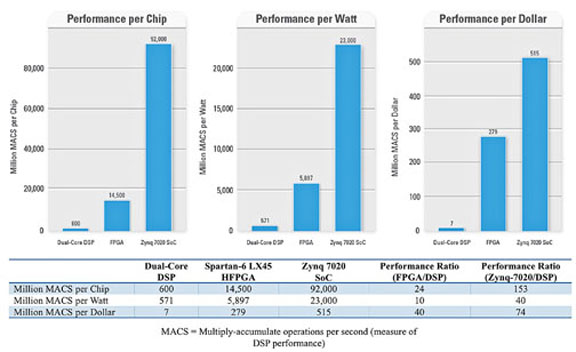

在數(shù)字信號處理領(lǐng)域 FPGA 同樣所向披靡,主要是因?yàn)樗母咚俨⑿刑幚砟芰ΑPGA最大優(yōu)勢是其并行處理機(jī)制,即利用并行架構(gòu)實(shí)現(xiàn)數(shù)字信號處理的功能。...

很多粉絲問我,嵌入式方向中的FPGA怎么樣?收入如何? 前言 講述FPGA前,我們先講講當(dāng)年中興被制裁的問題。 美國前總統(tǒng)特朗普曾經(jīng)發(fā)布過一條禁令,由于中興違反了美國的某個(gè)條例,禁止美國已經(jīng)國外任何一家公司向中興銷售FPGA芯片。 這個(gè)時(shí)候,一定會有抬杠青年說,我見過國內(nèi)生產(chǎn)的FPGA芯片,還用過呢...

隨著集成電路工藝進(jìn)入納米尺度,集成電路制造面臨日益嚴(yán)重的挑戰(zhàn)。例如,采用193nm波長光源的亞波長光刻導(dǎo)致硅片圖形嚴(yán)重畸變,化學(xué)機(jī)械拋光工藝導(dǎo)致互連線在高度方向發(fā)生嚴(yán)重偏差,工藝擾動(dòng)的影響日益嚴(yán)重等。...

參數(shù)傳遞經(jīng)常用于頂層的參數(shù)傳遞給子模塊,這樣我們只需要關(guān)注頂層實(shí)體的內(nèi)容,把子模塊的內(nèi)容當(dāng)做一個(gè)黑箱子即可,這也是非常實(shí)用的。...

這種方法還可以更好地與團(tuán)隊(duì)方法一起使用,并且可以創(chuàng)建可跨多個(gè)項(xiàng)目使用的加速內(nèi)核庫(IP)。另一個(gè)優(yōu)點(diǎn)是應(yīng)用于可編程邏輯實(shí)現(xiàn)的優(yōu)化駐留在 .xo 文件中,無需在每次使用算法時(shí)重新進(jìn)行優(yōu)化。...

對于fifo來說,H的設(shè)置至關(guān)重要。既要保證功能性,不溢出丟數(shù),也要保證性能流水。深度設(shè)置過小會影響功能,過大又浪費(fèi)資源。因此,總結(jié)下fifo設(shè)計(jì)中深度H的計(jì)算。...

版圖驗(yàn)證工具不僅要支持扁平化驗(yàn)證,而且要支持層次化驗(yàn)證。扁平化驗(yàn)證是版圖驗(yàn)證工具的基礎(chǔ);層次化驗(yàn)證充分利用版圖層次,可以有效避免重復(fù)報(bào)錯(cuò)和提高處理版圖的速度。對于大規(guī)模版圖,通常還采用并行技術(shù)以加速版圖驗(yàn)證效率。...

在做FPGA的開發(fā)過程中經(jīng)常會使用到移位寄存器,一般我們使用移位寄存器的目的都是為了將某個(gè)信號進(jìn)行打拍,使得時(shí)序符合我們的需求。...

其中有的CRC寄存器初始值設(shè)置為全1,如以太網(wǎng)的CRC32,目的就是為了能檢測出數(shù)據(jù)前面的0的個(gè)數(shù)。1234算出來的CRC,跟01234算出來的,不一樣,這就能應(yīng)對前面帶0的數(shù)據(jù)了。...

只有在腦海中建立了一個(gè)個(gè)邏輯模型,理解FPGA內(nèi)部邏輯結(jié)構(gòu)實(shí)現(xiàn)的基礎(chǔ),才能明白為什么寫Verilog和寫C整體思路是不一樣的,才能理解順序執(zhí)行語言和并行執(zhí)行語言的設(shè)計(jì)方法上的差異。在看到一段簡單程序的時(shí)候應(yīng)該想到是什么樣的功能電路。...

AXI IIC 和 PS IIC 控制器都符合 NXP IIC 總線規(guī)范。用戶必須確保其選擇使用的從設(shè)備的時(shí)序參數(shù)與UM10204 的第 48 頁上的“表 10”中的參數(shù)相同。...

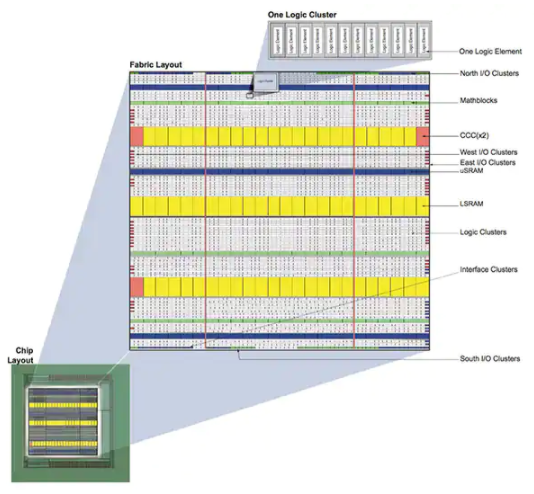

該入門套件包含一個(gè)系統(tǒng)級模塊 (SOM),其中包含帶有相關(guān)存儲器和時(shí)鐘的 Microsemi SmartFusion2 FPGA SoC 器件,以及一個(gè)承載原型設(shè)計(jì)區(qū)域、電源轉(zhuǎn)換器和電源管理 IC 的 SmartFusion2 基板,該入門套件提供了一個(gè)完整的平臺開始您的第一個(gè)設(shè)計(jì)。...

自從商業(yè)上可行的 FPGA 出現(xiàn)以來,嵌入式設(shè)計(jì)人員就已經(jīng)實(shí)現(xiàn)了異構(gòu)架構(gòu)。最初,F(xiàn)PGA 主要用作處理系統(tǒng)、外設(shè)和 I/O 之間接口的粘合邏輯。但隨著 FPGA 技術(shù)的改進(jìn),市場擴(kuò)大到在嵌入式系統(tǒng)中發(fā)揮更大和更核心的作用。異構(gòu)計(jì)算的最新趨勢是將處理器和 FPGA 子系統(tǒng)集成到單個(gè) SoC 中。以處理...